文獻(xiàn)標(biāo)識(shí)碼: A

文章編號(hào): 0258-7998(2015)02-0075-03

0 引言

近年來,隨著航空、航天、測(cè)控等技術(shù)的迅速發(fā)展,相關(guān)行業(yè)對(duì)數(shù)據(jù)采集系統(tǒng)的性能要求更加苛刻,要求能夠同時(shí)采樣的通道更多,采樣的精度和速度要求更高,因此研制開發(fā)了一套高性能數(shù)據(jù)采集系統(tǒng)。該系統(tǒng)較以往開發(fā)的數(shù)據(jù)采集系統(tǒng),在設(shè)計(jì)方案、操作界面等方面均有了較大改進(jìn),如該系統(tǒng)采用PCI總線,傳輸速率得以大大提高,系統(tǒng)軟件運(yùn)行于Windows操作系統(tǒng)下,較以往該領(lǐng)域的Dos系統(tǒng),在操作上更方便,界面更友好。整個(gè)系統(tǒng)具有高精度、高采樣速率以及多通道且通道數(shù)可變的突出特點(diǎn),本文介紹了該數(shù)據(jù)采集系統(tǒng)的設(shè)計(jì)與研制方案。

1 系統(tǒng)的總體設(shè)計(jì)方案

系統(tǒng)具體工作要求:有62路通道可以供用戶采集轉(zhuǎn)換使用,具體采集1~62路中的任意多個(gè)通道及這些通道的編號(hào)分別是多少等信息由用戶根據(jù)需要通過上位機(jī)傳送給本系統(tǒng),即本系統(tǒng)要根據(jù)上位機(jī)的具體信息完成用戶的任務(wù);另外為了達(dá)到相關(guān)指標(biāo)的要求,A/D分辨率應(yīng)達(dá)到14位。從要求可以看出本系統(tǒng)具有采集路數(shù)和路號(hào)可變、精度高、速度快的突出特點(diǎn)。針對(duì)這些特點(diǎn),選用凌華公司的數(shù)據(jù)采集卡(DAQ-2010)作為采集和A/D轉(zhuǎn)換器件,該板卡具有4個(gè)14位精度的同步A/D通道,通過擴(kuò)展可以滿足62通道的要求。另外,該板卡的4個(gè)獨(dú)立A/D的轉(zhuǎn)換速率可達(dá)2.2 Mb/s,滿足了高速采集的技術(shù)要求。作為該板卡工作的控制器,選擇使用CPLD,因?yàn)镃PLD具有精度高、速度快、穩(wěn)定性好的特點(diǎn),從而可以滿足需要。本系統(tǒng)與上位機(jī)的通信和控制器選擇的是8051核單片機(jī),其開發(fā)技術(shù)成熟,性能完全可以滿足需求,并且價(jià)格低廉,可以很好地控制成本,它們的具體連接框圖如圖1所示。

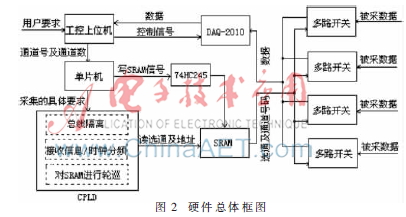

系統(tǒng)工作時(shí),首先由用戶將要選通的具體通道編號(hào)和通道數(shù)目通過工控機(jī)傳遞給單片機(jī),單片機(jī)將各通道編號(hào)作為數(shù)據(jù)存放于SRAM中,并且將具體的采樣要求,諸如采樣頻率、采樣總通道數(shù)等信息傳給CPLD。而后CPLD獨(dú)立輸出SRAM的地址來輪巡所要采集的通道。每當(dāng)一個(gè)通道開通,傳感器和電壓端子盒將被測(cè)系統(tǒng)的電流信號(hào)或電壓信號(hào)匯集到信號(hào)控制箱,然后進(jìn)入信號(hào)調(diào)理板和信號(hào)轉(zhuǎn)換電路,將被測(cè)信號(hào)轉(zhuǎn)換為標(biāo)準(zhǔn)測(cè)量電平后,通過轉(zhuǎn)接適配器進(jìn)入數(shù)據(jù)采集卡,DAQ-2010數(shù)據(jù)采集卡就采集轉(zhuǎn)換一次,并將轉(zhuǎn)換后的數(shù)據(jù)傳回給上位工控機(jī)。工控機(jī)對(duì)電壓、電流、功率、相位等信號(hào)參數(shù)進(jìn)行數(shù)據(jù)分析、計(jì)算、顯示和存儲(chǔ),并套用相關(guān)標(biāo)準(zhǔn)限制曲線圖形,使標(biāo)準(zhǔn)規(guī)定的極限曲線與試驗(yàn)數(shù)據(jù)填充曲線進(jìn)行對(duì)比,以此評(píng)估被測(cè)試系統(tǒng)設(shè)計(jì)的精度和誤差,從而實(shí)現(xiàn)對(duì)被測(cè)系統(tǒng)的實(shí)時(shí)監(jiān)控。

2 系統(tǒng)的硬件設(shè)計(jì)

系統(tǒng)硬件的設(shè)計(jì)主要是圍繞DAQ-2010數(shù)據(jù)采集卡進(jìn)行的,諸如將數(shù)據(jù)采集卡的4個(gè)同步采樣通道擴(kuò)展為62通道,利用硬件描述語言開發(fā)CPLD,使其能夠完成對(duì)62通道的輪巡以及總線隔離等功能。針對(duì)系統(tǒng)各通道要采集的電壓、電流信號(hào)的不同,采用多種電壓、電流傳感器將原始信號(hào)轉(zhuǎn)換成數(shù)據(jù)采集卡可以采集的統(tǒng)一形式的電信號(hào),這樣就可以為數(shù)據(jù)采集、信號(hào)處理打下有利的基礎(chǔ)。硬件總體框圖如圖2所示。

2.1 通道擴(kuò)展的實(shí)現(xiàn)

如前所述,本系統(tǒng)設(shè)計(jì)需要62個(gè)通道供用戶使用,但DAQ-2010僅有4個(gè)獨(dú)立同步A/D通道,于是采用4個(gè)16通道多路開關(guān)進(jìn)行擴(kuò)展,從而可以構(gòu)造出64個(gè)通道可供使用,既滿足了用戶的要求,又可以留有兩個(gè)通道作為應(yīng)急或系統(tǒng)升級(jí)使用。

2.2 通道輪巡的實(shí)現(xiàn)

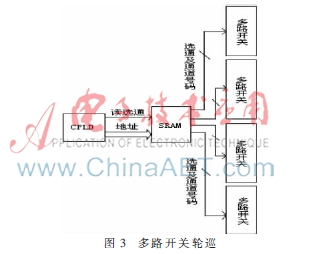

將通道擴(kuò)展至62之后,如何選通通道這一任務(wù)的完成是通過對(duì)SRAM的數(shù)據(jù)進(jìn)行讀取實(shí)現(xiàn)的。具體思想是在系統(tǒng)開始工作時(shí),用戶根據(jù)自己的需求將需要測(cè)試的通道編號(hào)通過工控機(jī)傳遞給單片機(jī),而后由單片機(jī)將通道編號(hào)作為數(shù)據(jù)寫入靜態(tài)存儲(chǔ)器SRAM中,開始進(jìn)行數(shù)據(jù)采集時(shí),CPLD在內(nèi)部時(shí)鐘的控制下讀取SRAM中的數(shù)據(jù)(即通道編號(hào)),這些編號(hào)就成為了多路開關(guān)的選通信號(hào),隨即實(shí)現(xiàn)了相應(yīng)多路開關(guān)通道的開通,這樣就完成了對(duì)所需通道的輪巡,其實(shí)現(xiàn)框圖如圖3所示。

2.3 CPLD程序設(shè)計(jì)

CPLD程序設(shè)計(jì)的任務(wù)是:

(1)接收單片機(jī)對(duì)系統(tǒng)工作要求的信息:如用戶需要輪巡的通道數(shù)、分頻數(shù)、復(fù)位信號(hào)等。

(2)對(duì)多路開關(guān)進(jìn)行輪巡時(shí),自動(dòng)產(chǎn)生所要讀取SRAM的選通信號(hào)以及它的地址信號(hào),并根據(jù)時(shí)序要求實(shí)現(xiàn)輪巡。

(3)接收系統(tǒng)工作時(shí)鐘,并且根據(jù)要求實(shí)現(xiàn)對(duì)系統(tǒng)時(shí)鐘的分頻。

另外值的一提的是,系統(tǒng)在工作時(shí)分為單片機(jī)向SRAM寫數(shù)據(jù)并驗(yàn)證和CPLD讀取SRAM中的數(shù)據(jù)兩個(gè)步驟,而從單片機(jī)和CPLD引出的SRAM選通、讀取、地址等控制或數(shù)據(jù)線都要與SRAM連接,這樣就需要有隔離措施,使得在前一個(gè)步驟時(shí),CPLD與SRAM間是高阻態(tài),而當(dāng)?shù)诙€(gè)步驟時(shí),單片機(jī)與SRAM間處于高阻態(tài)。由于在硬件方面,為了控制PCB板的規(guī)格,所以CPLD與SRAM間的隔離需要編程實(shí)現(xiàn)。

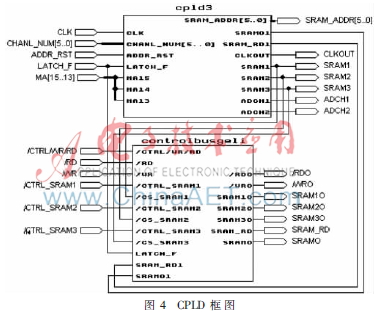

系統(tǒng)中最重要的時(shí)序是CPLD的工作時(shí)序,CPLD能否正常工作是整個(gè)系統(tǒng)的關(guān)鍵,要保證CPLD的工作時(shí)序清晰,不會(huì)產(chǎn)生混亂。CPLD選用EPM7128,使用Verilog HDL語言在MAX+PLUSⅡ環(huán)境下進(jìn)行開發(fā), CPLD的頂層程序設(shè)計(jì)模塊見圖4。框圖左側(cè)均為CPLD的輸入管腳,包括時(shí)鐘、控制讀、寫選通等信號(hào),框圖右側(cè)均為CPLD的輸出管腳,包括對(duì)SRAM的讀信號(hào)和地址信號(hào),其中SRAM1O、SRAM2O、SRAM3O、SRAMO、SRAM_RD等信號(hào)可以在單片機(jī)寫SRAM時(shí)實(shí)現(xiàn)CPLD與SRAM的隔離。

正常工作時(shí),系統(tǒng)的時(shí)序圖如圖5所示。

3 測(cè)試系統(tǒng)的軟件設(shè)計(jì)

測(cè)試系統(tǒng)軟件使用VC++開發(fā),運(yùn)行于Windows環(huán)境下,人機(jī)界面友好,包括系統(tǒng)測(cè)試軟件和和系統(tǒng)校準(zhǔn)軟件。其中系統(tǒng)測(cè)試軟件是在對(duì)被測(cè)系統(tǒng)進(jìn)行測(cè)試時(shí),具體實(shí)現(xiàn)對(duì)電壓、電流、相位、功率、功率因數(shù)等參數(shù)的穩(wěn)態(tài)和瞬態(tài)進(jìn)行數(shù)據(jù)測(cè)試、數(shù)據(jù)分析和數(shù)據(jù)存儲(chǔ)的執(zhí)行軟件,系統(tǒng)校準(zhǔn)軟件是對(duì)系統(tǒng)的精度進(jìn)行計(jì)量的軟件。

該軟件包采用中文下拉菜單方式提示操作、顯示、打印,自動(dòng)記錄和存儲(chǔ)所有測(cè)試數(shù)據(jù),以便于事后調(diào)出查詢,觀察分析,重新顯示輸出。測(cè)試數(shù)據(jù)套用相關(guān)標(biāo)準(zhǔn)限制曲線圖形,標(biāo)準(zhǔn)規(guī)定的極限曲線與試驗(yàn)數(shù)據(jù)填充曲線的對(duì)比圖形可同時(shí)顯示打印,以便于判斷測(cè)試結(jié)果是否滿足設(shè)計(jì)要求。

4 結(jié)束語

本系統(tǒng)已經(jīng)投入實(shí)際應(yīng)用,經(jīng)過實(shí)踐證明這一系統(tǒng)完全滿足多通道同時(shí)采樣并且速度快、精度高的要求,穩(wěn)定可靠,取得了很好的效果,說明了文章中所作的分析和討論是合理和實(shí)用的。本系統(tǒng)可應(yīng)用于高速、多通道且通道路數(shù)可變的工程應(yīng)用領(lǐng)域。

參考文獻(xiàn)

[1] 王育堅(jiān).Visual c++面向?qū)ο缶幊探坛蘙M].北京:清華大學(xué)出版社,2003.

[2] 夏宇聞.Verilog 數(shù)字系統(tǒng)設(shè)計(jì)教程[M].北京:北京航空航天大學(xué)出版社,2003.

[3] 東方人華.MAX+PLUSⅡ入門與提高[M].北京:清華大學(xué)出版社,2004.

[4] 王金明,楊吉斌.數(shù)字系統(tǒng)設(shè)計(jì)與Verilog HDL[M].北京:電子工業(yè)出版社,2002.

[5] BHASKER J.Verilog HDL硬件描述語言[M].徐振林,譯.北京:機(jī)械工業(yè)出版社,2000.