魯佳琪,黃芝平,劉純武,劉德勝,陳實(shí)

(國防科學(xué)技術(shù)大學(xué) 機(jī)電工程與自動(dòng)化學(xué)院,湖南 長沙 410073)

摘要:網(wǎng)絡(luò)流量分類技術(shù)為網(wǎng)絡(luò)服務(wù)提供有力保障,在網(wǎng)絡(luò)行為分析和網(wǎng)絡(luò)監(jiān)管方面發(fā)揮重要作用。設(shè)計(jì)并實(shí)現(xiàn)了一種基于FPGA+TCAM架構(gòu)的網(wǎng)絡(luò)分流系統(tǒng),接入高速網(wǎng)絡(luò)信號(hào),恢復(fù)數(shù)據(jù)流信息,并對(duì)其進(jìn)行分流管理。解決了傳統(tǒng)網(wǎng)絡(luò)分流系統(tǒng)接入速率不高,分流效果差的問題。最后對(duì)系統(tǒng)平臺(tái)進(jìn)行了測試,測試結(jié)果表明,該系統(tǒng)具備在高速網(wǎng)絡(luò)環(huán)境下數(shù)據(jù)流實(shí)時(shí)分流處理的能力。

關(guān)鍵詞:網(wǎng)絡(luò)流量;分流;三態(tài)內(nèi)容可尋址寄存器;現(xiàn)場可編程門陣列

0引言

網(wǎng)絡(luò)流量分類技術(shù)是指將混合有各種應(yīng)用的流量,按其相關(guān)特性進(jìn)行分類的技術(shù)。網(wǎng)絡(luò)流量分類一直是學(xué)術(shù)界和產(chǎn)業(yè)界關(guān)注的重點(diǎn)之一。對(duì)學(xué)術(shù)界來說,網(wǎng)絡(luò)流量分類是高性能網(wǎng)絡(luò)協(xié)議和應(yīng)用設(shè)計(jì)的基礎(chǔ);對(duì)運(yùn)營商來說,網(wǎng)絡(luò)流量分類是網(wǎng)絡(luò)運(yùn)營管理、網(wǎng)絡(luò)發(fā)展規(guī)劃、網(wǎng)絡(luò)流量調(diào)度和高效能業(yè)務(wù)前瞻的依據(jù)[1] 。因此,進(jìn)行網(wǎng)絡(luò)流量分類相關(guān)領(lǐng)域的研究具有重要的理論和現(xiàn)實(shí)意義。但是,傳統(tǒng)分流設(shè)備由于不能適應(yīng)高速網(wǎng)絡(luò)環(huán)境,導(dǎo)致處理效率和準(zhǔn)確率不高。傳統(tǒng)設(shè)備的缺點(diǎn)一直制約著網(wǎng)絡(luò)流量分類技術(shù)研究的發(fā)展。因此,設(shè)計(jì)并實(shí)現(xiàn)高接入速率、高處理效率的分流系統(tǒng)迫在眉睫。

網(wǎng)絡(luò)流量分類技術(shù)分為軟件和硬件兩種主要實(shí)現(xiàn)方式。已有的軟件算法包括:(1)鍵樹結(jié)構(gòu)的分類算法:包括分層樹和擴(kuò)展樹兩種結(jié)構(gòu)。分層樹結(jié)構(gòu)查找時(shí)的回查操作導(dǎo)致其查找速度變慢;擴(kuò)展樹結(jié)構(gòu)又由于重復(fù)復(fù)制大量路徑致使算法的空間占用量很大。(2)計(jì)算幾何學(xué)點(diǎn)定位算法:利用這種思想演變而來的各種軟件算法也是目前相對(duì)較好的算法,如BV、HiCuts、RFC以及改進(jìn)型BV算法(如ABV、AFBV等)等。其利用不同的技術(shù)提高了網(wǎng)絡(luò)流量的處理速度,但是存在占用大量存儲(chǔ)空間的缺點(diǎn)[2]。

硬件算法主要以基于三態(tài)內(nèi)容可尋址寄存器(Ternary Content Addressable Memory,TCAM)的硬件算法為主。TCAM具有并行全相聯(lián)結(jié)構(gòu),一個(gè)時(shí)鐘周期就可以獲得匹配結(jié)果[3]。TCAM是由內(nèi)容可尋址寄存器(Content Addressable Memory,CAM)發(fā)展而來。TCAM相比CAM來說,每一個(gè)匹配位不僅可以存儲(chǔ)“0”或“1”,還可以存儲(chǔ)“X”來進(jìn)行模糊匹配,匹配范圍更加廣泛,匹配效率也更高。盡管TCAM也存在功耗高、存儲(chǔ)量小等缺點(diǎn),但是通過分頁TCAM可以降低TCAM的功耗[4],對(duì)TCAM匹配的規(guī)則集進(jìn)行語義等價(jià)變換可減少TCAM所需的資源[5],這些研究都彌補(bǔ)了TCAM器件的不足。

根據(jù)軟硬件算法的優(yōu)缺點(diǎn)對(duì)比,本文系統(tǒng)平臺(tái)采用TCAM作為數(shù)據(jù)匹配部分的關(guān)鍵器件。現(xiàn)場可編程門陣列(Field Programmable Gate Array,F(xiàn)PGA)具有并行處理的優(yōu)勢,且算法是在底層硬件上實(shí)現(xiàn),相比多核等處理器減少了程序在操作系統(tǒng)上的運(yùn)行時(shí)間,加快了處理速度。基于以上優(yōu)點(diǎn),本文采用FPGA作為整體架構(gòu)的核心處理器件。最終,設(shè)計(jì)并實(shí)現(xiàn)了基于FPGA+TCAM架構(gòu)的網(wǎng)絡(luò)分流系統(tǒng),解決了傳統(tǒng)技術(shù)接入速率低、匹配準(zhǔn)確性差的缺點(diǎn),實(shí)現(xiàn)了高速網(wǎng)絡(luò)信號(hào)快速準(zhǔn)確的分流過濾。

1系統(tǒng)硬件平臺(tái)設(shè)計(jì)

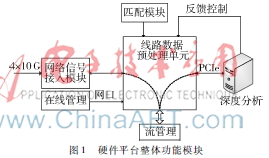

網(wǎng)絡(luò)流量分類系統(tǒng)的設(shè)計(jì)關(guān)鍵在于如何適應(yīng)高速網(wǎng)絡(luò)信號(hào)接入的高速率。其次,網(wǎng)絡(luò)中的信號(hào)是通過數(shù)據(jù)報(bào)文的形式進(jìn)行傳輸?shù)模瑢?duì)網(wǎng)絡(luò)信號(hào)進(jìn)行分類主要是在流的基礎(chǔ)上進(jìn)行,而流指的是在超時(shí)約束下,具有相同五元組(源IP,目的IP,源端口號(hào),目的端口號(hào),IP層協(xié)議號(hào))信息的一組報(bào)文的集合。如何進(jìn)行數(shù)據(jù)報(bào)文的流恢復(fù)和管理也是系統(tǒng)設(shè)計(jì)的關(guān)鍵之一。再次,互聯(lián)網(wǎng)新技術(shù)、新應(yīng)用層出不窮,網(wǎng)絡(luò)協(xié)議格式復(fù)雜,如何快速地實(shí)時(shí)更新匹配表項(xiàng)也是系統(tǒng)設(shè)計(jì)的難點(diǎn)之一。基于以上幾個(gè)難點(diǎn)將網(wǎng)絡(luò)分流系統(tǒng)具體分為以下幾個(gè)模塊:高速網(wǎng)絡(luò)接入模塊、數(shù)據(jù)預(yù)處理單元、流管理模塊、匹配模塊、在線管理和深度分析模塊。圖1是系統(tǒng)平臺(tái)的整體功能模塊劃分。

系統(tǒng)平臺(tái)通過高速信號(hào)接入模塊將骨干網(wǎng)的高速光纖信號(hào)接入系統(tǒng)平臺(tái),首先在預(yù)處理單元中對(duì)接入的數(shù)據(jù)進(jìn)行數(shù)據(jù)清洗、數(shù)據(jù)集成、數(shù)據(jù)變換等預(yù)處理操作[1] ,然后在流管理單元將分片的數(shù)據(jù)進(jìn)行流恢復(fù),獲得完整的流信息。之后將流送入匹配模塊進(jìn)行匹配條目的對(duì)比命中操作,最后將命中的結(jié)果送到后端服務(wù)器進(jìn)行更深層次的數(shù)據(jù)分析和處理。

1.1網(wǎng)絡(luò)信號(hào)接入模塊

當(dāng)前骨干網(wǎng)的傳輸速率普遍為10 Gb/s,設(shè)計(jì)的系統(tǒng)平臺(tái)要兼容10 Gb/s及以下的網(wǎng)絡(luò)信號(hào)速率。因此,該模塊采用集成化接口,將10 Gb/s的網(wǎng)絡(luò)數(shù)據(jù)接入平臺(tái)。系統(tǒng)設(shè)計(jì)有4路接入端口,接入速率高達(dá)40 Gb/s,可應(yīng)對(duì)包括10G POS(IP over SDH)、10GE、10G WAN等不同的網(wǎng)絡(luò)信號(hào)格式的收發(fā)處理。

1.2預(yù)處理單元

互聯(lián)網(wǎng)的數(shù)據(jù)規(guī)模異常龐大,單單一條10 Gb/s的鏈路,按全天平均30%的傳輸負(fù)荷,每秒產(chǎn)生的流量數(shù)據(jù)為375 MB,一天的流量就要超過32 TB。如此海量的數(shù)據(jù)對(duì)獲取、存儲(chǔ)、查詢和實(shí)時(shí)分析都增加了很大的難度。通過數(shù)據(jù)預(yù)處理可降低后續(xù)的分析規(guī)模,提高效率。

系統(tǒng)選用FPGA來完成預(yù)處理操作,其高速并行處理的特性非常適合系統(tǒng)預(yù)處理性能的需求。FPGA還要完成對(duì)其他模塊的配置和管理工作。系統(tǒng)設(shè)計(jì)包括高速緩存、管理網(wǎng)口、交互接口等多種不同格式的接口模塊,因此,系統(tǒng)選用Altera Stratix V系列FPGA芯片。該芯片擁有專用接口可以滿足PCIExpress總線和4路高速接口的接入能力,并且擁有足夠數(shù)量的管腳進(jìn)行其他模塊的管理操作。

通過編寫程序?qū)崿F(xiàn)數(shù)據(jù)報(bào)文的預(yù)處理以及對(duì)其他模塊的管理操作。其中包括數(shù)據(jù)報(bào)文恢復(fù)、提取五元組信息、剔除無關(guān)報(bào)文;對(duì)TCAM表項(xiàng)的更新、寄存器動(dòng)態(tài)配置以及對(duì)相應(yīng)操作的仲裁管理[6];對(duì)高速緩存的控制和輸入輸出調(diào)度;通過PCI Express接口與服務(wù)器通信完成數(shù)據(jù)流后續(xù)分發(fā)處理;通過管理網(wǎng)口對(duì)匹配規(guī)則進(jìn)行在線管理和更新。

1.3流管理模塊

數(shù)據(jù)流的完整性對(duì)于匹配操作的準(zhǔn)確性十分重要,在高速網(wǎng)絡(luò)中,數(shù)據(jù)是以分組形式傳輸,每個(gè)IP包內(nèi)儲(chǔ)存部分?jǐn)?shù)據(jù)。系統(tǒng)為了還原完整的數(shù)據(jù)內(nèi)容就需要進(jìn)行流管理,包括對(duì)數(shù)據(jù)的分片重組和報(bào)文亂序重組。流管理模塊緩存處理好的數(shù)據(jù)流,并建立流表。如果有新報(bào)文接入,就提取該報(bào)文的五元組信息,用該五元組信息對(duì)現(xiàn)有流表進(jìn)行HASH運(yùn)算,判斷該報(bào)文是否屬于原緩存中的數(shù)據(jù)流。如果找到對(duì)應(yīng)的流則將該報(bào)文添加到該流內(nèi);否則添加新流并更新流表。這些操作都要對(duì)數(shù)據(jù)進(jìn)行緩存處理。

從系統(tǒng)硬件設(shè)計(jì)的穩(wěn)定性方面考慮,接入速率最高為40 Gb/s,高速緩存的容量要滿足40 Gb/8=5 GB的存儲(chǔ)空間,而且?guī)捯惨^40 Gb/s。一般情況下緩存芯片位寬為64 bit,雙倍速率讀寫,可獲得模塊的最低頻率為40 Gb/s/(64×2)=480 MHz。因此,從存儲(chǔ)容量和最低帶寬來考慮,系統(tǒng)設(shè)計(jì)有兩組緩存模塊,頻率可達(dá)533 MHz,其位寬為64 bit,滿足最低頻率要求。單片緩存模塊的容量為4 GB,在內(nèi)存總量上,兩組緩存模塊的容量為8 GB,也遠(yuǎn)大于5 GB的內(nèi)存容量。根據(jù)理論分析,該設(shè)計(jì)完全滿足40 Gb/s速率網(wǎng)絡(luò)信號(hào)的緩存要求。

1.4匹配模塊

在完成數(shù)據(jù)流恢復(fù)以及預(yù)處理操作之后,將數(shù)據(jù)流送入匹配模塊根據(jù)表項(xiàng)進(jìn)行匹配操作。TCAM內(nèi)部可存儲(chǔ)匹配表項(xiàng),因此系統(tǒng)只要向TCAM輸入搜索的內(nèi)容,就會(huì)將此內(nèi)容與匹配的表項(xiàng)進(jìn)行比較,返回所需要的最優(yōu)項(xiàng),獲得要執(zhí)行的動(dòng)作命令地址,反饋到FPGA中。隨后FPGA就會(huì)根據(jù)得到的命令對(duì)匹配到的數(shù)據(jù)流進(jìn)行轉(zhuǎn)發(fā)分類操作,最終實(shí)現(xiàn)匹配模塊的功能。

在系統(tǒng)硬件的開發(fā)中,TCAM的匹配規(guī)則將掉電丟失,如果將其存儲(chǔ)在FPGA內(nèi)部,又會(huì)占用大量FPGA的內(nèi)存資源。因此,本文設(shè)計(jì)了存儲(chǔ)匹配規(guī)則的Flash模塊,實(shí)行系統(tǒng)開機(jī)自動(dòng)更新匹配規(guī)則,減少配置匹配規(guī)則的麻煩。

1.5在線管理和深度處理模塊

深度處理功能是將初次匹配成功的數(shù)據(jù)包轉(zhuǎn)發(fā)至后臺(tái)服務(wù)器進(jìn)行更深層次的數(shù)據(jù)分類,該功能主要由PCI Express接口完成[7]。為降低PCI Express總線的開發(fā)難度,調(diào)用FPGA內(nèi)部專用的資源進(jìn)行開發(fā),可配置成PCI Express2.0和PCI Express3.0。

PCI Express 2.0使用8b/10b編碼,單通道速率達(dá)到5 Gb/s,x8模式下,總線速率可以達(dá)到5 Gb×8b/10b×8=32 Gb/s。PCI Express 3.0使用128b/130b編碼,單通道速率達(dá)到8 Gb/s,x8模式下,總線速率可以達(dá)到8 Gb×128b/130b×8=63.02 Gb/s,除去數(shù)據(jù)包的開銷等冗余字節(jié),可以完成4路萬兆數(shù)據(jù)的線速傳輸。

在線管理功能通過一個(gè)通信網(wǎng)口實(shí)現(xiàn)。平臺(tái)的配置和管理命令信息通過網(wǎng)口接入到系統(tǒng)平臺(tái)中,實(shí)現(xiàn)分流系統(tǒng)的在線配置和管理。

2基于TCAM+FPGA的字符串匹配模塊設(shè)計(jì)

數(shù)據(jù)流的匹配功能是系統(tǒng)設(shè)計(jì)的關(guān)鍵,本節(jié)進(jìn)行更為深入的分析和研究。

2.1硬件匹配原理

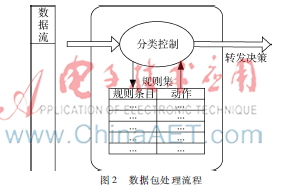

基于TCAM的流分類技術(shù)的基本處理流程如圖2所示。可簡單地理解為將流的標(biāo)志信息輸送進(jìn)匹配轉(zhuǎn)發(fā)引擎,將其與不同匹配規(guī)則進(jìn)行逐條匹配對(duì)比,如果命中規(guī)則,則返回相對(duì)應(yīng)的執(zhí)行動(dòng)作,分類控制器根據(jù)返回的動(dòng)作對(duì)該數(shù)據(jù)流進(jìn)行轉(zhuǎn)發(fā)或者執(zhí)行其他操作。匹配操作一般所涉及的方面為數(shù)據(jù)包頭信息,即五元組信息(源地址、目的地址、源端口、目的端口、協(xié)議類型)。

2.2字符串匹配模塊設(shè)計(jì)

整個(gè)系統(tǒng)的匹配部分由FPGA與TCAM共同配合完成,過濾的規(guī)則包括五元組信息以及指定位置的應(yīng)用層載荷信息等。硬件采用Broadcom公司生產(chǎn)的Netlogic系列芯片以及Altera公司的Stratix V系列芯片完成整體系統(tǒng)的構(gòu)架設(shè)計(jì)。

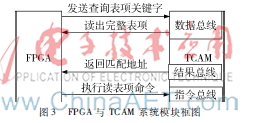

根據(jù)TCAM和FPGA的結(jié)構(gòu)以及各總線完成的功能可以得到如圖3所示的硬件連接基本框圖。其中數(shù)據(jù)總線負(fù)責(zé)匹配數(shù)據(jù)和表項(xiàng)的傳輸以及相關(guān)寄存器的配置;指令總線負(fù)責(zé)輸入指令編碼;結(jié)果總線負(fù)責(zé)輸出匹配結(jié)果,包括設(shè)備ID、最高優(yōu)先級(jí)匹配索引等一系列信息。這些總線的管腳都連接到FPGA的通用I/O管腳上并進(jìn)行等長布線。

由于系統(tǒng)接入的速率較高,所以系統(tǒng)設(shè)計(jì)中要采用有效的措施提高網(wǎng)絡(luò)數(shù)據(jù)流的匹配過濾效率。因此,在算法中將匹配規(guī)則分為兩個(gè)部分進(jìn)行匹配,即協(xié)議描述部分和報(bào)文描述部分(協(xié)議描述部分完成數(shù)據(jù)流五元組信息匹配工作,報(bào)文描述部分完成數(shù)據(jù)流應(yīng)用層載荷信息匹配工作),這兩部分的匹配表項(xiàng)分塊存儲(chǔ)在TCAM中,以匹配表項(xiàng)的第一個(gè)比特位進(jìn)行區(qū)分,“0”代表數(shù)據(jù)流將進(jìn)行協(xié)議描述表項(xiàng)的匹配,“1”表示數(shù)據(jù)流將進(jìn)行報(bào)文描述表項(xiàng)的匹配。

具體操作流程如下:首先由TCAM進(jìn)行協(xié)議描述部分的信息匹配,將數(shù)據(jù)流的五元組信息傳送至TCAM芯片進(jìn)行匹配操作,如果命中TCAM中的規(guī)則,表明已經(jīng)確定數(shù)據(jù)流的協(xié)議特征,然后將代表協(xié)議特征的協(xié)議動(dòng)作地址(Protocol Action ID,PActID)結(jié)果返回至FPGA中,如果關(guān)心該數(shù)據(jù)流中的應(yīng)用載荷信息,則添加報(bào)文描述標(biāo)志位進(jìn)行二次匹配,否則直接根據(jù)PActID的處理命令進(jìn)行處理。在進(jìn)行報(bào)文描述的二次匹配時(shí),將對(duì)特殊報(bào)文的應(yīng)用層關(guān)鍵信息進(jìn)行檢測,以獲得更為準(zhǔn)確的數(shù)據(jù)流信息,從而將該重要數(shù)據(jù)流分配至專用后端處理設(shè)備進(jìn)行精準(zhǔn)的分類分析。

3硬件平臺(tái)測試

根據(jù)上文的設(shè)計(jì)和分析,實(shí)現(xiàn)了基于FPGA+TCAM架構(gòu)的網(wǎng)絡(luò)分流系統(tǒng)。其中包括40 Gb/s高速網(wǎng)絡(luò)信號(hào)接口、一個(gè)管理系統(tǒng)的通信網(wǎng)口、8 GB緩存、TCAM匹配模塊、PCI Express轉(zhuǎn)發(fā)處理接口以及必要的時(shí)鐘芯片、管理接口和電源模塊。

關(guān)于該系統(tǒng)的測試和評(píng)價(jià)指標(biāo)主要包括兩個(gè)方面,即硬件的捕獲效率和軟件的處理分析速度。其評(píng)價(jià)因素包括以下幾項(xiàng)[8]:

(1)系統(tǒng)的吞吐率:分流系統(tǒng)在不丟包的情況下,所能實(shí)時(shí)處理的網(wǎng)絡(luò)數(shù)據(jù)最大帶寬,即系統(tǒng)的吞吐率。

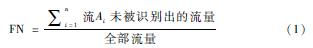

(2)系統(tǒng)的漏報(bào)率(False Negative,F(xiàn)N):系統(tǒng)在一定時(shí)間內(nèi)線速處理捕獲的數(shù)據(jù),但由于系統(tǒng)繁忙而丟失數(shù)據(jù),即系統(tǒng)會(huì)產(chǎn)生漏報(bào)。若流A在系統(tǒng)繁忙時(shí),沒有被系統(tǒng)識(shí)別為流A,那么就存在漏報(bào)。漏報(bào)率的定義就是沒有被識(shí)別出的流A占整個(gè)流量的百分比,即:

(3)系統(tǒng)的更新性能:在數(shù)據(jù)流分類過程中,規(guī)則的定義和更新是系統(tǒng)分類處理的重要環(huán)節(jié),過濾規(guī)則的定義要準(zhǔn)確,更新過程要迅速。

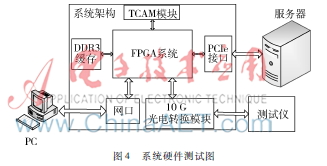

根據(jù)以上測試評(píng)價(jià)因素,設(shè)計(jì)了如圖4所示的硬件測試方案。系統(tǒng)平臺(tái)接收來自VePAL TX300e測試儀發(fā)出的10G SDH信號(hào),通過接收模塊接收測試儀發(fā)出的網(wǎng)絡(luò)數(shù)據(jù),之后進(jìn)行一系列的匹配分類操作,通過PCI Express接口將匹配的數(shù)據(jù)流轉(zhuǎn)發(fā)至服務(wù)器進(jìn)行更為深入的分析。系統(tǒng)測試主要對(duì)吞吐率、漏報(bào)率、誤報(bào)率(體現(xiàn)匹配規(guī)則的設(shè)置合理性)進(jìn)行測試,通過測試得到系統(tǒng)平臺(tái)的處理性能[6]。

硬件測試結(jié)果表明,網(wǎng)絡(luò)分流系統(tǒng)滿足總帶寬40 Gb/s的吞吐量,漏報(bào)率和誤報(bào)率在系統(tǒng)可承受范圍之內(nèi),總體性能達(dá)到設(shè)計(jì)要求。

4結(jié)論

本文設(shè)計(jì)并實(shí)現(xiàn)了一種基于FPGA+TCAM架構(gòu)的網(wǎng)絡(luò)分流系統(tǒng),該分流設(shè)備通過測試可以滿足吞吐率等性能評(píng)價(jià)指標(biāo)。該平臺(tái)的研制彌補(bǔ)了傳統(tǒng)分流過濾系統(tǒng)接入帶寬低、處理效率低等缺點(diǎn)。下一步的研究方向是通過對(duì)分類規(guī)則的統(tǒng)計(jì)分析,得到匹配規(guī)則的最優(yōu)設(shè)置,實(shí)現(xiàn)匹配條目的壓縮、分割,以及通過對(duì)多報(bào)文快速并行處理來提升系統(tǒng)平臺(tái)的整體性能。

參考文獻(xiàn)

[1] 汪立東,錢麗萍.網(wǎng)絡(luò)流量分類方法與實(shí)踐[M].北京:人民郵電出版社,2013.

[2] 王勇,周晴倫,林寧,等.IP流分類器的設(shè)計(jì)與實(shí)現(xiàn)[J].電子科技大學(xué)學(xué)報(bào),2007,36(6): 13621365.