關(guān)鍵詞:

圖說新聞

補(bǔ)充

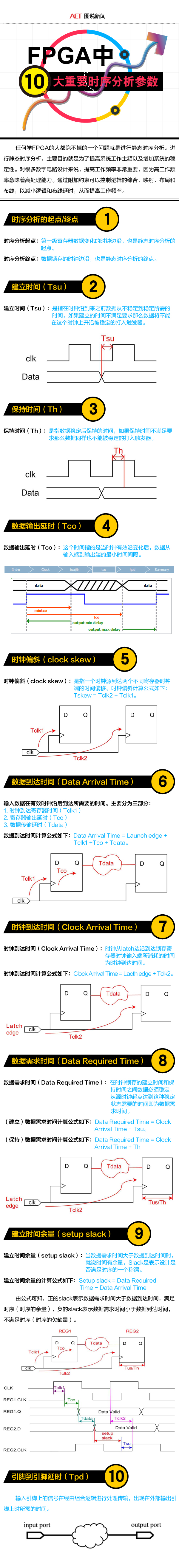

靜態(tài)時(shí)序分析(STA)是采用窮盡分析方法來提取出整個(gè)電路存在的所有時(shí)序路徑,計(jì)算信號(hào)在這些路徑上的傳播延時(shí),檢查信號(hào)的建立和保持時(shí)間是否滿足時(shí)序要求,通過對(duì)最大路徑延時(shí)和最小路徑延時(shí)的分析,找出違背時(shí)序約束的錯(cuò)誤。它不需要輸入向量就能窮盡所有的路徑,且運(yùn)行速度很快、占用內(nèi)存較少,不僅可以對(duì)芯片設(shè)計(jì)進(jìn)行全面的時(shí)序功能檢查,而且還可利用時(shí)序分析的結(jié)果來優(yōu)化設(shè)計(jì),因此靜態(tài)時(shí)序分析已經(jīng)越來越多地被用到數(shù)字集成電路設(shè)計(jì)的驗(yàn)證中。

靜態(tài)時(shí)序分析可以在邏輯綜合、布局布線等步驟后進(jìn)行,F(xiàn)PGA EDA工具在布局布線完成后給出STA結(jié)果,這時(shí)的分析結(jié)果是最接近實(shí)際電路情況的,而邏輯綜合時(shí)的分析結(jié)果是看不到的,也是不準(zhǔn)確的(因?yàn)闆]有物理信息,所以只用于指導(dǎo)布局)。如果是用ASIC綜合工具(比如DC),兩個(gè)階段的STA結(jié)果都可以看。

本站內(nèi)容除特別聲明的原創(chuàng)文章之外,轉(zhuǎn)載內(nèi)容只為傳遞更多信息,并不代表本網(wǎng)站贊同其觀點(diǎn)。轉(zhuǎn)載的所有的文章、圖片、音/視頻文件等資料的版權(quán)歸版權(quán)所有權(quán)人所有。本站采用的非本站原創(chuàng)文章及圖片等內(nèi)容無法一一聯(lián)系確認(rèn)版權(quán)者。如涉及作品內(nèi)容、版權(quán)和其它問題,請(qǐng)及時(shí)通過電子郵件或電話通知我們,以便迅速采取適當(dāng)措施,避免給雙方造成不必要的經(jīng)濟(jì)損失。聯(lián)系電話:010-82306118;郵箱:[email protected]。