文獻(xiàn)標(biāo)識碼: A

DOI:10.16157/j.issn.0258-7998.2016.08.045

中文引用格式: 田澤,索高華,張榮華,等. 基于FPGA的AFDX網(wǎng)絡(luò)高速數(shù)據(jù)采集器設(shè)計(jì)[J].電子技術(shù)應(yīng)用,2016,42(8):179-182.

英文引用格式: Tian Ze,Suo Gaohua,Zhang Ronghua,et al. Design of high speed data acquisition system for AFDX network based on FPGA[J].Application of Electronic Technique,2016,42(8):179-182.

0 引言

試飛系統(tǒng)是一種通過收集、管理飛行試驗(yàn)過程中所產(chǎn)生的飛行試驗(yàn)數(shù)據(jù),建立相關(guān)試驗(yàn)對象的數(shù)據(jù)庫管理和應(yīng)用系統(tǒng),為航空科學(xué)研究提供寶貴的第一手試驗(yàn)數(shù)據(jù),是現(xiàn)代航空技術(shù)不斷發(fā)展和提高的必備手段[1]。在試飛系統(tǒng)的開發(fā)過程中,實(shí)時(shí)、高速采集飛行數(shù)據(jù)成為其關(guān)鍵性的技術(shù)之一,本文提出了一種基于AFDX網(wǎng)絡(luò)的高速數(shù)據(jù)采集器,實(shí)時(shí)采集試飛試驗(yàn)中的垂直速度、氣壓高度、俯仰角、風(fēng)速、風(fēng)向等關(guān)鍵信息,廣泛應(yīng)用在AFDX網(wǎng)絡(luò)大型飛機(jī)的試飛系統(tǒng)中。

本文在深入理解航空標(biāo)準(zhǔn)ARINC664P7協(xié)議,掌握AFDX關(guān)鍵技術(shù)的基礎(chǔ)上[2],結(jié)合AFDX網(wǎng)絡(luò)海量數(shù)據(jù)高速傳輸?shù)奶攸c(diǎn),設(shè)計(jì)并實(shí)現(xiàn)了一種基于FPGA的AFDX數(shù)據(jù)采集器,完成網(wǎng)絡(luò)數(shù)據(jù)的實(shí)時(shí)采集、錯誤幀過濾、參數(shù)挑選和數(shù)據(jù)轉(zhuǎn)發(fā)等功能。該采集器是一款完全具有自主知識產(chǎn)權(quán)的AFDX數(shù)據(jù)采集器,實(shí)現(xiàn)了數(shù)據(jù)采集系統(tǒng)的技術(shù)指標(biāo),完全滿足試飛驗(yàn)證要求,是從標(biāo)準(zhǔn)協(xié)議理解、需求分析、架構(gòu)設(shè)計(jì)與全面驗(yàn)證等完全自主研制的AFDX網(wǎng)絡(luò)采集設(shè)備。

1 AFDX數(shù)據(jù)采集器工作原理

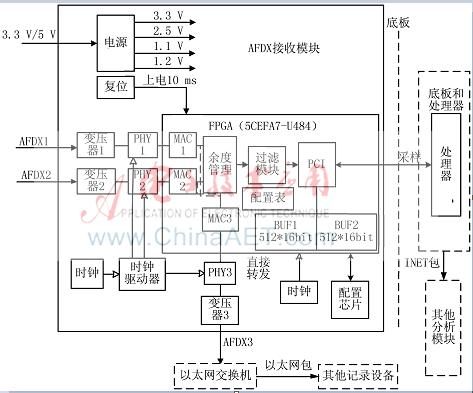

AFDX數(shù)據(jù)采集器主要應(yīng)用于AFDX采集系統(tǒng)中,通過和AFDX網(wǎng)絡(luò)交換機(jī)的任意端口相連,采集余度數(shù)據(jù)信息,經(jīng)AFDX數(shù)據(jù)采集器處理后,完成100%轉(zhuǎn)發(fā)和數(shù)據(jù)挑參,AFDX采集器的系統(tǒng)架構(gòu)如圖1所示。AFDX采集模塊從AFDX1和AFDX2接口處接收AFDX網(wǎng)絡(luò)的余度幀數(shù)據(jù),經(jīng)過變壓器(H1102)、PHY(DP83848YB)將數(shù)據(jù)調(diào)理后與主控芯片F(xiàn)PGA(5CEFA7-U484)進(jìn)行數(shù)據(jù)交互處理。FPGA將AFDX接口上的數(shù)據(jù)采集接收后,給每一幀都附加上接收時(shí)間戳信息,進(jìn)行完整性檢查和余度管理處理,處理后的數(shù)據(jù)一方面參考AFDX挑選參數(shù)配置表要求,挑選出需要的數(shù)據(jù),按配置表指定的地址空間存儲,等待主機(jī)通過PCI接口訪問獲取;另一方面,將余度后的數(shù)據(jù)添加以太網(wǎng)幀頭信息,并100%地通過AFDX3接口發(fā)送出去,再經(jīng)以太網(wǎng)交換機(jī)轉(zhuǎn)發(fā)存儲到記錄盤中。

圖1 AFDX采集模塊系統(tǒng)架構(gòu)

2 AFDX數(shù)據(jù)采集器系統(tǒng)設(shè)計(jì)

2.1 硬件設(shè)計(jì)

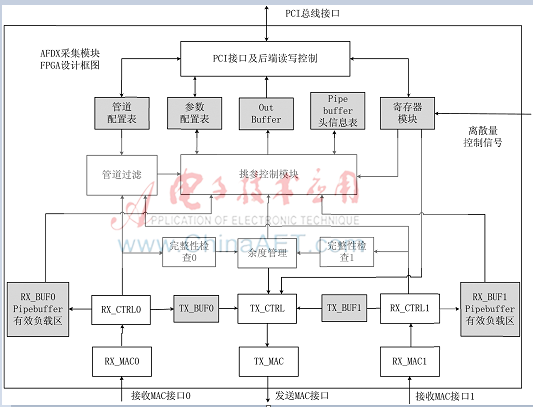

AFDX數(shù)據(jù)采集器主要包括MAC控制管理模塊、PCI接口控制模塊、完整性檢查模塊、余度管理模塊和挑參控制模塊,其設(shè)計(jì)框圖如圖2所示,其中灰色的框圖為存儲模塊,其他顏色均為控制模塊。由于AFDX網(wǎng)絡(luò)數(shù)據(jù)傳輸量大、數(shù)據(jù)速率快,需要對處理的數(shù)據(jù)進(jìn)行臨時(shí)緩存,加之模塊板卡尺寸的限制,以及采集記錄對FPGA的處理能力和存儲配置的高要求,因此,F(xiàn)PGA采用Altera公司Cyclone Ⅴ系列芯片5CEFA7-U484中的EPCS64SI16N,配置模式為AS模,用于控制外部PHY芯片、PCI接口以及模塊的配置、挑參和轉(zhuǎn)發(fā)等功能,來完成數(shù)據(jù)的通信和交互。

圖2 AFDX數(shù)據(jù)采集器設(shè)計(jì)框圖

AFDX數(shù)據(jù)采集器各模塊的主要功能如下:

(1)MAC控制管理模塊。MAC采用MII(Media Inde-

pendent Interface)接口,包括一個(gè)數(shù)據(jù)接口以及一個(gè)MAC與PHY之間的管理接口。數(shù)據(jù)接口用于發(fā)送和接收的兩條獨(dú)立信道;MII管理接口是由時(shí)鐘信號和數(shù)據(jù)信號構(gòu)成的雙信號接口,主要用來監(jiān)視和控制PHY[3]。

(2)PCI接口控制模塊。對外PCI接口滿足基本PCI規(guī)范,對后端提供一組讀寫控制信號,后端讀寫控制主要是對用戶的橋IP讀寫時(shí)序作出相應(yīng)的翻譯,產(chǎn)生對FPGA內(nèi)部資源的讀寫控制。

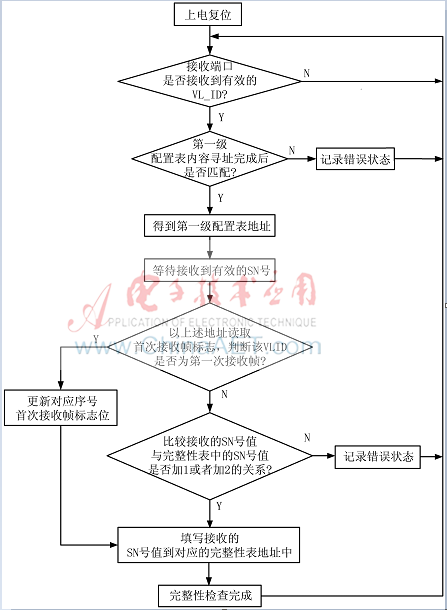

(3)完整性檢查。對于兩個(gè)接收AFDX端口來說具有各自獨(dú)立的完整性檢查表及標(biāo)志位寄存器組,該寄存器組對應(yīng)512個(gè)VL_ID,用于記錄首次接收到的數(shù)據(jù)幀,具體流程如圖3所示。

圖3 接收數(shù)據(jù)幀完整性檢查流程示意圖

(4)余度管理模塊。在接收端口完成完整性檢查后,將各自的VL_ID序列值及本數(shù)據(jù)幀的SN號傳送給余度管理模塊,余度管理模塊輪詢調(diào)度兩個(gè)接收端口的狀態(tài),根據(jù)先到先有效原則過濾掉冗余的數(shù)據(jù)幀[4],具體流程如圖4所示。

圖4 接收數(shù)據(jù)幀余度管理流程示意圖

(5)挑選參數(shù)控制模塊。該模塊包括接收數(shù)據(jù)幀管道過濾和參數(shù)抽取兩大功能。接收數(shù)據(jù)幀管道過濾是對接收到數(shù)據(jù)幀依據(jù)配置的VL_ID和UDP端口號進(jìn)行過濾,過濾后的數(shù)據(jù)幀才符合參數(shù)抽取條件。對過濾后的數(shù)據(jù)幀,根據(jù)挑選參數(shù)配置信息,抽取特定的飛行數(shù)據(jù)。AFDX數(shù)據(jù)幀在以太網(wǎng)幀的基礎(chǔ)上發(fā)展而來,最大幀長為1 518 B,最小幀長為64 B,挑選參數(shù)的范圍可以是AFDX幀格式中的任意字節(jié)。

2.2 軟件設(shè)計(jì)

AFDX數(shù)據(jù)采集器作為一種通用采集模塊,采用純硬件實(shí)現(xiàn),板卡本身不帶軟件。與其配合的CPU軟件包括上層應(yīng)用軟件和驅(qū)動軟件兩部分[5],均位于系統(tǒng)上位機(jī)中,同時(shí)為了更加靈活直觀地表達(dá)顯示處理結(jié)果,增加PC端的圖形應(yīng)用界面,方便分析數(shù)據(jù),顯示處理結(jié)果。

CPU端的驅(qū)動軟件僅提供寄存器訪問接口,如初始化、配置加載、參數(shù)讀取等,均通過寄存器數(shù)據(jù)的讀寫操作完成。

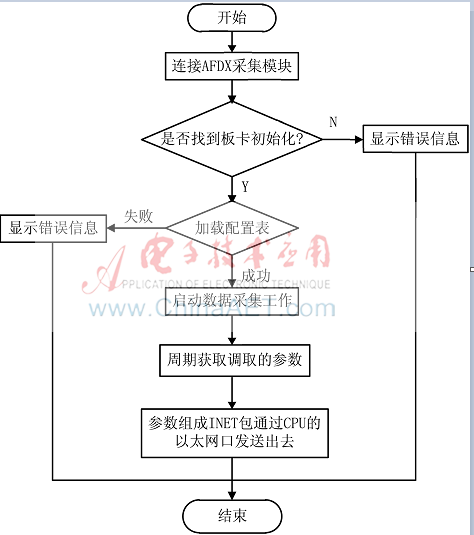

上層應(yīng)用程序主要分為兩部分:(1)PCI接口通信程序,負(fù)責(zé)調(diào)用驅(qū)動程序與FPGA進(jìn)行信息交互;(2)CPU用戶服務(wù)程序,主要進(jìn)行數(shù)據(jù)的接收、組成INET包、發(fā)送等功能。其中上層應(yīng)用程序的基本操作流程如圖5所示。

圖5 上層應(yīng)用程序基本操作流程

3 AFDX數(shù)據(jù)采集器的驗(yàn)證

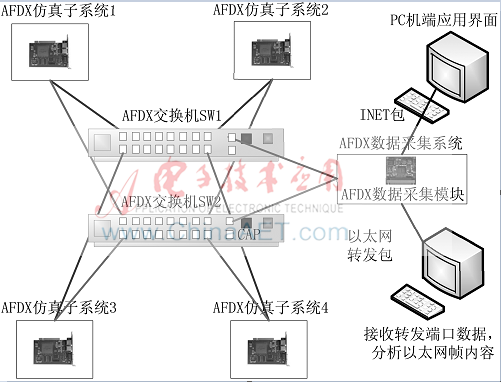

AFDX數(shù)據(jù)采集器的仿真測試平臺如圖6所示,4塊AFDX網(wǎng)絡(luò)仿真卡用于仿真機(jī)載航空電子系統(tǒng),2臺AFDX網(wǎng)絡(luò)交換機(jī)實(shí)現(xiàn)余度網(wǎng)絡(luò)的數(shù)據(jù)轉(zhuǎn)發(fā),AFDX數(shù)據(jù)采集器接收AFDX網(wǎng)絡(luò)交換機(jī)的數(shù)據(jù)信息,完成采集、轉(zhuǎn)發(fā)、挑選參數(shù)功能,上報(bào)數(shù)據(jù)采集系統(tǒng),將以太網(wǎng)包傳送給PC,經(jīng)界面解析后完成數(shù)據(jù)的處理及顯示[6]。

圖6 AFDX數(shù)據(jù)采集仿真測試平臺

本文所設(shè)計(jì)的AFDX網(wǎng)絡(luò)高速數(shù)據(jù)采集器已經(jīng)過功能測試、性能測試、協(xié)議符合性測試及系統(tǒng)聯(lián)試等全面的測試驗(yàn)證,實(shí)測結(jié)果表明,AFDX網(wǎng)絡(luò)高速數(shù)據(jù)采集器功能、性能穩(wěn)定可靠,完全滿足系統(tǒng)設(shè)計(jì)要求。

AFDX網(wǎng)絡(luò)仿真平臺分別發(fā)送64 B、512 B和1 518 B等典型網(wǎng)絡(luò)數(shù)據(jù)包對本文涉及的AFDX網(wǎng)絡(luò)高速數(shù)據(jù)采集器進(jìn)行測試,其采樣率完全滿足設(shè)計(jì)要求,能完成規(guī)定間隔的采集,測試項(xiàng)及測試結(jié)果如表1所示。

4 結(jié)束語

本文所設(shè)計(jì)的AFDX網(wǎng)絡(luò)高速數(shù)據(jù)采集器是一款符合ARINC664協(xié)議,具有自主知識產(chǎn)權(quán)的網(wǎng)絡(luò)采集設(shè)備,該采集器實(shí)時(shí)性強(qiáng)、正確性高、性能穩(wěn)定,完全滿足AFDX網(wǎng)絡(luò)數(shù)據(jù)的采集、轉(zhuǎn)發(fā)、挑選參數(shù)要求。本文詳細(xì)介紹了AFDX采集記錄器的工作原理及軟硬件實(shí)現(xiàn)技術(shù),并搭建仿真測試平臺對其進(jìn)行功能、性能、協(xié)議符合性、系統(tǒng)聯(lián)試等全面測試驗(yàn)證。該模塊設(shè)計(jì)新穎,尺寸小,功耗低,功能性能穩(wěn)定可靠,已成功應(yīng)用于工程實(shí)踐中,運(yùn)行狀態(tài)良好,為試飛驗(yàn)證和AFDX網(wǎng)絡(luò)設(shè)備的國產(chǎn)化打下了堅(jiān)定的基礎(chǔ)。

參考文獻(xiàn)

[1] 曹玉林,胡飛,崔鍵.Oracle封鎖技術(shù)在試飛系統(tǒng)設(shè)計(jì)中的應(yīng)用[J].微處理機(jī),2006,6(6):67-71.

[2] ARINC Specification 664 P7,Avioincs Full Duplex switched Ethernet(AFDX) network[S].2005.

[3] 葉佳字,陳曉剛,張新家.基于AFDX的航空電子通信網(wǎng)絡(luò)的設(shè)計(jì)[J].測控技術(shù),2008,27(6):56-58,60.

[4] 王治,田澤.一種高性能AFDX監(jiān)控卡的實(shí)現(xiàn)技術(shù)研究[J].計(jì)算機(jī)技術(shù)與發(fā)展,2010,20(8):217-220.

[5] 楊峰,田澤.基于USB接口的AFDX網(wǎng)絡(luò)TAP卡設(shè)計(jì)與實(shí)現(xiàn)[J].測控技術(shù)2013,32(5):77-81.

[6] 翟正軍.基于AFDX的高速數(shù)據(jù)采集記錄系統(tǒng)設(shè)計(jì)與實(shí)現(xiàn)[J].測控技術(shù)2013,32(5):17-20.