前言:

目前來看,Bizen可能會(huì)打開老式晶圓廠的邏輯生產(chǎn)之門。如果它能被業(yè)界采用,鑒于將給定技術(shù)節(jié)點(diǎn)上的Bizen裸片面積比CMOS邏輯實(shí)現(xiàn)的面積要小這一優(yōu)勢(shì),或許能夠?qū)⒛柖蓵r(shí)鐘倒退10年或更長(zhǎng)時(shí)間。

傳統(tǒng)晶體管面臨重重壓力

數(shù)十年來,芯片上的晶體管變得越來越小,越來越快,越來越便宜,可是近年來,摩爾定律正在面臨失效。

更小、更快的新型晶體管將使得計(jì)算機(jī)工業(yè)再次取得巨大進(jìn)步。通過這種方式,摩爾定律可能很快重新煥發(fā)生機(jī),計(jì)算機(jī)性能有望迅猛增長(zhǎng)。

晶體管日益發(fā)展,要突破物理極限,傳統(tǒng)方法已經(jīng)不適用,如今必須采用創(chuàng)新方法制造晶體管。

制程升級(jí)所面臨現(xiàn)實(shí)難題

在過去,半導(dǎo)體市場(chǎng)的重點(diǎn)一直圍繞著傳統(tǒng)的芯片微縮,在器件中加入更多功能,然后在每個(gè)工藝節(jié)點(diǎn)上縮小器件。

然而到了最近幾年,芯片在每個(gè)節(jié)點(diǎn)處的微縮都變得更加昂貴和復(fù)雜,如今只有少數(shù)人能夠負(fù)擔(dān)得起在先進(jìn)節(jié)點(diǎn)上設(shè)計(jì)芯片的費(fèi)用。

芯片行業(yè)對(duì)于數(shù)字的高度敏感,越來越成為晶圓代工廠商以及芯片廠商的緊箍咒。對(duì)于處于金字塔尖的巨頭們來說,不無例外。

制程越先進(jìn),面積越小,性能提升的同時(shí)功耗也會(huì)降低,一般來說,10nm對(duì)16nm,功耗大約會(huì)下降20%到30%。數(shù)字越小則代表了越先進(jìn)的技術(shù)水準(zhǔn)。

但無論是芯片廠商還是晶圓代工廠商,越往升級(jí)道路走,承擔(dān)的壓力就越大。去年全球四大純晶圓代工廠中,除了臺(tái)積電,GlobalFoundries、聯(lián)華電子和中芯國(guó)際每晶圓平均收入都在下降。

未來5年能有能力投入先進(jìn)制程的晶圓代工廠,只有臺(tái)積電、三星以及英特爾,激烈競(jìng)爭(zhēng)之下,一定會(huì)讓定價(jià)壓力一路延燒到2022年為止。

傳統(tǒng)結(jié)構(gòu)的多元消耗

在多晶硅和柵極氧化物的界面處形成耗盡區(qū),隨著器件繼續(xù)縮小,多晶硅耗盡變大,并且相當(dāng)于氧化物厚度的較大部分將限制柵極氧化物電容。多元消耗的負(fù)面影響是由于反型層電荷密度的降低和器件性能的降低。

對(duì)于傳統(tǒng)結(jié)構(gòu),隨著溝道長(zhǎng)度的縮小,柵極不能完全控制通道,這是不希望看到的。其影響之一是從漏極到源極引起更多的亞閾值泄漏,這從功耗角度來看不是很好,柵極不能控制遠(yuǎn)離其的泄漏路徑,摻雜被插入通道中減少各種SCE。

新型量子遂穿晶體管誕生

英國(guó)晶圓代工廠Semefab生產(chǎn)了一種名為Bizen的新型量子隧穿晶體管和晶圓工藝樣品,可以大大縮短交貨時(shí)間、晶圓面積和工藝層,同時(shí)提高速度,降低功耗并提高CMOS的柵極密度。

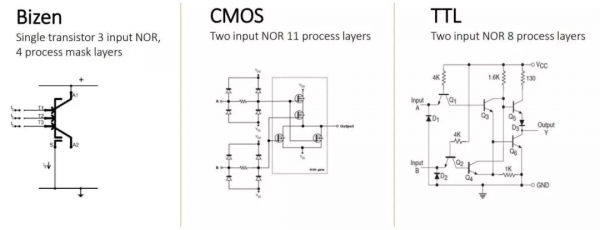

Bizen是由位于英國(guó)諾丁漢的初創(chuàng)公司Search For The Next(SFN)開發(fā)的新型晶體管體系結(jié)構(gòu),其使用了量子隧穿而不是絕緣柵。這種結(jié)構(gòu)由雙極和齊納二極管組合而成,它允許在標(biāo)準(zhǔn)CMOS工藝中僅在8層中產(chǎn)生邏輯,而對(duì)于傳統(tǒng)CMOS晶體管設(shè)計(jì),則需要20到30層。

Semefab在蘇格蘭Glenrothes生產(chǎn)的1μm制程工藝的Bizen測(cè)試芯片將傳統(tǒng)CMOS晶體管設(shè)計(jì)的交貨時(shí)間從15周縮短到了3周,并且芯片面積是同一工藝下同類CMOS器件的三分之一。

Bizen結(jié)構(gòu)的本質(zhì)和應(yīng)用

Bizen是一種新穎的晶體管結(jié)構(gòu),本質(zhì)上是一種PNP器件,其基極通過量子隧道結(jié)驅(qū)動(dòng),并且包括第二個(gè)隧道結(jié)內(nèi)部的自偏置晶體管。目前,這種結(jié)構(gòu)是基于硅的,但是能夠遷移到GaN和其他化合物半導(dǎo)體。

量子隧穿技術(shù)并不是什么新鮮事物,它已被廣泛應(yīng)用于NOR閃存芯片中。但是,在過去的兩年中,借助Bizen該技術(shù)已應(yīng)用于邏輯器件,并已由Semefab進(jìn)行生產(chǎn)、驗(yàn)證。

通過仔細(xì)建模,可以將傳統(tǒng)的橫向和縱向雙極結(jié)構(gòu)集成在一起,以整合成Bizen,而不會(huì)造成額外的工藝復(fù)雜性,可見它的確具有顛覆該行業(yè)的潛質(zhì)。

盡管CMOS容易發(fā)生閂鎖和ESD,但是否有缺陷對(duì)CMOS來說并不是什么大問題,而且CMOS的低功耗特性,已經(jīng)通過了時(shí)間的考驗(yàn),并且普遍可靠。

但是CMOS比較復(fù)雜,并且與功率集成時(shí)更是如此,復(fù)雜性意味著更長(zhǎng)的交貨時(shí)間和更高的成本,而Bizen恰好能夠解決這些問題。

Bizen晶體管結(jié)構(gòu)優(yōu)勢(shì)突出

Bizen的晶體管具有類似PNP的結(jié)構(gòu),但基極有所不同。這是一種雙極機(jī)制,而不是像MOSFET那樣的單極機(jī)制。它不會(huì)像BJT那樣直接與基極接觸,且不會(huì)像MOSFET那樣被氧化物隔離。

取而代之的是到基極的隧道結(jié),其中的摻雜很重,使得Bizen——雙極穩(wěn)壓管——保留了傳統(tǒng)雙極處理的優(yōu)點(diǎn),但通過使用齊納量子隧道機(jī)制消除了缺點(diǎn)。

雖然也將Bizen的兩個(gè)電極稱為“集電極”和“發(fā)射極”,但其實(shí)該結(jié)構(gòu)是對(duì)稱的,可以在不更改功能的情況下交換這兩個(gè)端子。

第二個(gè)隧道結(jié)使Bizen偏置,以便在隧道端子開路時(shí)“接通”但不飽和。雖然這表示在操作過程中有連續(xù)的電流流到地面,但隧道電流通常僅為2nA —5nA,可以通過包括一個(gè)可斷開偏置隧道連接的單一結(jié)構(gòu)來引入低功耗“睡眠”模式。

使用Bizen晶體管構(gòu)建的任何邏輯都是基于電流的邏輯,而不是基于電壓的邏輯,并且,除了電阻器或偏置隧道結(jié)以外,不需要額外占用空間的的電流吸收器。

可以使用Bizen晶體管實(shí)現(xiàn)任意邏輯功能,并且只需4個(gè)工藝光刻掩模,而不是整個(gè)工藝的8個(gè)掩模即可實(shí)現(xiàn)邏輯芯片,這是因?yàn)榭梢栽诰w管內(nèi)部建立晶體管到晶體管的連接。

Bizen的動(dòng)態(tài)功率要低得多,因?yàn)樗鼪]有與CMOS相關(guān)的所有浪費(fèi)功率的MOSFET柵極電容。當(dāng)前的方法允許進(jìn)行模擬計(jì)算,其中電流可以合并,并隨著時(shí)間的流逝而增長(zhǎng)。在不使用SOI襯底的情況下,芯片可以分為8層。

隧穿晶體管的優(yōu)勢(shì)愈發(fā)明顯

晶體管是電子設(shè)備的基本組成元件,在過去40年間,科學(xué)家們主要通過將更多晶體管集成到一塊芯片上來提高電子設(shè)備的計(jì)算能力,但目前這條道路似乎已快走到盡頭。

業(yè)界認(rèn)為,半導(dǎo)體工業(yè)正在快速接近晶體管小型化的物理極限,現(xiàn)代晶體管的主要問題是產(chǎn)生過多的熱量。

電子隧穿設(shè)備商業(yè)化的歷史很長(zhǎng),量子力學(xué)隧穿的原理也已被用于數(shù)據(jù)存儲(chǔ)設(shè)備中,借用最新技術(shù),未來,一個(gè)USB閃存設(shè)備或許能擁有數(shù)十億個(gè)TFET設(shè)備。

使用隧穿晶體管取代目前的晶體管技術(shù)并不需要對(duì)半導(dǎo)體工業(yè)進(jìn)行很大的變革,現(xiàn)有的很多電路設(shè)計(jì)和電路制造基礎(chǔ)設(shè)施都可以繼續(xù)使用。

CMOS制程仍是短期推進(jìn)微縮最佳途徑

要維持摩爾定律存續(xù),唯一的重點(diǎn)在不斷提升晶體管密度,進(jìn)而可持續(xù)提供更佳的效能以及能源效率表現(xiàn)。

只要業(yè)者能夠持續(xù)在更小芯片空間內(nèi)放入更多具更佳能源效率的晶體管,就能持續(xù)讓摩爾定律存續(xù),不論所采用實(shí)現(xiàn)這個(gè)晶體管密度持續(xù)提高的方式為何。

在此情況下,短期內(nèi)要能持續(xù)推動(dòng)摩爾定律前進(jìn),仍必須仰賴既有持續(xù)推出更先進(jìn)CMOS制程的技術(shù),讓晶圓制造端能夠量產(chǎn)閘極長(zhǎng)度更小的晶體管。以臺(tái)積電為例,目前的進(jìn)展是在蝕刻7納米晶體管,并朝5納米制程推進(jìn)。

結(jié)尾:

每一代都有賴全球半導(dǎo)體制程的不斷微縮演進(jìn),帶動(dòng)晶體管密度不斷微縮,以能推出效能及功耗更佳、符合新科技浪潮的更高運(yùn)算需求,進(jìn)而形成當(dāng)前全球科技產(chǎn)業(yè)供應(yīng)鏈現(xiàn)況,并創(chuàng)造一個(gè)愈來愈科技滲透的社會(huì)環(huán)境。

隨著行動(dòng)時(shí)代發(fā)展至今逐漸趨于成熟、成長(zhǎng)性逐漸趨緩,人工智能+5G將會(huì)是下一階段推動(dòng)半導(dǎo)體制程微縮前進(jìn)的主要推動(dòng)力。