除了成熟的PCIE3.0正在廣泛用于終端和SSD存儲設(shè)備之外,PCIE5.0也已經(jīng)蓄勢待發(fā),,除了在今年年中發(fā)布Base 1.0規(guī)范,,近期Base RX夾具也已經(jīng)上線,提供給會員單位訂購:

訂購鏈接

https://pcisig.com/specifications/order-form

圖1 PCIE5.0夾具訂購表

而當(dāng)下市場和產(chǎn)業(yè)界最翹首期待的PCIE4.0也在今年9月邁出了最堅(jiān)實(shí)的一步,。

9月中旬,在上海虹橋萬豪大酒店,,業(yè)界上游公司召集產(chǎn)業(yè)界主要系統(tǒng)廠家和測量廠家進(jìn)行了針對PCIE4.0的第一次Plugfest活動,。

Keysight公司作為業(yè)界唯一一家提供完整測試方案公司獲邀參加,攜帶了高性能DSAZ594A及UXR0334A實(shí)時示波器, M8020A誤碼儀及 E5071C網(wǎng)絡(luò)分析儀參加了本次活動,。

圖2 參會設(shè)備不完全照片

通過本次活動結(jié)合最近的標(biāo)準(zhǔn)發(fā)展情況和其它渠道信息,,如下實(shí)戰(zhàn)經(jīng)驗(yàn),今天在這里與大家分享,。

發(fā)送端(TX)測試

本次活動,,針對TX測試,Keysight準(zhǔn)備了UXR0334A和Z594A高性能實(shí)時示波器,。這兩臺設(shè)備均為四通道25GHz帶寬以上實(shí)時示波器,,專門針對System Board測試,,特別是需要采用Dual Port測試方法。

圖3 PCIE4.0 Phy Test Spec 2.7.5測試項(xiàng)目說明

圖4 PCIE4.0 System Board Dual Port測試方法示意圖

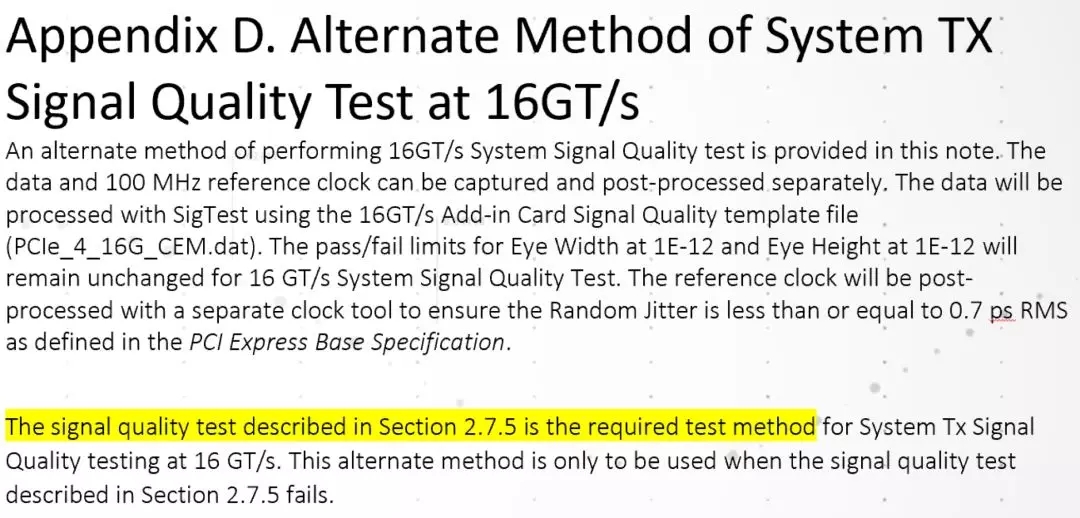

最近也看到很多客戶反饋說,,在PCIE4.0 Phy Test Spec里,,Appendix D有如下描述:

圖5 PCIE4.0 Test Spec Appendix D替代方法說明

注意上面黃色高亮文字,明確說明必須采用2.7.5描述方法,。只有在采用2.7.5方法測試失敗后,,才可以采用替代的數(shù)據(jù)和時鐘分開采集再對時鐘進(jìn)行后處理的方法。

因此必須要補(bǔ)充說明的是:

1.雙端口測試始終是PCIe 4.0 System Board測試的必須方法,。

2.添加了附錄D僅作為應(yīng)急,。最初,如果啟用了最大SSC,,Sigtest會顯示問題,。開發(fā)人員用新方法最近已經(jīng)解決了Sigtest SSC問題。

3.在最近的WorkShop #110上測試的所有系統(tǒng)板均使用雙端口方法進(jìn)行了測試,。

4.雙端口方法同時使用時鐘和數(shù)據(jù)測試,,基于End Device角度很好地詮釋了根組件的信號質(zhì)量。

5.系統(tǒng)板供應(yīng)商可以針對參考時鐘做抖動平衡或折中,,以獲得更好的信號抖動,,并且仍然符合規(guī)范。

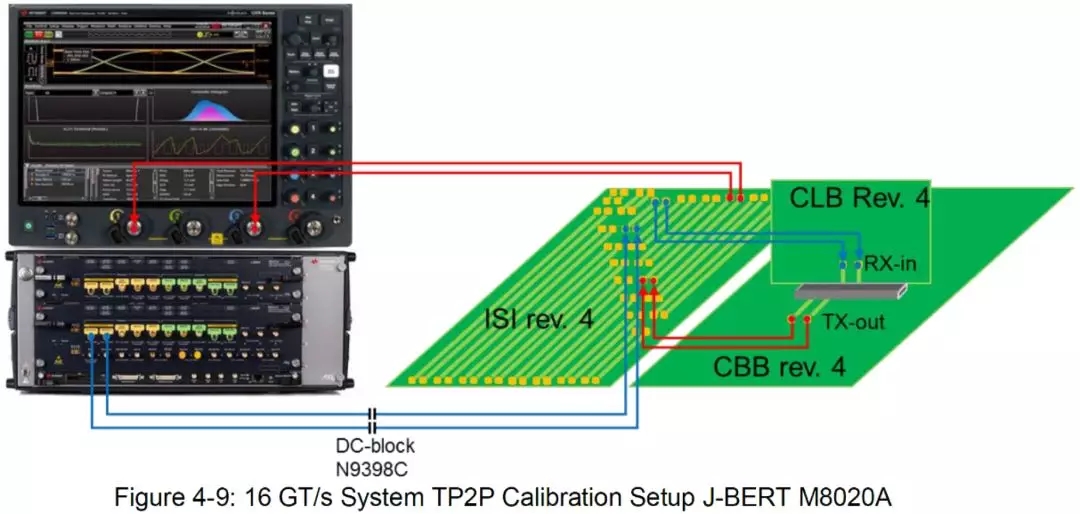

接收端(RX)測試

PCIE4.0 RX測試,,業(yè)界當(dāng)前有3家廠家號稱可以支持,,即Keysight公司,X公司和Y公司,。

Keysight M8020A誤碼儀作為本次活動的主力設(shè)備,,以其業(yè)界卓越的集成度帶來的簡便連接,領(lǐng)先的信號完整性等特點(diǎn)成功圓滿完成了本次測試任務(wù),。成功地為多個被測設(shè)備進(jìn)行鏈路協(xié)商訓(xùn)練進(jìn)入環(huán)回模式,,并順利進(jìn)行了誤碼測試。

而X公司采用的第三方的壓力信號校準(zhǔn)程序使用較小的抖動(Sj)和干擾(DMI)進(jìn)行測試,。從而導(dǎo)致被測設(shè)備未完全經(jīng)受符合規(guī)范的壓力信號的抖動容限測試,,存在隱患!且針對某些設(shè)備在一些鏈路上不能全部確保鏈路協(xié)商和訓(xùn)練進(jìn)入環(huán)回模式,。

Y公司則由于其設(shè)備一直未能在業(yè)界主流平臺上進(jìn)行過完整的全流程RX測試,,因此沒有參加本次活動,也就是說在接收端測試上,,Y公司已經(jīng)出局,!從近期部分客戶反饋和本次活動中也看到,這些客戶在采用Y公司設(shè)備進(jìn)行PCIE4.0接收端測試時存在完全不能進(jìn)入環(huán)回狀態(tài),,因此目前看來深陷泥沼,。

ISI夾具標(biāo)定及鏈路測試

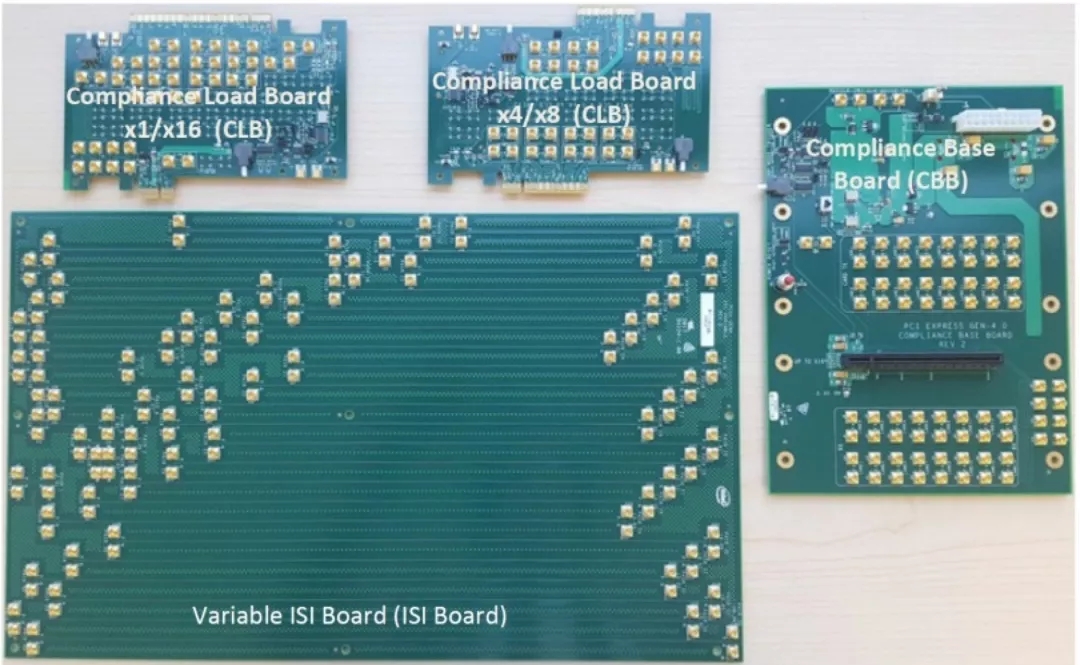

由于PCIE4.0規(guī)范里針對信號發(fā)送鏈路強(qiáng)調(diào)了全部Insertion Loss需滿足不高于 28dB@8GHz,,而針對接收鏈路則強(qiáng)調(diào)全部Insertion Loss需滿足不高于30dB@8GHz,考慮到不同型號,,批次產(chǎn)品和架構(gòu)以及材質(zhì)的差異性,,為了在測試中滿足規(guī)范這一要求,PCI-Sig組織為此專門定義并設(shè)計(jì)了可變ISI夾具板,,在板上設(shè)計(jì)了不同長度尺寸的差分走線配合滿足不同材質(zhì)等情況下全鏈路的整體損耗要求。

圖6 PCIE4.0標(biāo)準(zhǔn)協(xié)會夾具

特別是在進(jìn)行接收端測試之前必須要對注入被測設(shè)備的RX端的壓力信號進(jìn)行嚴(yán)格和準(zhǔn)確的校準(zhǔn)以確保符合規(guī)范,。如下圖針對System Board的RX信號校準(zhǔn)示意圖,。

圖7 PCIE4.0 16GT/s System RX Cal示意圖

因此在進(jìn)行RX測試前必須針對包括ISI夾具在內(nèi)的全鏈路進(jìn)行標(biāo)定并選擇總鏈路損耗在27-30dB。

在參加本次活動之前通常以為采用網(wǎng)絡(luò)分析儀標(biāo)定之后即可,,通過這次反復(fù)插拔活動發(fā)現(xiàn):

反復(fù)多次插拔和連接之后夾具上的SMP連接頭容易出現(xiàn)過勞和損傷,,因此在大批量測試情況下需要不定期采用網(wǎng)絡(luò)分析儀進(jìn)行測試標(biāo)定,目前看來至少1-2周需進(jìn)行一次標(biāo)定測試,。也就是說,,網(wǎng)絡(luò)分析儀已經(jīng)成為今天的典型高速標(biāo)準(zhǔn)如PCIExpress4.0研究開發(fā)的必備工具。

以上關(guān)于最新的PCIE4.0/5.0測試方法更新和最新進(jìn)展,,謝謝閱讀,!未來將繼續(xù)更新,歡迎您的持續(xù)關(guān)注,!