隨著芯片集成度的越來越高,如今的IC測試面臨著前所未有的挑戰(zhàn):

測試時間越來越長,百萬門級的SoC測試可能需要幾個月甚至更長的時間;

測試矢量的數(shù)目越來越多,覆蓋率卻難以提高,人們不知道究竟要用多少測試矢量才能覆蓋到所有的器件;

測試設備的使用成本越來越高,直接影響到芯片的成本。

一、測試的概念和原理

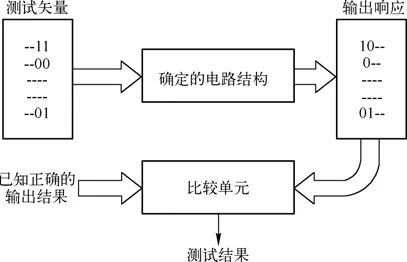

集成電路(IC)測試是IC產(chǎn)業(yè)鏈中重要的一環(huán),而且是不可或缺的一環(huán),它貫穿于從產(chǎn)品設計開始到完成加工的全過程。目前所指的測試通常是指芯片流片后的測試,定義為對被測電路施加已知的測試矢量,觀察其輸出結(jié)果,并與已知正確輸出結(jié)果進行比較而判斷芯片功能、性能、結(jié)構(gòu)好壞的過程。圖1說明了測試原理,就其概念而言,測試包含了三方面的內(nèi)容:已知的測試矢量、確定的電路結(jié)構(gòu)和已知正確的輸出結(jié)果。

圖1集成電路測試原理

二、測試及測試矢量的分類

1.按測試目的分類

根據(jù)測試的目的不同,可以把集成電路測試分為4種類型。

(1)驗證測試(Verification Testing,也稱作Design Validation)

當一款新的芯片第一次被設計并生產(chǎn)出來,首先要接受驗證測試。在這一階段,將會進行功能測試,以及全面的AC、DC參數(shù)的測試。通過驗證測試,可以診斷和修改設計錯誤,為最終規(guī)范(產(chǎn)品手冊)測量出芯片的各種電氣參數(shù),并開發(fā)出測試流程。

(2)生產(chǎn)測試(Manufacturing Testing)

當芯片的設計方案通過了驗證測試,進入量產(chǎn)階段之后,將利用前一階段調(diào)試好的流程進行生產(chǎn)測試。在這一階段,測試的目的就是明確做出被測芯片是否通過測試的判決。由于每一顆芯片都要進行生產(chǎn)測試,所以測試成本是這一階段的首要問題。從這一角度出發(fā),生產(chǎn)測試通常所采用的測試向量集不會包含過多的功能向量,但是必須有足夠高的模型化故障的覆蓋率。

(3)可靠性測試(Reliability Testing)

通過生產(chǎn)測試的每一顆芯片并不完全相同,最典型的例子就是同一型號產(chǎn)品的使用壽命不盡相同。可靠性測試就是要保證產(chǎn)品的可靠性,通過調(diào)高供電電壓、延長測試時間、提高溫度等方式,將不合格的產(chǎn)品(如會很快失效的產(chǎn)品)淘汰出來。

(4)接受測試(Acceptance Testing)

當芯片送到用戶手中,用戶將進行再一次的測試。例如,系統(tǒng)集成商在組裝系統(tǒng)之前,會對買回的各個部件進行此項測試。

2.按測試方式的分類

根據(jù)測試方式的不同,測試矢量也可以分為3類。

(1)窮舉測試矢量(Exhaustive Vector)

窮舉測試矢量是指所有可能的輸入矢量。該測試矢量的特點是覆蓋率高,可以達到100%,但是其數(shù)目驚人,對于具有n個輸入端口的芯片來說,需要2n個測試矢量來覆蓋其所有的可能出現(xiàn)的狀態(tài)。例如,如果要測試74181ALU,其有14個輸入端口,就需要214=16384個測試矢量,對于一個有38個輸入端口的16位的ALU來說,以10 MHz的速度運行完所有的測試矢量需要7.64個小時,顯然,這樣的測試對于量產(chǎn)的芯片是不可取的。

(2)功能測試矢量 (Functional Vector)

功能測試矢量主要應用于驗證測試中,目的是驗證各個器件的功能是否正確。其需要的矢量數(shù)目大大低于窮舉測試,以74181ALU為例,只需要448個測試矢量,但是目前沒有算法去計算矢量是否覆蓋了芯片的所有功能。

(3)結(jié)構(gòu)測試矢量 (Structural Vector)

這是一種基于故障模型的測試矢量,它的最大好處是可以利用電子設計自動化(EDA)工具自動對電路產(chǎn)生測試向量,并且能夠有效地評估測試效果。74181ALU只需要47個測試矢量。這類測試矢量的缺點是有時候工具無法檢測所有的故障類型。

三、自動測試設備

與IC測試有關的另外一個重要概念就是自動測試設備(ATE,Automatic Test Equipment)。使用ATE可以自動完成測試矢量的輸入和核對輸出的工作,大大提高了測試速度,但是目前其仍舊面臨不小的挑戰(zhàn)。

該挑戰(zhàn)主要來自于兩方面。首先是不同芯片對于同種測試設備的需求。在一般情況下,4~5個芯片需要用同一個測試設備進行測試,測試時間只有一批一批的安排。每種設計都有自己的測試矢量和測試環(huán)境,因此改變被測芯片時,需要重新設置測試設備和更新測試矢量。其次是巨大測試矢量對于測試設備本身性能的要求。目前,百萬門級SoC的測試矢量規(guī)模非常大,可能達到數(shù)萬個,把這些測試矢量讀進測試設備并初始化需要相當長的時間。解決這一方法的途徑是開發(fā)具有大容量矢量存儲器的測試矢量加載器。例如,Advantest的W4322的高速測試矢量加載服務器,可以提供72 GB的存儲空間,可以縮短80%的矢量裝載時間。

四、可測性的概念

可測性是現(xiàn)在經(jīng)常使用,卻經(jīng)常被理解錯的一個詞。其框架式的定義是,可測性是在一定的時間和財力限制下,生成、評價、運行測試,以滿足一系列的測試對象(例如,故障覆蓋率、測試時間等)。對一些具體的集成電路來說,對該定義的解釋由于使用工具和已有的技術水平的不同而不同。目前工業(yè)界使用的一個范圍比較窄的定義是,可測性是能夠測試檢驗出存在于設計產(chǎn)品中的各種制造缺陷的程度。

1.可測性設計(DFT,Design For Testability)

所謂可測性設計是指設計人員在設計系統(tǒng)和電路的同時,考慮到測試的要求,通過增加一定的硬件開銷,獲得最大可測性的設計過程。簡單來說,可測性設計即是指為了達到故障檢測目的所做的輔助性設計,這種設計為基于故障模型的結(jié)構(gòu)測試服務,用來檢測生產(chǎn)故障。目前,主要的可測性設計方法有掃描通路測試、內(nèi)建自測試和邊界掃描測試等。

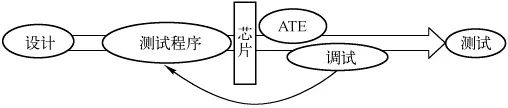

為什么說DFT是必需的?讓我們先來看看傳統(tǒng)的測試方法,如圖2所示。在傳統(tǒng)測試方法中,設計人員的職責止于驗證階段,一旦設計人員認定其設計滿足包括時序、功耗、面積在內(nèi)的各項指標,其工作即告結(jié)束。此后,測試人員接過接力棒,開始開發(fā)合適的測試程序和足夠的測試圖形,用來查找出隱藏的設計和制造錯誤。但是,在其工作期間很少了解設計人員的設計意圖,因此,測試人員必須將大量寶貴的時間花在梳理設計細節(jié)上,而且測試開發(fā)人員必須等到測試程序和測試模型經(jīng)過驗證和調(diào)試之后才能知道早先的努力是否有效。沿用傳統(tǒng)測試方法,測試人員別無選擇,只能等待流片完成和允許他使用昂貴的自動測試設備(ATE)。這就導致了整個設計-測試過程周期拉大,充斥著延誤和效率低下的溝通。

圖2 傳統(tǒng)的設計測試流程

自20世紀80年代以來,規(guī)模較大的半導體生產(chǎn)商就開始利用DFT技術來改善測試成本,降低測試復雜度。如今,前端設計人員都能清楚地認識到只要使用恰當?shù)墓ぞ吆头椒ǎ谠O計的最初階段就對測試略加考慮,會在將來受益匪淺,見圖3。DFT技術與現(xiàn)代的EDA/ATE技術緊密地聯(lián)系在一起,大幅降低了測試對ATE資源的要求,便于集成電路產(chǎn)品的質(zhì)量控制,提高產(chǎn)品的可制造性,降低產(chǎn)品的測試成本,縮短產(chǎn)品的制造周期。

圖3 現(xiàn)在的設計測試流程

2.可控制性和可觀測性

可控制性(Controllability)和可觀測性(Observability)是可測性設計中的重要概念。可控制性表示通過電路初始化輸入端控制電路內(nèi)部節(jié)點邏輯狀態(tài)的難易程度,如果電路內(nèi)部節(jié)點可被驅(qū)動為任何值,則稱該節(jié)點是可控的。可觀察性表示通過控制輸入變量,將電路內(nèi)部節(jié)點的故障傳播到輸出端以便對其進行觀察的難易程度。如果電路內(nèi)部節(jié)點的取值可以傳播到電路的輸出端,且其值是預知的,則稱該節(jié)點是可觀察的。

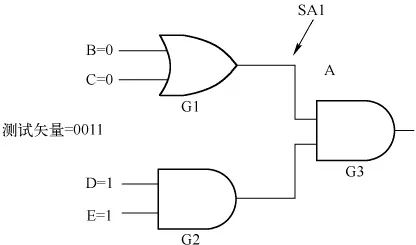

所謂集成電路的可控制性可以理解為將該信號設置成0或者1的難度。如圖4所示,對于與門G3輸入端口A的固定為邏輯值1的故障,可以通過在外圍端口B、C、D、E施加矢量0011來檢測,因此認為該節(jié)點是可控制的。

圖4 可控制性舉例

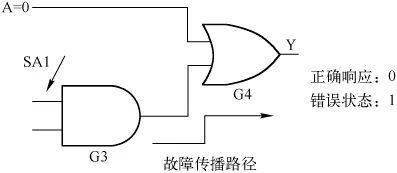

可觀測性是指觀察這個信號所產(chǎn)生故障的難度。如圖5所示,G3輸入端口A的固定為邏輯值1的故障可以通過施加0向量而傳輸?shù)酵鈬丝赮,因此認為其為可觀測的。

圖5 可觀測性舉例

五、可測性設計的優(yōu)勢和不足

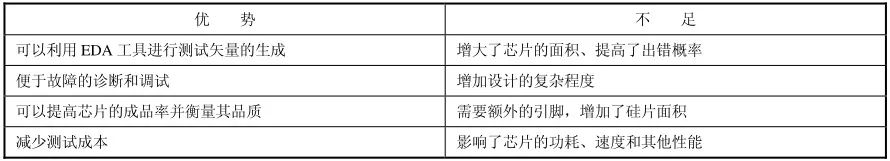

人們通常會問,為什么要在原有的電路中加入額外的測試結(jié)構(gòu)?這個問題確實很難回答,DFT的經(jīng)濟性涉及包括設計、測試、制造、市場銷售等各個方面。不同的人衡量的標準也不一樣,設計工程師通常覺得DFT附加的電路會影響芯片的性能,而測試工程師會認為有效的可測性設計將大大提高故障覆蓋率。表1列出了可測性設計的一些優(yōu)勢和不足。

表1 DFT的優(yōu)勢和不足

來自工業(yè)界的許多實例證明,加入額外的測試結(jié)構(gòu)確實有助于芯片成品率的提高,從而大幅降低了芯片的制造成本。當然為了彌補一些缺陷,DFT技術本身也在不斷地改進和發(fā)展。

六、常用的可測性設計

1.內(nèi)部掃描測試設計

內(nèi)部掃描設計的主要任務就是要增加內(nèi)部狀態(tài)的可控制性和可觀察性。對于集成電路而言,其做法是將內(nèi)部時序存儲邏輯單元連接成移位寄存器形式,從而可將輸入信號通過移位輸入內(nèi)部存儲邏輯單元以滿足可控制性要求。同樣,以移位方式將內(nèi)部狀態(tài)輸出以滿足可觀察性要求。采用掃描路徑設計的芯片在測試方式下工作時,內(nèi)部構(gòu)成一個長的移位寄存器。

如圖6所示,掃描測試工具首先把普通的觸發(fā)器變成了帶掃描使能端和掃描輸入的觸發(fā)器,然后把這些觸發(fā)器串聯(lián)在一起。當scan_enable無效時,電路可以正常工作,當scan_enable有效時,各觸發(fā)器的值將可以從來自片外的scan_in信號串行輸入。這樣就可以對各片內(nèi)寄存器賦值,也可以通過scan_out得到它們的值。支持掃描測試設計的工具有Synopsys公司的DFT Compiler及Mentor的DFT Advisor。

圖6 掃描測試電路

2.自動測試矢量生成(ATPG,Automation Test Pattern Generation)

ATPG采用故障模型,通過分析芯片的結(jié)構(gòu)生成測試向量,進行結(jié)構(gòu)測試,篩選出不合格的芯片。通常ATPG工具和掃描測試工具配合使用,可以同時完成測試矢量的生成和故障仿真。

首先是故障類型的選擇。ATPG可以處理的故障類型不僅是阻塞型故障,還有延時故障和路徑延時故障等,一旦所有需要檢測的故障類型被列舉,ATPG將對這些故障進行合理的排序,可能是按字母順序、按層次結(jié)構(gòu)或者隨機排序。

在確定了故障類型后,ATPG將決定如何對這類故障進行檢測,并且需要考慮施加激勵向量測試點,需要計算所有會影響目標節(jié)點的可控制點。此類算法包括D算法等。

最后是尋找傳輸路徑,可以說這是向量生成中最困難的,需要花很多時間去尋找故障的觀測點的傳播。因為通常一個故障擁有很多的可觀測點,一些工具一般會找到最近的那一個。不同目標節(jié)點的傳輸路徑可能會造成重疊和沖突,當然這在掃描結(jié)構(gòu)中是不會出現(xiàn)的。支持產(chǎn)生ATPG的工具有Mentor的Fastscan和Synopsys的TetraMAX。

3.存儲器內(nèi)建自測試(Memory Built-in-self-test)

內(nèi)建自測試是當前廣泛應用的存儲器可測性設計方法,它的基本思想是電路自己生成測試向量,而不是要求外部施加測試向量,它依靠自身來決定所得到的測試結(jié)果是否正確。因此,內(nèi)建自測必須附加額外的電路,包括向量生成器、BIST控制器和響應分析器,如圖7所示。BIST的方法可以用于RAM、ROM和Flash等存儲設備,主要用于RAM中。大量關于存儲器的測試算法都是基于故障模型的。常用的算法有棋盤式圖形算法和March算法。

圖7 BIST的基本結(jié)構(gòu)

支持BIST的工具有Mentor的mBISTArchitect和Synopsys的SoCBIST。

4.邊界掃描測試(Boundary Scan)

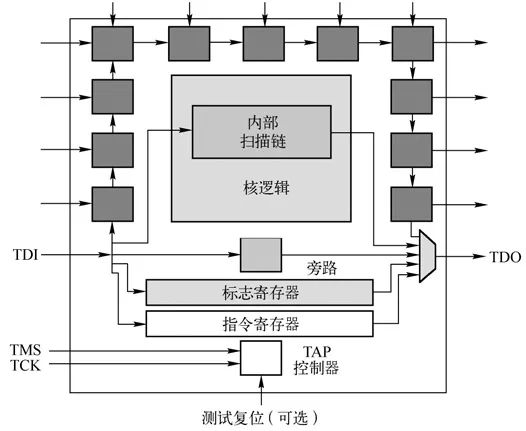

邊界掃描的原理是在核心邏輯電路的輸入和輸出端口都增加一個寄存器,通過將這些I/O上的寄存器連接起來,可以將數(shù)據(jù)串行輸入被測單元,并且從相應端口串行讀出。在這個過程中,可以實現(xiàn)芯片級、板級和系統(tǒng)級的測試。其中,最主要的功能是進行板級芯片的互連測試,如圖8所示。

圖8 利用邊界掃描進行板級測試

邊界掃描是歐美一些大公司聯(lián)合成立的一個組織——聯(lián)合測試行動小組(JTAG)為了解決印制電路板(PCB)上芯片與芯片之間互連測試而提出的一種解決方案。由于該方案的合理性,它于1990年被IEEE采納而成為一個標準,即IEEE 1149.1。該標準規(guī)定了邊界掃描的測試端口、測試結(jié)構(gòu)和操作指令,其結(jié)構(gòu)如圖9所示。該結(jié)構(gòu)主要包括TAP控制器和寄存器組。其中寄存器組包括邊界掃描寄存器,旁路寄存器,標志寄存器和指令寄存器。主要端口為TCK、TMS、TDI、TDO,另外還有一個用戶可選擇的端口TRST。

支持邊界掃描的自動設計工具有Mentor的BSD Architect和Synopsys的BSD Compiler。

圖9 IEEE 1149.1結(jié)構(gòu)