什么是自動IP生成

隨著半導體行業(yè)的發(fā)展,SoC已經成為了芯片設計的最常見形式。在SoC中,通常都包括了多個半導體IP,之后在頂層把這些IP連接到一起組成完整的系統(tǒng)。

常規(guī)的IP設計過程費時費力。一般來說,數(shù)字IP設計首先需要定義IP實現(xiàn)的功能、接口和高層架構設計,此后進一步細化到微架構設計(如模塊劃分和RTL定義),然后再是映射到具體的電路設計。模擬IP設計則是需要首先定義模塊的性能指標(spec),之后根據(jù)該指標再去仔細調整電路/版圖設計并隨時進行仿真驗證,在多次迭代之后獲得最終的模擬IP設計。在整個過程中,每一個環(huán)節(jié)都需要大量的時間和人力。

與之相對,自動IP生成則是希望能通過直接把頂層架構設計(對于數(shù)字IP)或模塊指標(模擬IP)映射到電路。這樣一來,就能大大節(jié)省設計的時間和成本,同時可以做更多的設計探索,最終收斂到最優(yōu)設計。

數(shù)字領域的自動IP生成

傳統(tǒng)的數(shù)字電路IP設計通常需要經過以下幾個環(huán)節(jié):

(1)制定頂層的架構和算法(使用C語言等高級語言設計),并且進行算法驗證;

(2)根據(jù)頂層架構做模塊劃分和微架構設計/優(yōu)化,包括時序規(guī)劃、clock gating等;

(3)根據(jù)微架構設計RTL;

(4)根據(jù)RTL進行綜合生成門級網(wǎng)表;

(5)根據(jù)門級網(wǎng)表做布局布線生成版圖GDS。

而數(shù)字領域的自動IP生成則是指使用(1)中的高級語言設計,跳過(2)和(3),直接生成RTL/門級網(wǎng)表/GDS。

我們認為,數(shù)字領域的自動IP生成非常適合信號處理型IP。信號處理型IP主要是對于輸入信號做數(shù)學運算,其中的主要部分即做運算的數(shù)據(jù)通路(data path),典型的信號處理型IP包括數(shù)字濾波器、視頻編解碼等等。

我們可以更進一步把數(shù)字領域的自動IP生成分為兩大類。一類是對于某些算法和結構相對固定的數(shù)字IP,根據(jù)頂層的IP spec輸入去自動生成電路設計。典型的例子是MathWorks Matlab中的數(shù)字濾波器自動RTL綜合,用戶只需要輸入數(shù)字濾波器的類型(FIR,IIR)、指標(帶寬、中心頻率、濾波抑制比、通帶紋波等)等信息,就能自動生成高質量的數(shù)字濾波器RTL代碼。在這類應用中,使用自動生成的優(yōu)勢在于可以大大較少設計驗證的迭代時間。例如,在數(shù)字濾波器設計中,用戶最關心的就是帶寬、濾波抑制比等高層的頻域指標,但是如果使用RTL去做設計仿真的話,需要自行加入相應的激勵波形,同時輸出的時域波形圖也無法直接反映頻域的特性,而需要去把該波形圖的數(shù)據(jù)點導出再去做傅立葉分析才能驗證設計是否滿足頻域指標。這一來一去就會花很多時間,而使用數(shù)字IP直接生成則可以直接在Matlab里去驗證濾波器的性能以及把濾波器接入系統(tǒng)中的整體性能,這樣就大大加速了設計流程。

另一種數(shù)字IP自動生成則是針對更一般電路,它通常使用C/C++/SystemC等高級語言作為輸入,其輸出則是功能和高級語言輸入等價的RTL/門級網(wǎng)表/GDS。這類數(shù)字自動生成工具通常又稱作“high-level synthesis”(HLS)。HLS的優(yōu)點和限制都很明確:優(yōu)點是整體設計和驗證速度都很快,省去了微結構設計和RTL編寫的時間,驗證上也可以直接和使用高級語言的系統(tǒng)驗證方便地整合在一起。而其缺陷則在于高級語言在描述數(shù)字邏輯時的顆粒度較粗,且一般沒有時序的概念,因此HLS生成的電路通常僅能保證功能正確,但是在電路的速度(往往由時序劃分決定)和功耗(HLS對于常規(guī)的低功耗設計方法學如clock gating的支持還不方便)上比起手寫的RTL可能有差距。在信號處理模塊上,HLS生成的電路比起手寫RTL差距較小,差距可以在20%以內,甚至在一些場合可以做到HLS生成的電路與手寫RTL性能沒有差距。目前,HLS的主要產品包括Mentor Graphics的Catapult,Cadence的Stratus,Xilinx的Vivado HLS等。

HLS的概念提出已經有十多年,但是在最近得到了越來越多的重視。這除了和HLS本身技術發(fā)展之外,還和半導體行業(yè)的趨勢有關。在過去,半導體芯片的主要范式還是大的半導體廠商提供通用的處理器平臺,在這樣的范式下,由于在計算平臺上執(zhí)行的算法不確定,因此半導體廠商的策略就是把通用處理平臺的每一個細節(jié)都做到完美,這樣一來自然就沒有HLS的發(fā)展空間。而在最近,隨著人工智能、大數(shù)據(jù)和下一代多媒體需求的出現(xiàn),SoC上對于執(zhí)行固定算法的數(shù)字IP的需求在大大增強,而且隨著互聯(lián)網(wǎng)廠商加入芯片戰(zhàn)局也為半導體芯片快速交付提出了需求。在這種情況下,HLS就變得越來越有價值。這是因為,對于這類執(zhí)行固定算法的數(shù)字信號處理IP,算法本身以及IP頂層架構的優(yōu)化對于SoC芯片整體性能的影響往往遠遠大于具體電路實現(xiàn)帶來的影響。在較短交付周期的限制下,如果使用傳統(tǒng)的數(shù)字設計方法論,往往就意味著留給頂層架構和算法探索的時間比較少,最后導致使用高效的RTL代碼實現(xiàn)了并非最優(yōu)的架構/算法。反之,如果使用HLS,則可以大大壓縮RTL設計的時間,這樣就給架構/算法探索留下了更多時間,最后盡管HLS生成的電路性能可能比手寫RTL要差20%,但是頂層架構/算法的優(yōu)化帶來的影響可能是2-3倍的性能提升,而HLS帶來的time-to-market的改善則可能是更大的影響。

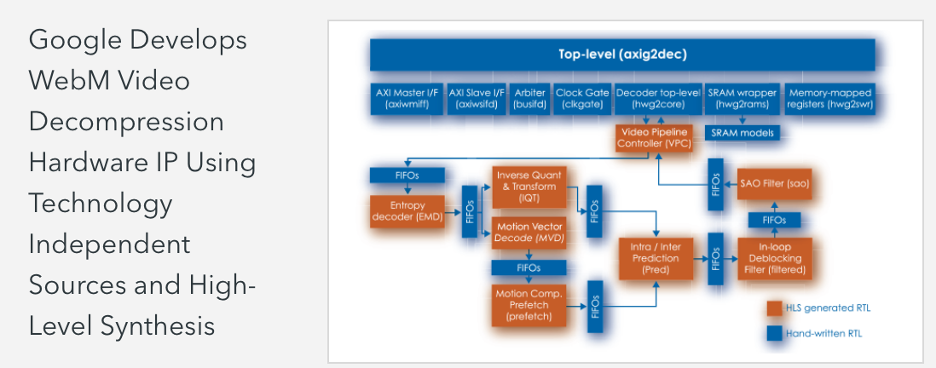

谷歌使用Catapult HLS實現(xiàn)了視頻解碼IP中的絕大部分模塊。該IP是典型的數(shù)字信號處理IP。

模擬IP自動生成

在模擬電路領域,自動IP生成也是EDA領域的一個熱門方向。

模擬IP自動生成目前能做的是給定一種電路結構(例如帶4-tap DFE的wireline receiver)和模塊指標,自動生成電路圖和版圖并完成仿真驗證。在未來,隨著電路庫中電路結構數(shù)量的上升,也有機會能實現(xiàn)僅需輸入模塊功能和指標,IP自動生成器可以自主選擇最優(yōu)電路結構并生成符合指標的電路和版圖。

模擬IP自動生成可以分成兩部分,即自動調優(yōu)電路中的晶體管參數(shù)和自動生成版圖。前者至少有30年的歷史,上世紀九十年代就有不少學者在研究用各種數(shù)學優(yōu)化方法來自動選擇模擬電路中晶體管的參數(shù)。在今天,如果僅僅是選擇電路中的晶體管參數(shù)而不考慮自動生成版圖,那么常規(guī)的EDA工具中的參數(shù)掃描就能滿足大部分需求。但是,電路圖設計中的晶體管參數(shù)自動調優(yōu)往往不能落實到實際設計中,這是因為隨著半導體工藝越來越先進,模擬電路中的版圖效應也越來越顯著,而電路圖設計中的晶體管參數(shù)調優(yōu)并不能反映版圖的影響,因此往往掃描得到的電路圖最優(yōu)晶體管參數(shù)和版圖設計完成后的最優(yōu)參數(shù)有一定差別。因此常見的做法是先做一個版本電路圖設計,然后去畫版圖并做帶版圖效應的電路仿真,然后再去調整電路圖設計中的晶體管參數(shù)。在這個過程中,即使電路圖中的晶體管參數(shù)都能自動化調優(yōu),但是整體的設計流程還是卡在了手工畫版圖——仿真——調整電路圖晶體管參數(shù)這個循環(huán)里。

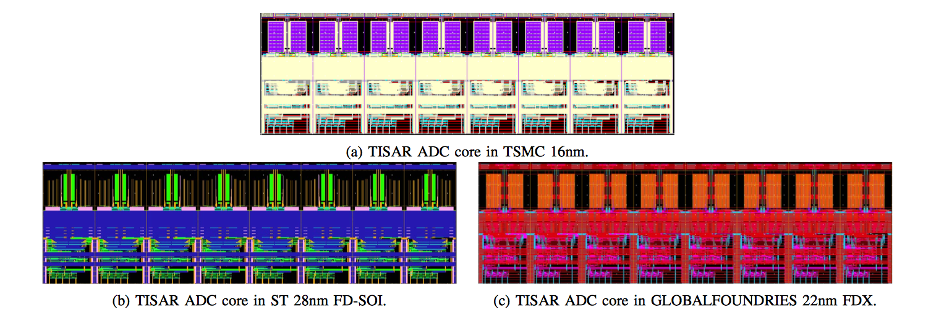

而模擬IP自動生成解決的最大痛點,就在于能自動生成版圖。這樣一來,整體的流程都可以做到自動化,僅需輸入指標,生成器可以自動生成一組晶體管參數(shù),自動生成版圖做仿真,并自動根據(jù)版圖仿真結果去調整電路圖晶體管參數(shù)。這就大大節(jié)省了模擬IP生成的人力和時間,并提升了設計效率。目前,模擬IP自動生成做的最領先的是UC Berkeley的BAG(Berkeley Analog Generator)項目,該項目已經能自動生成SerDes、ADC等復雜的模擬/混合信號IP的電路設計和版圖,并且在28nm和16nm等先進工藝下都得到了流片驗證。

BAG自動生成的ADC版圖

自動IP生成是中國EDA的機會

自動IP生成在美國得到了相當?shù)闹匾暎绹鴩栏呒壯芯坑媱澗郑―ARPA)2019年的電子復興計劃(ERI)中,自動IP生成(IDEA)是其重點扶持方向之一。我們認為,這個領域對于中國的半導體行業(yè)有重要價值,同時中國距離全球先進的差距也并不大,因此如果得到足夠支持的話有機會能在未來數(shù)年內追趕全球領先。

對于數(shù)字IP自動生成來說,其主戰(zhàn)場在信號處理領域,這就從一個方面降低了工具所需要覆蓋的設計范圍。只要能加速設計流程,國產EDA版本的HLS完全可以考慮僅僅只支持一部分C/SystemC語言的特性或者甚至是自主的高級語言,只需要該語言能方便地描述這類信號處理電路即可。我們看到,在人工智能、大數(shù)據(jù)和下一代多媒體等新興市場,中國有一大批互聯(lián)網(wǎng)公司進入了芯片設計領域(如阿里,百度,以及最近的字節(jié)跳動等),這些互聯(lián)網(wǎng)公司對于芯片的主要訴求就是加速信號處理,并且需要能快速交付,因此國產HLS對于這些互聯(lián)網(wǎng)公司的芯片項目將有很大的吸引力。

對于模擬IP自動生成來說,我們看到自動版圖生成技術至今大約有5年的時間,可以說中國半導體行業(yè)如果有心發(fā)展的話,完全可以在未來幾年內趕上并達到全球一流水平。擁有下一代的自動模擬IP生成工具,也有利于鞏固中國模擬IP設計強國的地位。