隨著電子行業(yè)技術(shù)的發(fā)展,特別是在傳輸接口方面,從PCI到PCI Express、從ATA到SATA、從并行ADC接口到JESD204、從RIO到Serial RIO等等,無(wú)一都證明了傳統(tǒng)并行接口的速度已經(jīng)達(dá)到瓶頸,取而代之的是速度更快的串行接口,于是原本用于光纖通信的SerDes 技術(shù)成為了高速串行接口的主流。串行接口主要應(yīng)用了差分信號(hào)傳輸技術(shù),具有功耗低、抗干擾強(qiáng),速度快的特點(diǎn),諸如PCI Express?(PCIe?)Gen4等串行鏈路接口的數(shù)據(jù)傳輸率將達(dá)到雙位千兆級(jí)傳輸速率。由此,器件建模、互連建模和分析方法必須不斷發(fā)展,以應(yīng)對(duì)不斷減小的設(shè)計(jì)余量和當(dāng)今工程師面臨的更具挑戰(zhàn)的合規(guī)標(biāo)準(zhǔn)。本系列文章將從各方面深入分析探討,為了降低風(fēng)險(xiǎn)并優(yōu)化設(shè)計(jì),將分析盡可能地推向上游至關(guān)重要,以實(shí)現(xiàn)權(quán)衡、可行性研究、元件選擇和約束獲取。

由于諸如PCI Express(PCIe)Gen 4等串行鏈路接口的數(shù)據(jù)傳輸率將達(dá)到雙位千兆級(jí)傳輸速率,器件建模、互連建模和分析方法必須不斷發(fā)展,以應(yīng)對(duì)不斷減小的設(shè)計(jì)余量和當(dāng)今工程師面臨的更具挑戰(zhàn)的合規(guī)標(biāo)準(zhǔn)。為了降低風(fēng)險(xiǎn)并優(yōu)化設(shè)計(jì),將分析盡可能地推向上游至關(guān)重要,以實(shí)現(xiàn)權(quán)衡、可行性研究、元件選擇和約束獲取。

鏈路中,SerDes發(fā)射器和接收器的均衡的精確建模對(duì)于獲得更好的仿真結(jié)果至關(guān)重要,這包括幾乎所有高數(shù)據(jù)速率串行鏈路中存在的復(fù)雜自適應(yīng)均衡。隨著過(guò)孔陣列需要全波3D的解決方案,以便通過(guò)過(guò)孔stub和耦合行為準(zhǔn)確地表征其復(fù)雜性,互連模型也面臨新的挑戰(zhàn),這可能會(huì)需要幾分鐘到幾小時(shí)或幾天的提取時(shí)間。仿真之后,經(jīng)常需要接口特定的后處理來(lái)檢查發(fā)射器、傳輸同道和接收器的合規(guī)性。

接下來(lái)將介紹創(chuàng)建串行鏈路預(yù)設(shè)計(jì)“虛擬原型”的方法,以及如何創(chuàng)建與之相關(guān)的互連和SerDes模型。我們將檢查如何使用IBIS-AMI模型,以及如何在沒(méi)有現(xiàn)有模型使用的情況下創(chuàng)建自己的模型。它還將向您展示最新的互連提取技術(shù),以便在控制計(jì)算時(shí)間的同時(shí)保證 “您需要的全波精度” ,以及如何使用基于標(biāo)準(zhǔn)的合規(guī)工具來(lái)自動(dòng)執(zhí)行布局后分析和高級(jí)接口驗(yàn)收,如 PCI Express Gen 4。

隨著數(shù)據(jù)速率的不斷加快和電源電壓的不斷減小,用于解釋邏輯的“單位間隔”或“UI”受到了明顯的壓縮。

各種PCI Express數(shù)據(jù)8'‘運(yùn)行通過(guò) FR4帶狀線

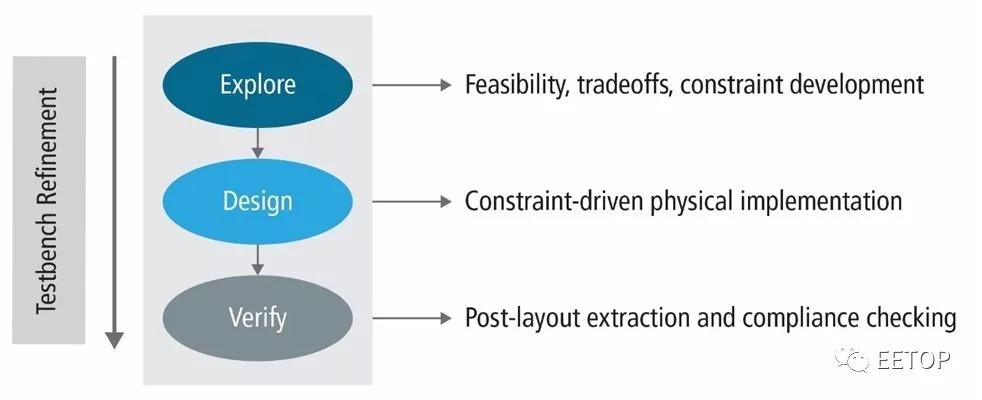

隨著工作空間越來(lái)越小,將信號(hào)完整性(SI)分析過(guò)程進(jìn)一步推向上游變得越來(lái)越重要,以便在設(shè)計(jì)過(guò)程中更早地定位問(wèn)題、應(yīng)對(duì)挑戰(zhàn),從而減輕流程后端的風(fēng)險(xiǎn)。這需要傳統(tǒng)方法的一些轉(zhuǎn)變,以及用于建模串行器/解串器或用于發(fā)送和接收高速信號(hào)的“SerDes”器件的新技術(shù)。這種前期的勞動(dòng)成果包括設(shè)計(jì)中優(yōu)化的材料清單(BOM),以及實(shí)現(xiàn)約束驅(qū)動(dòng)印刷電路板(PCB)物理布局過(guò)程的約束。結(jié)合高效的布局后互連提取和自動(dòng)化合規(guī)檢查,能夠確保給制造商驗(yàn)收您的設(shè)計(jì),沒(méi)有意外或進(jìn)度影響,并在硬件方面取得成功,同時(shí)避免昂貴又耗時(shí)的返工。

通過(guò)“自上而下”的方法將SI推向上游

成功實(shí)現(xiàn)能夠達(dá)到這些數(shù)據(jù)速率的關(guān)鍵因素之一是在傳統(tǒng)的布局后驗(yàn)證步驟中將SI分析起點(diǎn)更多地推向上游。這里有一個(gè)錯(cuò)誤的概念,在傳統(tǒng)的“自下而上”方法中,直到經(jīng)過(guò)詳細(xì)的PCB布局后才能進(jìn)行有意義的分析。然而在實(shí)際硬件設(shè)計(jì)環(huán)境中并非如此。

當(dāng)設(shè)計(jì)工程師完成layout后,通常有一兩天的時(shí)間,來(lái)自各個(gè)學(xué)科的工程師(機(jī)械、熱、信號(hào)完整性、電源完整性、EMI)可進(jìn)行最終檢查,為最后的layout提供一些改進(jìn)意見。但是,通常要承受來(lái)自項(xiàng)目經(jīng)理的巨大壓力,要在規(guī)定的時(shí)間段內(nèi)將Gerbers交給PCB制造商,而組裝廠將按序訂購(gòu)元件并接收這些裸板進(jìn)行裝配和測(cè)試,軟件工程師將會(huì)等待硬件進(jìn)入實(shí)驗(yàn)室,以便他們可以測(cè)試最新的軟件版本。換句話說(shuō),在PCB layout初步完成時(shí),供應(yīng)鏈依賴性的多米諾骨牌效應(yīng)將被完全捕獲于項(xiàng)目經(jīng)理的甘特圖中,而在這一點(diǎn)上執(zhí)行詳細(xì)SI分析的可用時(shí)間將很短。通常更可能的是,“運(yùn)行分析,直到時(shí)間耗盡,然后發(fā)貨”,而不是“運(yùn)行分析,直到您滿意,接口工作正常,然后發(fā)貨”。

為了在該P(yáng)CB設(shè)計(jì)流程的壓縮后端完成關(guān)鍵節(jié)點(diǎn)的簽收,準(zhǔn)備工作至關(guān)重要。一個(gè)策略是“自上而下”,提前于后期,建立一個(gè)早期版本的串行鏈路接口仿真測(cè)試臺(tái)。當(dāng)您初步了解用于發(fā)送和接收信號(hào)的SerDes和協(xié)議(例如PCI Express Gen 4)時(shí),可以在早期BOM階段開始從上游進(jìn)行詳細(xì)的原理圖設(shè)計(jì),這是解決系統(tǒng)分區(qū)、多少個(gè)PCB將用于構(gòu)建信號(hào)路徑、以及將用到什么樣的連接器的一般方法。系統(tǒng)中所有模塊的具體詳細(xì)模型在這個(gè)早期階段并不重要,最初可以使用 “現(xiàn)有模型占位” ,但是在了解更多詳細(xì)信息的情況下,它們將被替換(合規(guī)工具包是一個(gè)您搭建早期測(cè)試平臺(tái)所需前期模型的豐富來(lái)源,將在后續(xù)部分中介紹。)簡(jiǎn)而言之,如果您可以在餐巾紙上繪制接口,那么您應(yīng)該就能夠早日整合仿真測(cè)試平臺(tái)。這種自上而下的方法有很多好處:

可使您可視化整個(gè)系統(tǒng)和將被遍歷的信號(hào)路徑。

可以幫助您確定完成所有芯片間信號(hào)路徑連接所需的所有模型,以備用。

提前運(yùn)行一些步驟,使您可以提前搭建仿真測(cè)試平臺(tái),從而整個(gè)過(guò)程中的后續(xù)工作主要是更新拓?fù)渲械哪P汀⒏敿?xì)地重新運(yùn)行仿真。當(dāng)時(shí)間緊張時(shí),這個(gè)過(guò)程的后期可以節(jié)省大量的時(shí)間。

一般設(shè)計(jì)方法

隨著串行鏈路拓?fù)涞某跏荚屯負(fù)洌⑶腋鱾€(gè)模塊至少存在現(xiàn)有初始模型,您應(yīng)該擁有一個(gè)測(cè)試平臺(tái),用來(lái)仿真,并以目標(biāo)數(shù)據(jù)速率傳遞流量進(jìn)行分析。現(xiàn)在,在您的設(shè)計(jì)過(guò)程中,將逐漸開始使用更具體、更真實(shí)的模型替代初始模型。這些模型通常有以下幾類:

SerDes發(fā)射器和接收器的IBIS-AMI模型

分立器件的Spice模型(例如AC去耦電容)

封裝

PCB走線

PCB過(guò)孔

連接器

第一步是在拓?fù)渲懈髂K所需的模型以及在庫(kù)中的現(xiàn)有模型之間進(jìn)行差距分析。用現(xiàn)有模型增強(qiáng)測(cè)試平臺(tái),并驗(yàn)證仿真結(jié)果。接下來(lái),列出缺少的模型,聯(lián)系模型供應(yīng)商(可以是內(nèi)部的或者外部的),并提出模型需求。記錄聯(lián)系人、聯(lián)系日期和模型的狀態(tài)。當(dāng)您得到它們后,就可相應(yīng)地增強(qiáng)您的測(cè)試平臺(tái)了。

假設(shè)我們正在致力于PCI Express Gen 4串行鏈路的研發(fā),數(shù)據(jù)的傳輸速率為16Gbps。再假設(shè)我們能夠獲得供應(yīng)商提供的AC耦合電容、封裝和連接器的模型,以及來(lái)自SerDes接收端的IBIS-AMI模型。接下來(lái)還需要PCB的走線和過(guò)孔模型,以及發(fā)射端的IBIS-AMI模型。假設(shè)供應(yīng)商暫時(shí)無(wú)法提供這些數(shù)據(jù),那就讓我們先來(lái)解決PCB架構(gòu)的問(wèn)題吧。

PCB互連的預(yù)布局建模

PCB走線的建模可以從獲取層疊結(jié)構(gòu)開始,包括串聯(lián)鏈路差分對(duì)的材料、電介質(zhì)和導(dǎo)體厚度、阻抗、線寬以及間距。接下來(lái),需要確定串行鏈路(通常與接地層相鄰)的主要布線層,以便您可以生成適用的微帶線或帶狀線模型。有了這些信息,下一步就是估算互連的長(zhǎng)度。從這個(gè)層面上來(lái)講, “布局規(guī)劃” 或PCB的粗略布局是很有用的。您可以通過(guò)平面布局工具輸入基本的PCB輪廓、層疊結(jié)構(gòu),從封裝庫(kù)中提取部件,甚至可以定義一些簡(jiǎn)單的網(wǎng)絡(luò),所有這些都沒(méi)有一個(gè)正式的設(shè)計(jì)、完整的原理圖或網(wǎng)表。

布局規(guī)劃時(shí),不要忘記AC耦合電容。它們將被放置于電路板的頂層、在SerDes器件附近、還是與大部分其它分立元件一起位于電路板的背面?這種選擇會(huì)導(dǎo)致不同的過(guò)孔配置,所以在這一點(diǎn)上需要仔細(xì)考慮。在整個(gè)系統(tǒng)設(shè)計(jì)中,表面貼裝連接器也屬于這一類。

從平面布局中,找到串行鏈路的曼哈頓長(zhǎng)度作為初始的PCB長(zhǎng)度。將這些信息輸入到SI工具中,為PCB的主要布線生成一個(gè)W-element模型,并將其放入SI的仿真平臺(tái)。

提取平面布局的曼哈頓長(zhǎng)度進(jìn)行布線前的走線建模

對(duì)仿真平臺(tái)所需的其他走線模型也重復(fù)此過(guò)程,包括微帶線的扇出走線、連接到AC耦合電容任一側(cè)的走線等等。

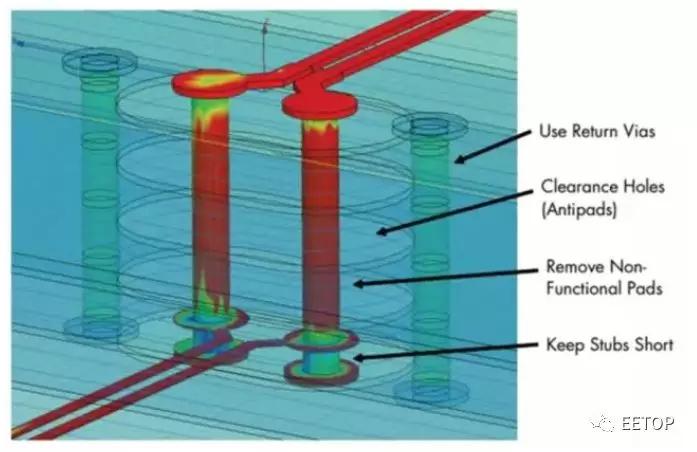

使用PCB上的通用走線模型后,我們將開始關(guān)注過(guò)孔。過(guò)孔是板上幾十或數(shù)千兆位串行鏈路的重要組成部分。它們通常代表整個(gè)信號(hào)路徑中最大的“速度突變點(diǎn)”,優(yōu)化這些過(guò)孔設(shè)計(jì)使其插損和回?fù)p最小,對(duì)高速率傳輸數(shù)據(jù)至關(guān)重要。在一些特殊情況下,可能通過(guò)僅有微帶線的布線消除過(guò)孔,但通常不會(huì)這樣做。高數(shù)據(jù)速率串行鏈路的過(guò)孔數(shù)量當(dāng)然應(yīng)該盡量減少,但通常無(wú)法被完全消除。

過(guò)孔不連續(xù)性“速度起伏”

鉆孔直徑、焊盤尺寸、反焊盤設(shè)計(jì)以及接地通孔都是設(shè)計(jì)中的關(guān)鍵因素。過(guò)孔的一個(gè)重要考慮因素是分支線長(zhǎng)度,或者說(shuō)是信號(hào)過(guò)孔的未使用部分,這可能引起信道中信號(hào)的反射。通過(guò)仔細(xì)選擇布線層、利用盲孔或背鉆等技術(shù)可以有效的控制分支線的長(zhǎng)度。

通過(guò)結(jié)構(gòu)參數(shù)進(jìn)行優(yōu)化

關(guān)鍵參數(shù)的自動(dòng)掃描可以顯著加快串行鏈路的過(guò)孔優(yōu)化設(shè)計(jì)。一旦確定了所需的過(guò)孔結(jié)構(gòu),就需要確認(rèn)并將其應(yīng)用在PCB的布線當(dāng)中。傳遞這些過(guò)孔設(shè)計(jì)參數(shù)的自動(dòng)化機(jī)制是非常有效的,可以確保它們?cè)谖锢聿季种邪凑疹A(yù)期實(shí)現(xiàn),成為“正確的設(shè)計(jì)”,并且使過(guò)孔對(duì)最終眼圖的影響最小化。

IBIS-AMI建模

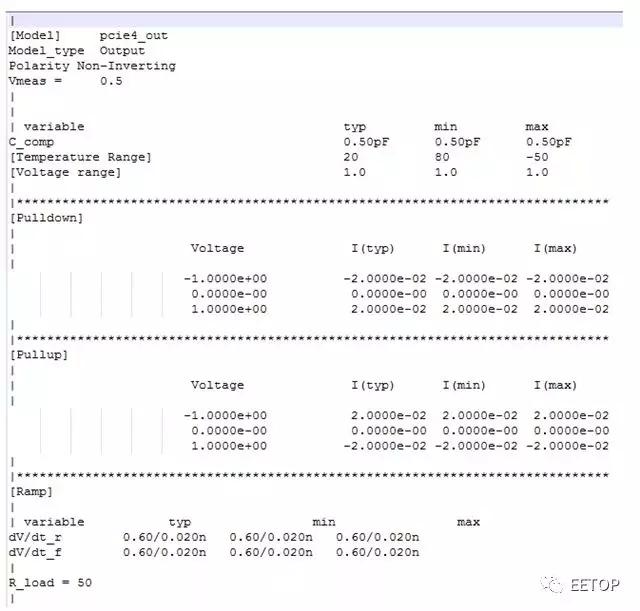

假設(shè)我們的PCIExpress Gen 4串行鏈路,使用初始的PCB走線和過(guò)孔模型,其余的缺失部分用于發(fā)射器的IBIS-AMI模型,“AMI”表示算法模型接口。正如其名,IBIS-AMI模型具有以傳統(tǒng)IBIS (I/O 緩沖區(qū)信息規(guī)范) 格式定義的“電路”部分和以AMI格式定義的“算法”部分。兩者都是完整模型所必需的。

該模型的電路或IBIS部分用于描述發(fā)射器的電壓擺幅、輸出阻抗、寄生效應(yīng)和上升/下降時(shí)間特性。這些信息應(yīng)該在您SerDes發(fā)送器的數(shù)據(jù)表中。假設(shè)數(shù)據(jù)表顯示,以50ohm作為參考阻抗,擺幅為1V,單端50歐姆輸出阻抗,0.5pF范圍內(nèi)的焊盤電容,以及20ps左右的單端上升/下降時(shí)間。采用一個(gè)標(biāo)準(zhǔn)的IBIS模型作為開始,是最直接的做法。

初步的IBIS模型

該算法(或模型的AMI部分)用于描述發(fā)射器的均衡行為。在PCI Express Gen 4的情況下,這由前向反饋均衡(FFE)或 “去加重”組成。FFE將包含多個(gè)“抽頭”,表示產(chǎn)生去加重行為的main和boost驅(qū)動(dòng)器,boost轉(zhuǎn)換位(例如0到1的轉(zhuǎn)換)和去加重穩(wěn)定狀態(tài)位(例如連續(xù)的多個(gè)1)。這些抽頭的作用大小通常用系數(shù)來(lái)表示,表示與主抽頭相比它們的比例系數(shù)。

含PCI Express預(yù)設(shè)的FFE和發(fā)射器波形

將上述信息作為輸入,現(xiàn)在的IBIS-AMI仿真工具通常包括直接生成AMI模型的功能。同樣,這些信息通常可以在SerDes發(fā)射器的數(shù)據(jù)表中找到。假如您感興趣的發(fā)射器使用與PCIExpress規(guī)范中描述的類似的去加重設(shè)置,可以使用如前所述的自動(dòng)化工具,利用上述的抽頭系數(shù)快速直接地生成AMI模型。

啟用約束驅(qū)動(dòng)設(shè)計(jì)

通過(guò)構(gòu)建預(yù)布局測(cè)試平臺(tái),填入相關(guān)模型,生成結(jié)果逼真的仿真結(jié)果,這時(shí)候正適合啟用約束來(lái)驅(qū)動(dòng)和控制串行鏈路的物理布局。這可能會(huì)導(dǎo)致測(cè)試平臺(tái)需要一些改進(jìn)和迭代,來(lái)添加更多的細(xì)節(jié),這是可預(yù)期的。此時(shí)的方法是參數(shù)化測(cè)試平臺(tái)的關(guān)鍵元素,掃描它們以量化其對(duì)整個(gè)接口性能的影響,并限制那些參數(shù)以確保我們的設(shè)計(jì)在完成時(shí)滿足合規(guī)要求。在PCI Express Gen 4的情況下,核心要求是眼圖高度至少為15mV,眼圖寬度為0.3UI(對(duì)于16Gbps的數(shù)據(jù)速率而言約為19ps),目標(biāo)誤碼率(BER)為1e-12。

那么掃描哪些類型的參數(shù)是有意義的?我們從SerDes器件開始,他們的電路模型中通常含有硅工藝/溫度/電壓(PVT)的快速和慢速Corner系數(shù),所以這方面應(yīng)該被覆蓋。如果您是PCB的設(shè)計(jì)人員,可能不一定會(huì)修改或控制它們,但是它們的影響應(yīng)該在掃描仿真中加以考慮,因?yàn)槟腜CB需要在那些條件下工作。另外,如果您能夠獲得SerDes的封裝模型,涵蓋互連寄生效應(yīng)的最小/最大范圍,那么也應(yīng)被包括進(jìn)去。連接器和AC耦合電容模型也是如此。

PCB互連從發(fā)射器開始工作,一直到接收器。如今的器件具有精細(xì)的引腳間距,為了從這些器件順利出線,通常需要縮小差分對(duì)的線寬和間距。因此這些變窄的幾何結(jié)構(gòu)一般會(huì)比電路板的主要部分產(chǎn)生更高的阻抗,因此會(huì)產(chǎn)生阻抗不連續(xù)性。扇出線應(yīng)該走多長(zhǎng)才不會(huì)出現(xiàn)問(wèn)題?這也需要在鏈路的接收端考慮。

一旦輸出到電路板的主要部分,就應(yīng)掃描差分對(duì)的線寬和間距,以達(dá)到PCB預(yù)期的阻抗容差范圍(通常+/- 10%)。而且,始終保持電路板上差分走線的間距不變可能是不切實(shí)際的。他們可能需要彼此分開,并短暫解耦以繞過(guò)障礙,甚至連接到AC耦合電容。這將改變差分對(duì)的特性阻抗。解耦線可以走多長(zhǎng)?電容引腳的escape走線可以走多長(zhǎng)?這對(duì)結(jié)果有嚴(yán)重影響嗎?

在哪里放置電容?發(fā)射端附近?接收端附近?位置有影響嗎?掃描位置信息可以量化這些影響。差分對(duì)正負(fù)引腳之間可以走多長(zhǎng)的線?布線長(zhǎng)度是否需要在layout中匹配到+/- 1 mil范圍內(nèi)?還是可以允許10或20mils的容差?請(qǐng)記住,弄清楚什么是無(wú)關(guān)緊要的與弄清楚什么是緊要的同樣重要。

串?dāng)_可能會(huì)對(duì)串行鏈路接口產(chǎn)生很大的影響。如果電路板上有足夠的空間,則可以方便地將約束用于差分對(duì)周圍,以產(chǎn)生足夠的間距,來(lái)解決串?dāng)_問(wèn)題。但是許多設(shè)計(jì)太密集以至于這種方法無(wú)法適用,這意味著其他信號(hào)到差分串行鏈路的間隔和耦合長(zhǎng)度也需要考慮并掃描。

鏈路的總長(zhǎng)度也是一個(gè)基本要素。SerDes器件的均衡設(shè)計(jì)是為了抵制有損互連,但是它們能夠做到的效果是有限的。需要確定的一個(gè)很重要的參數(shù)是:整個(gè)布線達(dá)到多長(zhǎng)時(shí)仍然可以生成符合規(guī)范的結(jié)果。

以下這些因素可能并不是需要考慮的約束的全部列表,但提供了一個(gè)好的開始:

扇出布線寬度、間距、長(zhǎng)度

主要布線層分配

額定的差分線寬度和間距

阻抗容差最大非耦合長(zhǎng)度

最大過(guò)孔數(shù)差分相位容差

AC耦合電容到發(fā)射端或接收端的最大長(zhǎng)度

整個(gè)串行鏈路布線的最大長(zhǎng)度

與其他信號(hào)的最小間距和最大耦合長(zhǎng)度(平行狀態(tài))

過(guò)孔結(jié)構(gòu)定義

將這些參數(shù)加入預(yù)布局測(cè)試平臺(tái)中,可以掃描這些參數(shù),并對(duì)其影響進(jìn)行量化。這項(xiàng)工作所交付的是一套現(xiàn)實(shí)的、可執(zhí)行的、量化的約束,可以導(dǎo)入到物理布局過(guò)程,并由layout設(shè)計(jì)人員使用自動(dòng)設(shè)計(jì)規(guī)則和電氣規(guī)則檢查(DRC/ERC)來(lái)控制關(guān)鍵串行鏈路接口的布局和布線。

Layout設(shè)計(jì)人員通常要求放松或修改初始的布線規(guī)則。這是很平常的,因?yàn)橛袝r(shí)候一些細(xì)微的修改可以使設(shè)計(jì)更加整潔和高效。而在預(yù)布局的測(cè)試平臺(tái)中,應(yīng)該可以很直接地調(diào)整一些參數(shù),重新掃描,并評(píng)估所需的改變是否會(huì)大大影響Margin。這個(gè)“協(xié)商” 過(guò)程可能會(huì)經(jīng)歷幾個(gè)迭代循環(huán),才能產(chǎn)生更好的成品。從SI的角度來(lái)看,最終目標(biāo)仍然是通過(guò)布線設(shè)計(jì)來(lái)完成最后的驗(yàn)證和合規(guī)性檢查,并產(chǎn)生可接受的Margin。

將約束加入layout以啟用約束驅(qū)動(dòng)設(shè)計(jì)

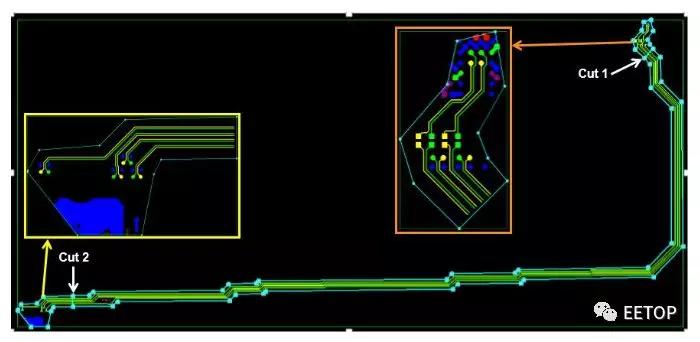

高效的互連提取

一旦物理layout完成(或者至少串行鏈路差分對(duì)的布線完成),就可以進(jìn)行布局后驗(yàn)證。需要決定使用多大的帶寬進(jìn)行模型提取。為了評(píng)估這一點(diǎn),需要考慮通過(guò)鏈路傳遞的信號(hào)。 PCI Express Gen 4的規(guī)格是指上升時(shí)間約為22ps,測(cè)量值為10%至90%。將上升時(shí)間與信號(hào)帶寬相關(guān)聯(lián)的經(jīng)典表達(dá)式是:

BW (GHz) =350 / Trise (ps)

對(duì)于PCI Express Gen 4來(lái)說(shuō),我們首先考慮的是至少16 GHz的信號(hào)帶寬,并且如果考慮均衡因素可能會(huì)更高。大多數(shù)工程師會(huì)堅(jiān)持?jǐn)?shù)倍于數(shù)據(jù)速率的最小帶寬,這樣就處于30至50 GHz的范圍內(nèi)。因此,為了精確,需要全波3D電磁場(chǎng)求解器,特別是針對(duì)復(fù)雜的非平面結(jié)構(gòu)(如耦合過(guò)孔)。所以最初的傾向是為這些類型的串行鏈路部署全波三維提取技術(shù)。

問(wèn)題在于計(jì)算的時(shí)間。正如前面所討論的那樣,在設(shè)計(jì)過(guò)程中,詳細(xì)的互連提取的關(guān)鍵在布線后。而設(shè)計(jì)周期的最后通常是最具時(shí)間挑戰(zhàn)性的,因?yàn)樾枰L(zhǎng)時(shí)間的計(jì)算。盡管從精確的角度來(lái)看復(fù)雜過(guò)孔結(jié)構(gòu)需要3D全波方法,但是對(duì)于長(zhǎng)而均勻的傳輸線,如PCB中的走線,就計(jì)算得太慢了。對(duì)于這些結(jié)構(gòu)來(lái)說(shuō),快速2D方法運(yùn)行效果還可以,所以在提取引擎方面存在一個(gè)基本沖突。

最有效的技術(shù)是將兩種方法結(jié)合起來(lái),為您提供“全方位的需求”,同時(shí)將更快、更簡(jiǎn)單的方法部署到長(zhǎng)而均勻的傳輸線結(jié)構(gòu)中。這通常被稱為“切割和縫合”方法,其中根據(jù)所發(fā)現(xiàn)的特定互連結(jié)構(gòu),將要提取的整個(gè)互連結(jié)構(gòu)分解成不同的區(qū)域。具有3D結(jié)構(gòu)的區(qū)域,如過(guò)孔,被標(biāo)記為全波引擎解決方案,而具有長(zhǎng)而均勻傳輸線的區(qū)域用2D技術(shù)解決。

將互連分成多個(gè)區(qū)域進(jìn)行切割和縫合

最終的結(jié)果組合成一個(gè)最終的S參數(shù),就像整個(gè)網(wǎng)絡(luò)都是由全波引擎提取的。這種技術(shù)的優(yōu)點(diǎn)是提供了全波精度,同時(shí),提供的解決方案時(shí)間比單用3D全波求解器提取整個(gè)網(wǎng)絡(luò)的時(shí)間要快一個(gè)數(shù)量級(jí)(或更多)。

此時(shí),可以將詳細(xì)的互連模型插回仿真測(cè)試平臺(tái)進(jìn)行布局后驗(yàn)證,取代預(yù)布局階段開發(fā)的PCB走線和過(guò)孔模型。

使用IBIS-AMI模型進(jìn)行仿真

此時(shí),SerDes元器件供應(yīng)商應(yīng)該已經(jīng)提供了所需的IBIS-AMI模型,如果這些模型可用,那么替換仿真測(cè)試平臺(tái)中的對(duì)應(yīng)模型。現(xiàn)在,我們重點(diǎn)關(guān)注后仿真的驗(yàn)證工作。在仿真測(cè)試平臺(tái)中替換為你自己的模型,盡管這時(shí)看起來(lái)你好像就馬上可以進(jìn)行仿真工作了,但是對(duì)于IBIS-AMI模型仍然有許多工作需要做。

如前所述,算法部分或者IBIS-AMI模型的“AMI”部分為SerDes的均衡功能。在雙沿?cái)?shù)據(jù)速率的工作情況下,SerDes均衡技術(shù)總是采用實(shí)時(shí)適應(yīng)的方法。為了模擬這種行為,AMI模型通常會(huì)有多個(gè)設(shè)置供用戶選擇,以便可以手動(dòng)調(diào)整均衡以獲得特定通道的最好驅(qū)動(dòng)。為了找到最佳的設(shè)置組合,通常把它當(dāng)做 “讀者的練習(xí)”,即SI工程師最好通過(guò)掃描多個(gè)組合以找出最佳值。

更高級(jí)的AMI模型會(huì)將部分或全部自適應(yīng)納入通道仿真中,從而更精確模擬實(shí)際硬件的行為。但即使使用這些類型的自適應(yīng)模型,仍然經(jīng)常需要檢查和優(yōu)化設(shè)置。例如,接收器的AMI模型包含連續(xù)時(shí)間線性均衡器(CTLE)、自動(dòng)增益控制器(AGC,有時(shí)稱為可變?cè)鲆娣糯笃骰騐GA)和判決反饋均衡器(DFE)。

接收器均衡

在這個(gè)特定的模型中,每個(gè)子模塊(CTLE,AGC和DFE)動(dòng)態(tài)調(diào)整其設(shè)置,因此您可能不需要手動(dòng)干預(yù)。使用默認(rèn)設(shè)置運(yùn)行時(shí),可觀察到以下內(nèi)容。

初始通道仿真結(jié)果

雖然眼睛睜開了,但CTLE、AGC和DFE系數(shù)的圖表顯示它們?cè)诜抡孢^(guò)程中并不真正收斂,并且持續(xù)反彈。初始設(shè)置使AGC模塊比CTLE模塊的適應(yīng)速度快兩倍。加快AGC適應(yīng)到4倍的CTLE適應(yīng)速度,可產(chǎn)生這些結(jié)果。

利用AGC更快的適應(yīng)性,您可以看到所有三個(gè)模塊(CTLE,AGC,DFE)的系數(shù)都已開始收斂。但收斂發(fā)生在約150,000位后。因此,將接收器AMI模型中的 “Ignore_Bits” 從40,000增加到150,000,這樣會(huì)從結(jié)果中刪除初始部分的仿真結(jié)果,這樣分析工具將評(píng)估收斂后的結(jié)果,就像在真實(shí)硬件中發(fā)生的那樣。這樣產(chǎn)生了如下結(jié)果。

融合接收器均衡設(shè)置

參數(shù),1e-12對(duì)應(yīng)的BER的眼高從40mV增加到85mV,提高了100%以上。

帶有收斂接收器均衡設(shè)置的結(jié)果

這說(shuō)明了一些使用高級(jí)AMI模型進(jìn)行仿真的細(xì)微之處。用戶仍然需要仔細(xì)閱讀模型提供商的文檔,了解可用的可調(diào)設(shè)置,并相應(yīng)地運(yùn)用它們。

反向信道訓(xùn)練

均衡器自適應(yīng)的另一項(xiàng)能力是反饋訓(xùn)練。許多高速串行協(xié)議規(guī)定SerDes接收器可以評(píng)估發(fā)射器送出的training patterns的信號(hào)質(zhì)量,以此來(lái)決定發(fā)射器均衡的大小,然后將這個(gè)要求反饋給發(fā)射器,然后評(píng)估下一個(gè)training pattern。這個(gè)過(guò)程會(huì)重復(fù)多次,直到接收器對(duì)發(fā)射器的設(shè)置滿意,那么這個(gè)滿意的設(shè)置就會(huì)被實(shí)際傳輸出去。

反向信道訓(xùn)練

盡管目前的IBIS標(biāo)準(zhǔn)還不支持反饋訓(xùn)練功能,但是已經(jīng)有一個(gè)相關(guān)的改進(jìn)提議BIRD147,在下一版本的IBIS規(guī)范中將加入該功能。

如下PCI Express Gen 4示例,使用或不使用反饋訓(xùn)練:

初始信道仿真結(jié)果

初始結(jié)果(紅色)顯示的是未啟用反饋。在這種情況下,發(fā)射機(jī)的AMI模型根據(jù)信道特性自行優(yōu)化其FFE抽頭系數(shù),而接收機(jī)AMI模型的適應(yīng)則在整個(gè)信道仿真過(guò)程中實(shí)時(shí)完成。第二個(gè)結(jié)果(綠色)顯示的是啟用反饋訓(xùn)練,并且清晰地生成一個(gè)睜得更大的眼圖。值得注意的是,如果您查看兩種情況下使用的FFE抽頭系數(shù)之間的差異,您將看到FFE系數(shù)在啟用反饋的情況下已被調(diào)低。如下顯示了前導(dǎo)抽頭系數(shù)如何在反饋訓(xùn)練中做自適應(yīng):

前導(dǎo)抽頭系數(shù)在反饋訓(xùn)練中的自適應(yīng)

在這里您可以看到,前導(dǎo)抽頭系數(shù)從絕對(duì)值約為0.16開始,然后在反饋訓(xùn)練過(guò)程中,根據(jù)接收機(jī)的判斷,將其降低到0.14的范圍。這使得接收機(jī)更先進(jìn)的均衡功能可以完成更多的“繁重工作”,并最終產(chǎn)生更好的整體效果。這顯示了在通道仿真過(guò)程中使用反饋功能,以及產(chǎn)生能夠精確模擬SerDes器件的行為的AMI模型的重要性。

自動(dòng)合規(guī)性檢查

有了詳細(xì)的布局后互連以及IBIS-AMI模型的正確執(zhí)行,您可以關(guān)注特定的、感興趣的接口(本例中為PCI Express Gen 4)的合規(guī)性檢查。

每個(gè)接口都有自己的特定標(biāo)準(zhǔn)。在這種情況下,PCI Express確定了許多眼圖相關(guān)的時(shí)域標(biāo)準(zhǔn)、無(wú)源互連通道的頻域標(biāo)準(zhǔn)以及滿足特定抖動(dòng)容限范圍的能力。

單獨(dú)評(píng)估這些標(biāo)準(zhǔn)可能會(huì)非常耗時(shí),特別是,如果需要多次運(yùn)行來(lái)掃描設(shè)計(jì)范圍和多個(gè)通道模型的情形。用于通用串行鏈路標(biāo)準(zhǔn)的自動(dòng)合規(guī)工具包通常會(huì)提供一些仿真工具,可幫助大幅加快合規(guī)性檢查速度并縮短簽收時(shí)間。

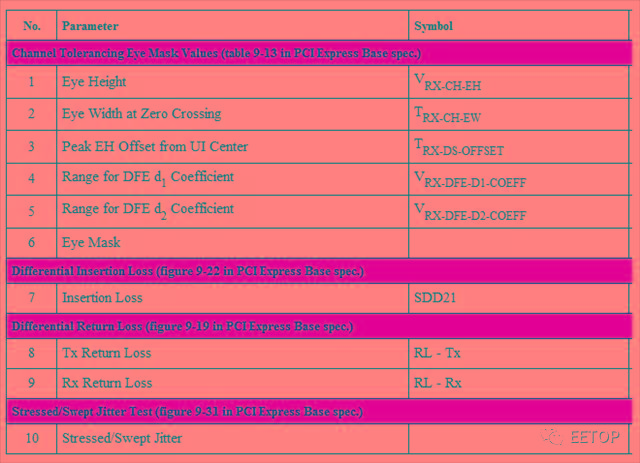

表1:PCI Express合規(guī)性檢查

自動(dòng)掃描關(guān)鍵參數(shù),并標(biāo)記合規(guī)性故障,可以更好地覆蓋您的串行鏈路設(shè)計(jì),并可幫助檢查您所關(guān)心的其他領(lǐng)域。

PCI Express合規(guī)性檢查結(jié)果

使用合規(guī)性工具包的另一個(gè)主要好處是能夠在預(yù)布局階段使用相關(guān)的模板。正如前面所討論的那樣,為可行性權(quán)衡建立早期測(cè)試平臺(tái)至關(guān)重要。但是在這個(gè)階段通常缺乏一些必要模塊的真實(shí)模型,有時(shí)需要使用“占位符”模型。隨自動(dòng)合規(guī)套件提供的模板通常會(huì)預(yù)先填充實(shí)際的拓?fù)浜湍P停òl(fā)射器和接收器的SerDes IBIS-AMI模型的規(guī)范級(jí)模型,并根據(jù)該特定標(biāo)準(zhǔn)的規(guī)范中描述的參考參數(shù)進(jìn)行構(gòu)建。這些模板以及與它們相關(guān)的模型為您的布局前測(cè)試平臺(tái)開發(fā)提供了一個(gè)很好的起點(diǎn),有助于最大限度地減少啟動(dòng)和運(yùn)行所需的時(shí)間,避免設(shè)計(jì)返工。

總結(jié)

兩位數(shù)的千兆數(shù)據(jù)速率的串行鏈路接口有其獨(dú)特的設(shè)計(jì)挑戰(zhàn)。從預(yù)設(shè)計(jì)階段開始,自上而下的分析方法可減輕相關(guān)風(fēng)險(xiǎn)、并可避免高代價(jià)、費(fèi)時(shí)間的重新設(shè)計(jì)。這項(xiàng)工作的成果是為了確定約束驅(qū)動(dòng)物理布局所需的布線規(guī)則。需要特別注意過(guò)孔結(jié)構(gòu)來(lái)控制插入損耗和回波損耗;將已知良好的過(guò)孔結(jié)構(gòu)導(dǎo)入布局的方法至關(guān)重要。需要IBIS-AMI模型來(lái)表示在這些數(shù)據(jù)速率下看到的自適應(yīng)均衡和反向信道功能,并且可以根據(jù)需求快速構(gòu)建規(guī)范。 “切割和縫合”(“Cut& stitch”)技術(shù)可以運(yùn)用在需要提取布線后互連提取,在獲得全波仿真精度的同時(shí),避免端到端全波3D提取的計(jì)算損失。自動(dòng)合規(guī)工具包可促進(jìn)串行鏈路設(shè)計(jì)的成功簽收,同時(shí)為預(yù)布局分析階段提供有價(jià)值的起點(diǎn)。