智能傳感器技術(shù)是一門(mén)正在蓬勃發(fā)展的現(xiàn)代傳感器技術(shù),是涉及微機(jī)械和微電子技術(shù)、計(jì)算機(jī)技術(shù)、網(wǎng)絡(luò)與通信技術(shù)、信號(hào)處理技術(shù)、電路與系統(tǒng)、傳感技術(shù)、神經(jīng)網(wǎng)絡(luò)技術(shù)、信息融合技術(shù)、小波變換理論、遺傳理論、模糊理論等多種學(xué)科的綜合技術(shù)。

智能傳感器中智能功能如:數(shù)字信號(hào)輸出、信息存儲(chǔ)與記憶、邏輯判斷、決策、自檢、自校、自補(bǔ)償都是以微處理器為基礎(chǔ)的。基于微處理器的傳感器從簡(jiǎn)單的數(shù)字化與信息處理已發(fā)展到了目前具有網(wǎng)絡(luò)通信功能、神經(jīng)網(wǎng)絡(luò)、模糊理論、遺傳理論、小波變換理論、多傳感器信息融合等新理論新技術(shù)逐步完善的現(xiàn)代智能傳感器。其微處理器硬件也經(jīng)歷了從單 CPU 結(jié)構(gòu)到多 CPU 甚至 DSP、ASIC 與 MCU 相混合的結(jié)構(gòu)。然而微處理器在可靠性、功耗、功能復(fù)用等多方面存在著與生俱來(lái)的一些不可克服的缺點(diǎn)與不足,阻礙了智能傳感器的進(jìn)一步發(fā)展。由系統(tǒng) IC 向 SOC(System on ChIP)轉(zhuǎn)變已成為歷史發(fā)展的必然趨勢(shì)。SOC 用硬件實(shí)現(xiàn)了以往軟件實(shí)現(xiàn)的功能。與一般 MCU 相比,它具有可靠性高、價(jià)格低、速度快、體積小、功能復(fù)用、保密性好等一系列優(yōu)點(diǎn)。傳統(tǒng)的 SOC 設(shè)計(jì)是以超深亞微米 IC 設(shè)計(jì)技術(shù)為基礎(chǔ)的,具有集成電路 ASIC 設(shè)計(jì)的復(fù)雜程度。隨著 SOC 平臺(tái)和 EDA 技術(shù)發(fā)展以及 IP 新經(jīng)濟(jì)模式的推動(dòng),在 SOC 應(yīng)用設(shè)計(jì)上越來(lái)越多的從傳統(tǒng)的硅片設(shè)計(jì)轉(zhuǎn)到利用大規(guī)模可編程的 FPGA 芯片設(shè)計(jì)。基于 FPGA 的 SOC 設(shè)計(jì)其開(kāi)發(fā)周期短、開(kāi)發(fā)工具及語(yǔ)言標(biāo)準(zhǔn)化、設(shè)計(jì)和器件無(wú)關(guān)等特點(diǎn),使得它與使用單片機(jī)一樣容易。大量的 FPGA 成功應(yīng)用的報(bào)道都是在圖像處理、電力系統(tǒng)等領(lǐng)域。在傳感器智能化領(lǐng)域上的應(yīng)用仍處于開(kāi)發(fā)研究階段。傳感器方面的少量應(yīng)用也僅限于用它作為一個(gè)或幾個(gè)獨(dú)立功能模塊,如:通信模塊、自補(bǔ)償模塊等都不具有系統(tǒng)的作用與功能,不能真正地成為片上系統(tǒng)(SOC)。本文將提出集采集系統(tǒng)、補(bǔ)償校正、數(shù)據(jù)處理、數(shù)據(jù)通信、任務(wù)調(diào)度、人機(jī)界面、IP 功能復(fù)用等功能模塊于一體的智能傳感器 SOC/IP 設(shè)計(jì)及基于 FPGA 與 ARM7 微處理器芯片的實(shí)現(xiàn)方法。

SOC/IP 概念與智能傳感器 SOC 設(shè)計(jì)方法

SOC:System on Chip 指建立在單芯片上的系統(tǒng)。IP: Intellectual Property 自主知識(shí)產(chǎn)權(quán)。傳統(tǒng)的智能傳感器設(shè)計(jì)方法是以功能設(shè)計(jì)為基礎(chǔ)的。而 SOC 設(shè)計(jì)方法以功能復(fù)用與搭建為基礎(chǔ),在芯片上用若干個(gè)宏模塊來(lái)構(gòu)建復(fù)雜系統(tǒng)。這些已經(jīng)開(kāi)發(fā)的宏模塊就是通用的 IP 核。IP 核的重用可以降低產(chǎn)品設(shè)計(jì)的復(fù)雜度,減少產(chǎn)品上市時(shí)間。

利用 SOC/IP 芯片能組成完整的智能傳感器系統(tǒng)。智能傳感器傳感參數(shù)可能是多種多樣的。但從功能模塊組成來(lái)講,它主要包括數(shù)據(jù)采集模塊、補(bǔ)償與校正模塊、數(shù)據(jù)處理模塊、數(shù)據(jù)網(wǎng)絡(luò)通信模塊、人機(jī)界面和任務(wù)管理與調(diào)度模塊等功能單元。從而基于 IP 的智能傳感器 SOC 設(shè)計(jì)過(guò)程為:首先正確建立智能傳感器的通用模塊模型;然后合理劃分各摸塊功能規(guī)范,制定各模塊之間的接口協(xié)議與標(biāo)準(zhǔn);再設(shè)計(jì)出一系列通用的 IP 核;最后把所需的通用 IP 核搭建整合在一起構(gòu)成完整的智能傳感器系統(tǒng)。

智能傳感器 IP 核設(shè)計(jì)與 SOC 構(gòu)建

智能傳感器涉及到數(shù)據(jù)采集、信號(hào)處理(程控放大、線(xiàn)性化、信號(hào)濾波、信號(hào)補(bǔ)償、人工神經(jīng)網(wǎng)絡(luò)、遺傳理論、多傳感器融合、模糊理論等) 、數(shù)據(jù)通信、人機(jī)界面及任務(wù)調(diào)度等各種功能。在 IP 核設(shè)計(jì)與 SOC 構(gòu)建中,為了簡(jiǎn)化工作,降低復(fù)雜度,我們選用基于 FPGA 的 IP 核及基于 ARM7TDMI-SCPU 的 IP 核兩種 SOC 設(shè)計(jì)方式,其中 FPGA 的 IP 核主要完成數(shù)據(jù)采集與信號(hào)處理模塊,基于 ARM7 的 IP 核完成數(shù)據(jù)通信、人機(jī)界面及任務(wù)調(diào)度工作。

數(shù)據(jù)采集

傳統(tǒng)的傳感器信號(hào)數(shù)字化大多采用的是 VFC、串行 A/D、并行 A/D 等方案。每一方案都可設(shè)計(jì)成相應(yīng)的 IP 核。雖然已經(jīng)有人用 FPGA 完成數(shù)據(jù)采集,但都是以特定應(yīng)用的方式,而不是以通用的 IP 核方式設(shè)計(jì)的。我們介紹采用 MAX125 完成的并行 A/D 接口 IP 核設(shè)計(jì)。MAX125 8 通道 14bit 的并行 A/D 芯片。在 FPGA A/D IP 核設(shè)計(jì)中,提供給 MAX125 信號(hào)有啟動(dòng)轉(zhuǎn)換及轉(zhuǎn)換結(jié)束后的時(shí)序信號(hào),讀取轉(zhuǎn)換結(jié)果并存儲(chǔ)到 FPGA 芯片內(nèi)部 RAM 中的數(shù)據(jù)信號(hào)。該 A/D IP 核我們已經(jīng)開(kāi)發(fā)成功,并獲得了很好的使用。

信號(hào)處理

信號(hào)處理是智能傳感器的主要內(nèi)容之一。通常包含線(xiàn)性化、濾波、各類(lèi)補(bǔ)償、人工神經(jīng)網(wǎng)絡(luò)、模糊理論、遺傳算法、多傳感器融合等工作。在濾波中,除了常規(guī)的 FFT、DFT 之外,近幾年還出現(xiàn)了小波變換。由于芯片速度上的優(yōu)勢(shì),如何實(shí)現(xiàn)各信號(hào)處理 IP 核通用化設(shè)計(jì),已成為相關(guān)信號(hào)處理算法 IP 核設(shè)計(jì)的關(guān)鍵。

如在線(xiàn)性化處理設(shè)計(jì)中,我們把各類(lèi)傳感器的線(xiàn)性化算法都設(shè)計(jì)到一個(gè)通用的線(xiàn)性化 IP 核中。在任務(wù)調(diào)用時(shí)再根據(jù)不同類(lèi)型傳感器線(xiàn)性化算法要求,組態(tài)選擇出相應(yīng)的算法 IP 核,供實(shí)際需要使用。

數(shù)據(jù)通信

設(shè)置數(shù)據(jù)通信接口主要是考慮芯片還可以同外部 CPU 或網(wǎng)絡(luò)構(gòu)成更加復(fù)雜的測(cè)控系統(tǒng)。為了方便芯片的設(shè)計(jì),節(jié)省芯片資源,我們選用基于 ARM7 的 philIPs LPC2106 芯片進(jìn)行通信 IP 核設(shè)計(jì)。它可以將一系列不同的通信接口(如: CAN、以太網(wǎng)、TCP/IP、RS232/485、I2C、SPI) 以及不同的通信規(guī)程用一個(gè)通用的微處理器實(shí)現(xiàn)。通過(guò)與上位機(jī)與各類(lèi)網(wǎng)絡(luò)的聯(lián)接,實(shí)現(xiàn)遠(yuǎn)程遙測(cè)、網(wǎng)絡(luò)遠(yuǎn)程智能測(cè)量節(jié)點(diǎn)等功能。通信 IP 核設(shè)計(jì)主要任務(wù)是通信規(guī)約算法設(shè)計(jì)。而大多數(shù)接口因?yàn)榛?ARM7 的微處理器都能提供,所以就不需要做太多的工作。

人機(jī)界面與任務(wù)調(diào)度

人機(jī)界面與任務(wù)調(diào)度 IP 核也用 ARM7 微處理器設(shè)計(jì)。人機(jī)界面主要設(shè)計(jì)鍵盤(pán)接口及 LCD/LED/CRT 等顯示接口。利用 ARM7 強(qiáng)大的 GPIO 功能是不難加以實(shí)現(xiàn)的。

任務(wù)調(diào)度 IP 主要包括數(shù)據(jù)采集調(diào)度、信號(hào)處理調(diào)度、數(shù)據(jù)通信調(diào)度及人機(jī)界面調(diào)度等工作。我們采用以源碼公開(kāi)的嵌入式操作系統(tǒng)μC/OS-Ⅱ2.52 版為基礎(chǔ),將它移植到 LPC2106 ARM 微處理器中。在μC/OS-Ⅱ嵌入式操作系統(tǒng)基礎(chǔ)上開(kāi)發(fā)各種應(yīng)用軟件,完成智能傳感器所需要的各類(lèi)任務(wù)調(diào)度與組態(tài)工作。

應(yīng)用舉例

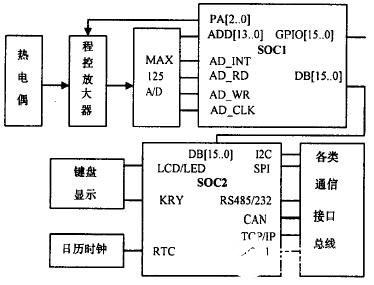

有了基本的 IP 內(nèi)核,我們就可以根據(jù)需要通過(guò)對(duì) IP 核的組態(tài)(在嵌入式操作系統(tǒng)μC/OS-Ⅱ的調(diào)度下)構(gòu)成各類(lèi)所需的智能傳感器系統(tǒng)。圖 1 所示是用于熱電偶溫度測(cè)溫的智能傳感器的 SOC 設(shè)計(jì)實(shí)例。所有算法 IP 模塊都加載到 ALTERA 公司的 APEX20K 的多芯片 FPGA 上,完成溫度信號(hào)采集、A/D 變換、低端補(bǔ)償、線(xiàn)性化、程控放大等功能。芯片的總體外部引腳包括 A/D 接口的數(shù)據(jù)線(xiàn)和控制線(xiàn)、微處理器接口的數(shù)據(jù)線(xiàn)和控制線(xiàn)、程控放大的控制線(xiàn)等。微處理器選用具有 ARM IP 核的 Philips 公司的 LPC2106 芯片。它完成通信功能、實(shí)時(shí)時(shí)鐘功能、人機(jī)接口功能及任務(wù)調(diào)度功能。通信 IP 包括 I2C 總線(xiàn)、RS232/RS485 總線(xiàn)、CAN 總線(xiàn)、TCP/IP 協(xié)議、以態(tài)網(wǎng)等。

圖 1 基于 IP 的智能傳感器的 SOC 設(shè)計(jì)

圖 2 是基于以上系統(tǒng)芯片構(gòu)成的熱電偶智能傳感器的組成框圖。其核心是兩片 SOC,其中 FPGA SOC 選用的是 APEX20K,MCU SOC 選用的是具有 ARM IP 核的 ARM7 TDMI-S 微處理器。該智能傳感器的樣機(jī)已經(jīng)完成。FPGA 的片上芯片經(jīng)硬件仿真測(cè)試,其 A/D 采樣、線(xiàn)性化算法、冷端溫度補(bǔ)償、多傳感器融合等功能與算法都已通過(guò)實(shí)驗(yàn)驗(yàn)證。MCU 的 SOC 在 48MHz 系統(tǒng)時(shí)鐘的運(yùn)行下,通過(guò)了通信、人機(jī)界面、實(shí)時(shí)日歷時(shí)鐘、任務(wù)調(diào)度管理等功能的實(shí)驗(yàn),驗(yàn)證了該設(shè)計(jì)的可行性。

圖 2 基于 SOC 芯片構(gòu)成的熱電偶智能傳感器的組成框圖

結(jié)束語(yǔ)

本文通過(guò)實(shí)例介紹了智能傳感器 IP/SOC 設(shè)計(jì)的方法。在設(shè)計(jì)通用智能傳感器 IP 核的基礎(chǔ)上,通過(guò) IP 復(fù)用,只需改變或重新設(shè)置數(shù)據(jù)與任務(wù)調(diào)用模塊就能設(shè)計(jì)出應(yīng)用于其他各類(lèi)智能傳感器的 SOC 系統(tǒng)。

由于 SOC 開(kāi)發(fā)及 EDA 設(shè)計(jì)工具的限制,以 FPGA 與 MCU 為基礎(chǔ),以實(shí)際系統(tǒng)應(yīng)用為切入點(diǎn),進(jìn)行智能傳感器的 SOC/IP 設(shè)計(jì)是符合當(dāng)前 SOC 設(shè)計(jì)和我國(guó)實(shí)際情況的研究方式。為了提高智能傳感器 SOC/IP 的設(shè)計(jì)能力,必須特別注意以下幾個(gè)方面的總結(jié)工作: ①EDA 工具:包括開(kāi)發(fā)工具、設(shè)計(jì)工具、分析工具以及驗(yàn)證工具。②HDL 語(yǔ)言工具:要充分利用 HDL 語(yǔ)言結(jié)構(gòu)好的特點(diǎn),采用自頂向下的模塊化設(shè)計(jì),強(qiáng)調(diào)詳細(xì)的配置和接口標(biāo)準(zhǔn)化。③IP 資源,一方面指充分利用現(xiàn)有通用 IP 的資源及資源標(biāo)準(zhǔn),如接口、規(guī)范、可測(cè)試性等,以及世界上市場(chǎng)份額占有率最大的 ARM 公司的 IP 核資源。另外一方面指智能傳感器本身 IP 核的總結(jié)與提高。

FPGA 的可現(xiàn)場(chǎng)編程特點(diǎn)使基于 SOC/IP 的智能傳感器設(shè)計(jì)更加靈活,各 IP 模塊并行處理的特點(diǎn)使以往用單一 CPU 無(wú)法實(shí)現(xiàn)的,如需要高速數(shù)據(jù)處理的傳感器校正算法、補(bǔ)償算法、神經(jīng)網(wǎng)絡(luò)傳感算法、模糊傳感算法、多傳感器融合等復(fù)雜算法得以實(shí)現(xiàn)。可進(jìn)一步提高測(cè)量精度、測(cè)量范圍與測(cè)量?jī)?nèi)容。同時(shí),用硬件實(shí)現(xiàn)以往軟件的功能,能解決干擾引起的程序死機(jī)問(wèn)題,極大地提高了智能傳感器系統(tǒng)的可靠性。