前不久的GTC 2021之上,老黃宣布英偉達(dá)很快將推出應(yīng)用于HPC AI的中央處理器Grace——基于Arm架構(gòu)。這在數(shù)據(jù)中心/服務(wù)器/基礎(chǔ)設(shè)施行業(yè)是個(gè)大新聞。

雖然去年到今年是Arm在各行各業(yè)大獲全勝的兩年,數(shù)據(jù)中心也頻繁出現(xiàn)Arm的身影——比如亞馬遜自研的Graviton2處理器基于Arm,富士通面向HPC的A64FX處理器基于Arm——這些在《Arm的十年P(guān)C征程,和微軟的“曖昧”》一文中就有所提及。

但英偉達(dá)在數(shù)據(jù)中心的分量,幾乎將Arm推到了最前線,多少有點(diǎn)兒很快就能把根植于該市場的x86拉下馬的意思。有關(guān)英偉達(dá)的Grace,很快我們會發(fā)表另一篇文章做單獨(dú)評論,即便個(gè)人認(rèn)為Grace著力的市場具有相當(dāng)強(qiáng)的針對性。本文嘗試呈現(xiàn),拋開Grace不談,Arm如今在服務(wù)器市場,究竟已經(jīng)發(fā)展到了何種程度。

Arm第一次認(rèn)真對待服務(wù)器市場

Arm一直以來就有突破移動(dòng)與嵌入式市場的野心,只不過就像Arm在PC之上的10年征程那樣,這個(gè)過程是需要不斷試錯(cuò)的。英偉達(dá)探索高性能CPU/SoC也不是今天才開始的,在10多年前英偉達(dá)就曾宣布過一個(gè)叫做Project Denver的項(xiàng)目,旨在與Arm合作面向HPC(高性能計(jì)算)市場推CPU產(chǎn)品。

不止是英偉達(dá),高通也曾推出基于Arm架構(gòu)的Centriq處理器,面向企業(yè)和服務(wù)器市場;Cavium的ThunderX此前也算是知名的Arm服務(wù)器芯片;還有博通的Vulcan,AMD的Opteron A1100……雖然它們中的大部分都失敗了。感覺從這些項(xiàng)目初期展示的PPT來看,Intel早就應(yīng)該縮在墻角顫抖了。但事實(shí)上,Arm在這一領(lǐng)域始終沒能真正走入主流視野(雖然Arm一直宣稱自己是“基礎(chǔ)設(shè)施(infrastructure)”設(shè)備中市場份額最高的,包含路由器、交換機(jī)、基站、服務(wù)器等)。

到近代鯤鵬920這類服務(wù)器芯片面世,以及如今相當(dāng)活躍的Ampere Computing也在推基于Arm的服務(wù)器處理器,Arm才真正在這一領(lǐng)域逐漸像樣起來。今年的GTC主題演講上,黃仁勛也宣布,英偉達(dá)的GPU開始和Ampere Computing、亞馬遜、聯(lián)發(fā)科等合作伙伴的CPU/SoC搭配,從云到邊緣到消費(fèi)終端。雖然在接受采訪時(shí),黃仁勛說Grace并不會多大程度影響到現(xiàn)有客戶,但這明擺著就有拆AMD/Intel墻角的意思。

Arm在服務(wù)器、基礎(chǔ)設(shè)施,或者說數(shù)據(jù)中心產(chǎn)品的試錯(cuò)歷史就不多做回顧了。事實(shí)上,Arm過去雖然也一直有試探服務(wù)器市場的意思,但他們始終都沒有面向這些數(shù)據(jù)中心的基礎(chǔ)設(shè)施,推過專門的IP——Arm在該市場的IP,基本與面向消費(fèi)市場的IP共享。

這一點(diǎn)其實(shí)是無可厚非的,大部分芯片制造商的同代核心IP,面向不同市場都會做較大程度的共享。但這也表現(xiàn)出Arm此前針對基礎(chǔ)設(shè)施設(shè)備并沒有明晰、像樣的市場規(guī)劃,這對生態(tài)構(gòu)建本來就是不利的。

轉(zhuǎn)機(jī)出現(xiàn)在2018年,這一年10月份的TechCon上,Arm正式宣布推出Neoverse系列IP,面向服務(wù)器市場,從云到邊緣。與此同時(shí)還公開了未來3年的產(chǎn)品路線圖,如上圖所示。Arm Neoverse可以理解為服務(wù)器版的Arm Cortex。

這張圖列出了一年一迭代的Neoverse版本,比如2019年代號為Ares的處理器核心IP,也就是Neoverse N1。Arm最早的時(shí)候宣布,未來每年迭代都將實(shí)現(xiàn)30%的性能提升——聽起來比旁邊的Cortex系列平均增速要快些,也比競爭對手更快。后來的發(fā)布會上,Arm又宣布N1性能提升,實(shí)際相比2018年的Cosmos高出了60%(不過Cosmos據(jù)說并不指代一個(gè)專門的架構(gòu)),是原目標(biāo)的2倍提升——基于SPEC2017整形測試(SPECspeed2017_int_base)。到今年發(fā)布的N2,提升速度似乎又超預(yù)期了,后文還將探討更具體的微架構(gòu)變化。

2019年2月份,Arm正式宣布推出Neoverse N1與E1平臺——這應(yīng)該是Arm對服務(wù)器市場改朝換代的開始。

當(dāng)然光換個(gè)名字肯定是沒用的,此前多篇探討Arm發(fā)展史的文章中,我們都談到了近代Arm的核心IP,在保持低功耗特性的前提下,在高性能方面也有了突破。即便一般的芯片制造商無法做到蘋果M1那種程度,高通驍龍8cx也已經(jīng)有了應(yīng)用于PC的可行性。起碼如今這個(gè)時(shí)代,和10年前英偉達(dá)Project Denver時(shí)代(Cortex-A15時(shí)代)還是有根本差別的。

2018年這一年,Arm向市場推出Cortex A76核心IP,這應(yīng)該是眾所周知的了——高通面向PC所推的驍龍8cx就應(yīng)用了Cortex A76微架構(gòu)。次年問世的Neoverse N1實(shí)際上就屬于Cortex A76微架構(gòu)的變體,或者說基于Cortex A76。

Austin家族微架構(gòu)(選讀)

這兩者都來自Arm奧斯汀設(shè)計(jì)中心,都屬于Austin家族微架構(gòu),基于ARMv8指令集。事實(shí)上Cortex與Neoverse后續(xù)更新版本,包括Cortex A78、Neoverse V1應(yīng)當(dāng)都屬于Austin家族,今年預(yù)計(jì)要推向市場的新一代Neoverse Poseidon才會采用全新的微架構(gòu)。

Neoverse V1和Cortex A76一樣都采用4-wide取指/解碼,11級管線深度,可在需要時(shí)縮減至9級。前端、后端的區(qū)別都不大。

兩者區(qū)別比較大的部分主要在存儲、連接方面——作為服務(wù)器處理器,這也是必然的。L1-I cache做到硬件級別的完全一致性(coherency),這屬于面向虛擬環(huán)境性能的改進(jìn)。L2新增1MB可選大小(A76是512KB),針對存儲敏感型應(yīng)用。

存儲層級結(jié)構(gòu)發(fā)生了比較大的變化。N1 CPU是連接到mesh網(wǎng)絡(luò)之上的,即CMN-600(CMN-600是Arm最早于2016年發(fā)布的SoC互聯(lián)IP,全稱叫coherent mesh network;如上圖所示,連接中間經(jīng)過了CAL以及mesh網(wǎng)絡(luò)的XP交叉點(diǎn);每個(gè)CAL層至多連接2個(gè)N1——即兩核為一簇)。在Arm的參考設(shè)計(jì)中,后續(xù)再連接到系統(tǒng)級緩存——SLC(system level cache)slice,每簇2MB,參考設(shè)計(jì)64核N1總共64MB SLC。

這張圖來自Wikichip,結(jié)構(gòu)描繪上更為清晰

N1去掉了L3和DSU(DynamIQ Shared Unit)的監(jiān)聽過濾(snoop-filter)邏輯,CPU核心直接連接到CMN的CHI接口。這樣一來內(nèi)存控制器和CPU核心之間的通訊,只需要經(jīng)過mesh網(wǎng)絡(luò)。這好像也屬于服務(wù)器CPU的標(biāo)配。

7nm工藝也是與上述設(shè)計(jì)內(nèi)容配套的,核心面積整體上還是很小。另外,Neoverse N1一個(gè)比較大的變化是最高頻率往上提了,發(fā)布時(shí)是說達(dá)到3.1GHz,電壓也需相應(yīng)提高,提供更高的單線程性能——頻率提高19%,實(shí)際上需要44%的功耗為代價(jià),這也很能表現(xiàn)Arm在頻率與功耗的關(guān)系上,并沒有什么魔法。亞馬遜Graviton2就是基于Neoverse N1的芯片,CPU核心頻率只選擇了2.5GHz。

基于消費(fèi)級產(chǎn)品提升頻率,和Intel、AMD這種傳統(tǒng)服務(wù)器CPU供應(yīng)商的思路就不同了:x86市場的這兩名玩家,其服務(wù)器CPU微架構(gòu)也與消費(fèi)CPU共享,但服務(wù)器CPU卻是拉低核心頻率的。這與雙方在消費(fèi)市場的定位還是有很大關(guān)系的。

不過即便是這樣,功耗還是有優(yōu)勢,Arm此前宣稱64核的N1參考設(shè)計(jì)總功耗大約為105W;Arm公開其64核參考設(shè)計(jì)SPECint_rate2006吞吐測試得分1310分,整數(shù)延遲得分(SPECint2006)37分,還是能夠表現(xiàn)Arm能效方面的優(yōu)勢的。

對于networking和存儲服務(wù)器,Arm推薦8-32核N1設(shè)計(jì),TDP 25-65W;類似5G基站邊緣端側(cè)設(shè)備,16-64核目標(biāo)設(shè)計(jì),TDP 35-105W;對于超大規(guī)模數(shù)據(jù)中心而言,N1目標(biāo)設(shè)計(jì)64-128核,TDP >150W。

Arm的Neoverse N1平臺參考設(shè)計(jì)64核心,外加前面提到的CMN-600 mesh網(wǎng)絡(luò)和64MB SLC緩存。臺積電7nm工藝制造64核N1參考設(shè)計(jì)的die size已經(jīng)快要接近400mm?了,Arm也因此推薦chiplet那樣的設(shè)計(jì),chiplet die之間通過CCIX互聯(lián)來通訊。

另外Neoverse N1平臺設(shè)計(jì)中,可集成SmartNIC——加速網(wǎng)絡(luò)連接還是如今實(shí)現(xiàn)數(shù)據(jù)中心高吞吐的重要因素(看看英偉達(dá)現(xiàn)在都在宣傳些啥)。CMN-600可連一些固定功能加速IP。通過CCIX連接第三方IP,可實(shí)現(xiàn)存儲一致性。更多特性不再列舉,屬于服務(wù)器RAS、安全等相關(guān)的。

Arm服務(wù)器CPU的效率現(xiàn)在怎么樣?

早前的Arm服務(wù)器處理器IP核心不夠主流,很大程度上在于性能和效率都不怎么樣。硬件層面的性能和功耗表現(xiàn),是爭奪這塊市場的基本要求。

能了解服務(wù)器CPU性能的渠道不多,像亞馬遜Graviton2這種芯片都還是亞馬遜自用的。不過隨Arm這兩年在服務(wù)器市場的活躍,像AnandTech這樣的外媒也開始把性能測試觸及到了服務(wù)器、基礎(chǔ)設(shè)施處理器產(chǎn)品之上。

事實(shí)上,2018年Cavium的ThunderX2被AnandTech認(rèn)為是這一領(lǐng)域,Arm平臺首次可與Intel、AMD相提并論的處理器產(chǎn)品。此后亞馬遜Graviton處理器的出現(xiàn)也表明,Arm處理器是可以成為服務(wù)器領(lǐng)域的主流的。

除了亞馬遜Graviton2,在Neoverse N1實(shí)施方案中,比較具有代表性的應(yīng)該是Ampere Computing最新的 Altra產(chǎn)品線。去年的Altra Q80-33就是用來對標(biāo)Intel、AMD在服務(wù)器市場的高端產(chǎn)品的。

Altra Q80-33主頻最高3.3GHz,80核心;CMN-600 mesh互聯(lián),每核心L2選配1MB,以及32MB SLC——每核心分配到的SLC可能少了點(diǎn)。I/O以及更高的系統(tǒng)層面就不做介紹了,Ampere打造的Mount Jade,2-socket 2U機(jī)架服務(wù)器,有興趣的可以去查一查外圍的配置。

值得一提的是,這顆處理器的TDP標(biāo)250W,實(shí)際上它并不是指常規(guī)負(fù)載的平均功耗,而是峰值狀態(tài)下的平均功耗。其實(shí)際功耗大部分情況下低于250W,AnandTech認(rèn)為按照Intel、AMD的標(biāo)法,Altra Q80-33的TDP應(yīng)該在200W左右。

與之對應(yīng),Intel前不久剛剛發(fā)布的Ice Lake-SP至強(qiáng)處理器,高配型號的TDP 270W(最高配8380為40核心,十代酷睿的Sunny Cove架構(gòu));AMD上個(gè)月推代號Milan的EPYC處理器,TDP 280W(最高配64核心,Zen 3架構(gòu))。如果光從高配版處理器的售價(jià)來看,Ampere Altra的性價(jià)比還是高出了一大截的。

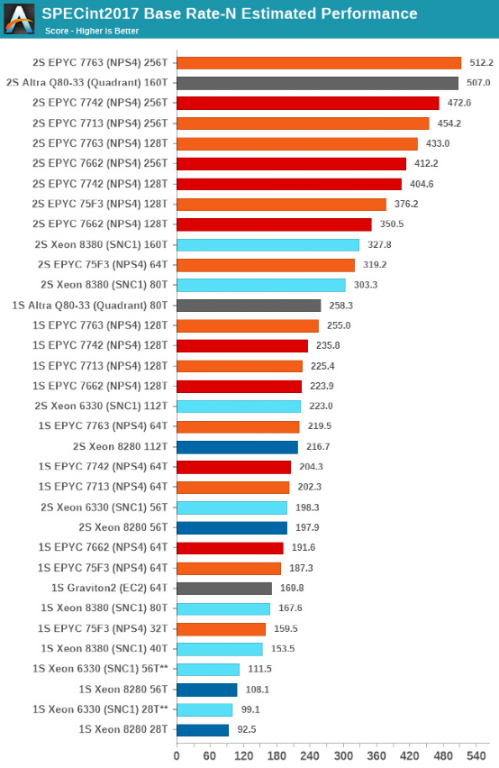

AnandTech最近剛剛測試了Ice Lake-SP,參測的還包括AMD Milan、Ampere Altra,以及亞馬遜Graviton2。測試項(xiàng)分成多線程性能(SPECint2017/SPECfp2017 Base Rate-N)、單線程性能(SPEC2017 Rate-1)、每核心性能(針對per core licensing)、JAVA性能(SPECjbb MultiJVM)、LLVM編譯、NAMD性能。有興趣的可前往了解,這里就不列出具體的成績了(因?yàn)槠颍蠄D只列出了整數(shù)多線程性能/單線程性能)。

單看x86平臺,自從AMD Zen 2問世以來,Intel至強(qiáng)處理器在性能上表現(xiàn)出了全方位的乏力。上一代AMD EPYC和Intel至強(qiáng),在性能上拉開了比較大的差距。這一代Intel稍稍趕上了一些,但在旗艦產(chǎn)品上,整體仍然存在差距。Intel現(xiàn)在愈發(fā)強(qiáng)調(diào)系統(tǒng)性能,從自身包括存儲、軟件優(yōu)化等方面的優(yōu)勢,彌補(bǔ)CPU本身的弱勢,所以AnandTech的測試可能仍然是比較片面的。而且今年下半年規(guī)劃中的Sapphire Rapids會很快上線。這是題外話了。

基于Arm Neoverse N1的Ampere Altra是能夠和AMD上一代Rome架構(gòu)64核的EPYC打得有來有回的。Neoverse在每核性能上還是與x86平臺有差距;此外Altra在存儲敏感型測試中的表現(xiàn)并不怎么樣,與其cache配置相關(guān)(以及可能與mesh互聯(lián)有關(guān));另外Ampere在整體系統(tǒng)方案上,雙socket擴(kuò)展還是不能和Intel/AMD比。不過偏算力的負(fù)載場景下,Altra更多的核心則有優(yōu)勢;能效方面,如前所述相比x86平臺有功耗方面的顯著優(yōu)勢。

特別值得一提的是,Arm平臺的服務(wù)器處理器還存在價(jià)格上的顯著優(yōu)勢。與此同時(shí),Ampere今年還計(jì)劃推一款A(yù)ltra-Max,采用128個(gè)Neoverse-N1核心,屬于Arm設(shè)計(jì)目標(biāo)頂配。

雖說以Ampere Altra為代表的Arm處理器仍在性能表現(xiàn)的某些方面不及x86(主要是AMD),但已經(jīng)真正意義上對x86的服務(wù)器市場構(gòu)成相當(dāng)嚴(yán)肅的威脅了。

需要指出的是,加強(qiáng)生態(tài)構(gòu)建是Arm的當(dāng)務(wù)之急,不管是與軟硬件合作伙伴加強(qiáng)合作,還是制定規(guī)范。在前兩年發(fā)布Neoverse之時(shí),Arm還發(fā)布了ServerReady合規(guī)認(rèn)證計(jì)劃,幫助用戶做Arm服務(wù)器系統(tǒng)的安全、合規(guī)部署。

Neoverse N2與V1的發(fā)布

GTC大會上,英偉達(dá)表示Grace CPU會采用新一代的Neoverse架構(gòu),但沒說具體是什么架構(gòu)。按照計(jì)劃表,去年9月份,Arm發(fā)布了新一代的Neoverse架構(gòu)。除了N1迭代N2,這次新加了一個(gè)V系列:代號Zeus的Neoverse V1。

Neoverse V1是基于Cortex X1的性能向微架構(gòu)。和Cortex X1一樣,在PPA三者的指針上,Neoverse V1也更偏向性能,部分犧牲了功耗和面積。所以其設(shè)計(jì)方向和N系列是存在差別的。因此V1有著更大的cache、核心結(jié)構(gòu)。Arm的數(shù)據(jù)提到,V1相比N1有著50%的IPC提升,在這個(gè)時(shí)代下還是相當(dāng)巨量的,實(shí)際產(chǎn)品提頻過后要在每核性能上擊敗x86應(yīng)該已經(jīng)不是問題了。

另外V1會成為首個(gè)支持SVE(Scalable Vector Extension)的Arm核心。此前富士通的A64FX已經(jīng)率先做出這方面的支持,V1的SIMD單元寬度是A64FX的一半。除此之外,V1也引入了Bfloat16格式支持。

而N1迭代款的N2則持續(xù)專注于PPA均衡發(fā)展,與Neoverse N2對應(yīng)的Cortex家族微架構(gòu)還未發(fā)布,N2代號為Perseus。據(jù)說去年年底Arm就開始做N2架構(gòu)的授權(quán)了。N2的目標(biāo)設(shè)計(jì)最高攝心術(shù)已經(jīng)達(dá)到了192W,且TDP增至350W。這應(yīng)該是也是堆料的突破,英偉達(dá)的Grace CPU是極有可能應(yīng)用N2這個(gè)方案的。

AnandTech猜測,Neoverse N2可能會應(yīng)用ARMv9指令集+SVE2支持。另外,原本規(guī)劃中今年要推出的代號為Poseidon的5nm芯片預(yù)計(jì)會延后至明年。如今Neoverse的規(guī)劃已經(jīng)在有序推進(jìn)了。即便沒有英偉達(dá),Arm玩轉(zhuǎn)數(shù)據(jù)中心市場似乎也是早有預(yù)謀的,而英偉達(dá)顯然會成為這一行動(dòng)的助推器。