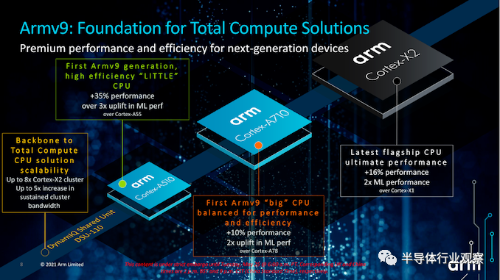

在上個月Arm發(fā)布了最新基礎(chǔ)架構(gòu)Neoverse V1和Neoverse N2 CPU IP之后,現(xiàn)在是時候該討論Arm在客戶端和移動方面的進展了。今年,Arm的情況比往常要大得多,因為我們看到了面向移動設(shè)備和客戶端的三種新一代微體系結(jié)構(gòu):旗艦級Cortex-X2內(nèi)核,以Cortex-A710形式亮相的新A78后續(xù)產(chǎn)品,還有名為Cortex-A510的全新小核心。

這三個新CPU構(gòu)成了Armv9兼容設(shè)計的新三重奏,旨在標(biāo)志著行業(yè)中很少出現(xiàn)的更大的體系結(jié)構(gòu)/ ISA轉(zhuǎn)換。

除了新的CPU內(nèi)核外,我們還看到了新L3和群集設(shè)計——DSU-110,Arm還通過新的緩存一致性CI-700網(wǎng)狀網(wǎng)絡(luò)和NI-700NoC IP對其互連IP進行了重大升級。

Cortex-X2,A710和A510是去年X1,A78和A55的后續(xù)產(chǎn)品。特別是對于新的Cortex-X2和A710,它們是其前代產(chǎn)品的直接微體系結(jié)構(gòu)后繼產(chǎn)品。這些部分在迭代改進IPC和效率的同時,還以Armv9和新擴展(例如SVE2)的形式結(jié)合了全新的體系結(jié)構(gòu)功能。

Arm的新小核心Cortex-A510是一個更大的微體系結(jié)構(gòu)跳躍,因為它代表了Arm的Cambridge CPU設(shè)計團隊的一項新的CPU設(shè)計。A510在改進IPC的同時仍繼續(xù)關(guān)注功率效率,并且也許最有趣的是,它保留了其有序的微體系結(jié)構(gòu)特征。

Armv9 CPU系列:僅用于所有實際目的的AArch64 *

新的CPU系列標(biāo)志著我們多年來最大的體系結(jié)構(gòu)飛躍之一,因為該公司現(xiàn)在將所有三個新CPU IP都基于Armv9.0。早在三月下旬,我們就廣泛地介紹了新Arm架構(gòu)的細(xì)節(jié)。新ISA的基礎(chǔ)功能包括新注冊的先前可選/缺失的Armv8.2 +功能,這些功能在移動和客戶端設(shè)計中無法得到保證(主要是由于較舊的A55內(nèi)核),以及引入了新的SVE2 SIMD和矢量擴展。

我們期待已久的一大變化是,在即將到來的Arm Cortex-A移動內(nèi)核中,我們將看到32位AArch32執(zhí)行模式的棄用。自從Google在2019年宣布Google Play商店將要求上傳64位應(yīng)用程序以來,我們就一直在為32位應(yīng)用程序倒計時。該公司也將于今年夏天晚些時候停止向64位兼容設(shè)備提供32位應(yīng)用程序,

盡管Arm宣布這一轉(zhuǎn)變將在2023年發(fā)生,但就所有意圖和目的而言,明年大多數(shù)全球用戶都已經(jīng)在發(fā)生這種轉(zhuǎn)變。Cortex-X2旗艦內(nèi)核和Cortex-A510小內(nèi)核都是僅限AArch64的微體系結(jié)構(gòu),它們不再能夠執(zhí)行AArch32代碼。

話雖如此,信心的讀者可能會注意到,三分之二的CPU并不是一個完整的轉(zhuǎn)變,其原因是因為Cortex-A710實際上仍然支持AArch32。Arm表示,這樣做的原因主要是為了滿足中國移動市場的需求,因為中國移動市場缺乏全球Play商店市場的同類生態(tài)系統(tǒng)功能,中國供應(yīng)商及其國內(nèi)應(yīng)用程序市場需要更多時間來促進向僅64位轉(zhuǎn)變。這意味著明年我們將有一個奇怪的情況,那就是只有SoC能夠在其中級內(nèi)核上執(zhí)行32位應(yīng)用程序,而這些應(yīng)用程序被降級到A710內(nèi)核中級,而錯過了A510內(nèi)核的小功率效率或X2內(nèi)核的性能。

在核心方面,新的Cortex-X2和Cortex-A710是Cortex-X1和Cortex-A78的后繼產(chǎn)品。這兩種設(shè)計大多由ARM奧斯汀的設(shè)計團隊設(shè)計的,從多年前的A76算起,新產(chǎn)品代表了這個微架構(gòu)系列的第四代產(chǎn)品。在Arm借助明年的新Sophia內(nèi)核將其移交給全新設(shè)計之前,這些內(nèi)核應(yīng)該是該微體系結(jié)構(gòu)家族中的最后一個,

在設(shè)計理念上,X2和A710總體上保持了X1和A78所定義的總體目標(biāo):X系列繼續(xù)致力于通過增加微體系結(jié)構(gòu)來提高性能,并且Arm愿意在合理的范圍內(nèi)折衷功率。同時,A710繼續(xù)致力于通過更智能的設(shè)計來提高性能和效率,并著重于最大化IP的功率,性能和面積(PPA)平衡。

在上一張幻燈片中,Arm提出的重點是優(yōu)化了關(guān)鍵路徑(critical paths)和物理設(shè)計,以實現(xiàn)持續(xù)的電壓運行,這更多是該公司在下一代“Middle”內(nèi)核中追求的目標(biāo),而不是在Cortex-A710中專門體現(xiàn)的目標(biāo)……

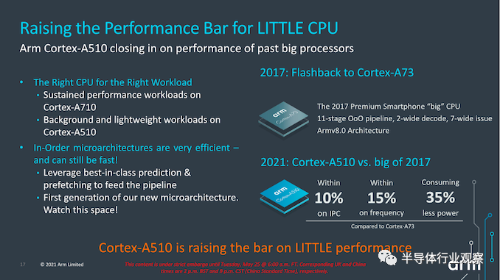

今年,我們也終于看到了一個新的小核心。我們早在2017年就介紹了Cortex-A55,自那時以來我們還沒有看到對Arm的小內(nèi)核的任何更新,以至于它被視為最后幾代移動SoC的重大弱點。

全新的Cortex-A510是Arm劍橋設(shè)計團隊的clean-sheet 設(shè)計,它利用了公司較大內(nèi)核中已采用的許多技術(shù),但將這些技術(shù)實施到了新的有序(in-order)小型微體系結(jié)構(gòu)中。是的,我們?nèi)栽谟懻撚行騼?nèi)核,而Arm仍將其視為提取移動設(shè)備最佳效率和“使用天數(shù)”的最佳選擇。

盡管這是一個有序內(nèi)核,但Arm進行了比較,認(rèn)為新設(shè)計與2017年的旗艦內(nèi)核Cortex-A73非常相似,實現(xiàn)了非常相似的IPC和頻率功能,而功耗卻要低得多。

新設(shè)計還采用了非常有趣的共享復(fù)雜方法,并與第二個內(nèi)核共享了L2和FP / SIMD pipelines,一個被Arm稱為“合并內(nèi)核”(merged core)的設(shè)計方法,這無疑會讓讀者想起十年前AMD在推土機內(nèi)核中使用的CMT方法 ,即使在方法上有非常重要的差異。

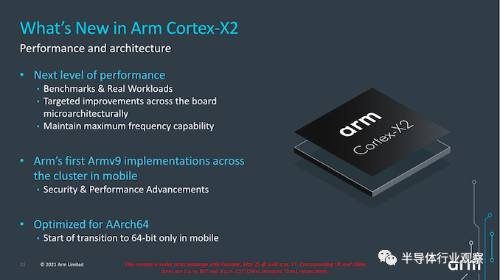

Cortex-X2:更高的性能,更深的OoO

我們首先從去年的Cortex-X1的繼承者Cortex-X2開始。

X1是Arm推出的新IP系列產(chǎn)品中的第一款產(chǎn)品,在這個系列面世后,Arm將其“大”核心產(chǎn)品分成了兩個不同的IP產(chǎn)品線,其中Cortex-A兄弟繼續(xù)了Arm最初的PPA設(shè)計理念,而X系列則被允許為了實現(xiàn)更高的性能點而不斷發(fā)展壯大。

Cortex-X2延續(xù)了這一理念,并進一步擴大了其與“Middle”同類產(chǎn)品Cortex-A710之間的性能和功耗差距。我還注意到,在Arm的整個演講中,都提到了將Cortex-X2用于大屏幕計算設(shè)備和筆記本電腦等外形尺寸中的情況,因此這很可能表明該公司的這一代產(chǎn)品,將被應(yīng)用在上述場景的產(chǎn)品設(shè)計中。

從體系結(jié)構(gòu)的角度來看,X2與X1自然不同,這在很大程度上要歸功于它對Armv9的支持以及該體系結(jié)構(gòu)的新基準(zhǔn)化所帶來的所有安全性和相關(guān)的ISA平臺改進。

如簡介中所述,Cortex-X2還是僅64位內(nèi)核,即使在PL0用戶模式應(yīng)用程序中,也僅支持AArch64執(zhí)行。從微體系結(jié)構(gòu)的角度來看,這很有趣,因為這意味著Arm將能夠消除設(shè)計中的某些缺陷。但是,由于該設(shè)計是Austin處理器系列的延續(xù),因此,我想知道我們是否會在未來的 “clean-sheet” 大內(nèi)核設(shè)計中看到這種棄用的更多好處,因為從一開始就設(shè)計了僅AArch64。實際上,這是Arm的其他CPU內(nèi)核中已經(jīng)發(fā)生的事情,因為新的小內(nèi)核Cortex-A510設(shè)計為sans-AArch32。

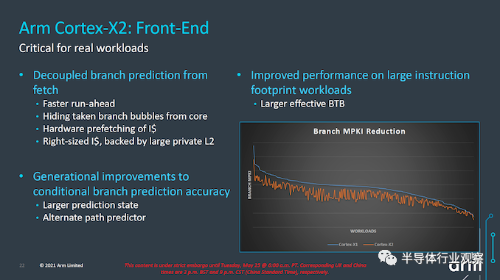

在前端方面,Arm一直在嘗試改進其認(rèn)為微體系結(jié)構(gòu)最重要的方面:分支預(yù)測。這包括繼續(xù)以與獲取階段分離的方式運行(run the branch resolution in a decoupled way)分支分辨率(branch resolution),以使這些功能塊能夠在錯誤預(yù)測的情況下領(lǐng)先于內(nèi)核的其余部分運行,并最大程度地減少分支氣泡( branch bubbles)。Arm通常不愿就其預(yù)測變量在這里進行過多少改動而談?wù)撎嗉?xì)節(jié),但希望在新的X2和A710內(nèi)核的分支預(yù)測準(zhǔn)確性方面取得顯著改善,從而有效地降低了MPKI(Misses per kilo instructions)指標(biāo),以應(yīng)對非常廣泛的工作負(fù)載。

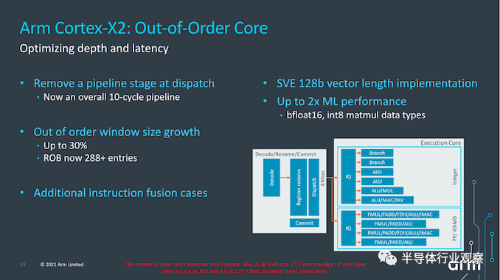

由于Arm能夠?qū)ispatch stages從2個周期減少到1個周期,因此新的核心總體上將其pipeline長度從11個周期減少到10個周期。需要注意的是,我們必須將pipeline cycles與mispredict penalties分開來,在大多數(shù)情況下,后者在Cortex-A77設(shè)計中已減少到10個周期。移除pipeline stage通常是一個相當(dāng)大的變化,特別是考慮到Arm的目標(biāo)是保持內(nèi)核的頻率能力。這種設(shè)計變更確實招致了一些更復(fù)雜的工程,并且具有面積和功耗成本。但是盡管如此,正如Arm所解釋的那樣,削減pipeline stage仍然可以帶來更大的投資回報,從而帶來績效收益,因此非常值得。

內(nèi)核還增加了亂序功能,這一代產(chǎn)品還將ROB(reorder buffer)從224個條目增加了30%,增加到288個條目。有效數(shù)字實際上還要高一點,因為在壓縮和指令捆綁的情況下,實際上存儲了超過288個條目。Arm說,這一代產(chǎn)品還促進了更多的指令融合案例。

在核心的后端,F(xiàn)P / ASIMD pipelines的一部分有了新的重大變化,這些 pipelines現(xiàn)在支持SVE2。在移動市場,SVE向量長度將繼續(xù)為128b,本質(zhì)上,新的X2內(nèi)核具有與X1的4x FP / NEON流水線相似的吞吐量特性。之所以選擇128b向量而不是更高的向量是因為在big.LITTLE設(shè)計中需要具有統(tǒng)一的體系結(jié)構(gòu)特征,因為您不能在同一SoC中以無縫方式混合不同向量長度的微體系結(jié)構(gòu)。

在后端,Cortex-X2繼續(xù)致力于通過將load-store窗口和結(jié)構(gòu)大小增加33%來提高MLP (memory level parallelism) )。Arm在這里采用了幾種結(jié)構(gòu),且通常不會詳細(xì)說明已擴展了哪些隊列,但是一旦我們拿到了X2系統(tǒng),就很可能能夠?qū)Υ诉M行衡量。L1 dTLB已從40個條目(entries)增加到48個條目,并且與每一代一樣,Arm還改進了其預(yù)取器(prefetchers),提高了準(zhǔn)確性和覆蓋范圍。

Prefetchers是今年早些時候在Cortex-X1和A78上使我們驚訝的一個設(shè)計,這是我們在行業(yè)中認(rèn)識到的同類產(chǎn)品中的第一個。這能夠鎖定到任意重復(fù)的內(nèi)存模式上,并識別內(nèi)存訪問中的新迭代,從而能夠智能地預(yù)取整個模式直至一定深度(我們估計為32-64MB的窗口)。Arm表示,現(xiàn)在覆蓋范圍以及準(zhǔn)確性都得到了進一步的提高,盡管只有在接觸到芯片之后,我們才能再次看到這些細(xì)節(jié)。

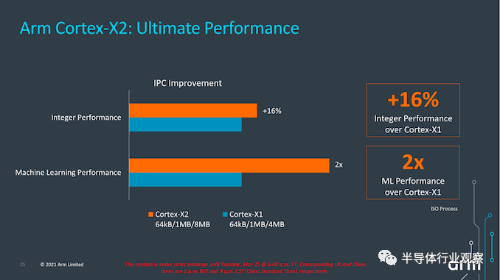

就IPC的改進而言,在SPECint2006中,ISO頻率在今年數(shù)字達(dá)到了+ 16%。該度量標(biāo)準(zhǔn)的問題(并且適用于今天所有Arm的數(shù)據(jù))是Arm將8MB L3緩存設(shè)計與4MB L3設(shè)計進行了比較,因此我希望+ 16%的數(shù)字中的較大部分是由于較大緩存而不是核心IPC自身進行改進。

就他們而言,Arm重申他們希望明年的X2 SoC使用8MB L3設(shè)計,因此,這個+ 16%的數(shù)字是現(xiàn)實的,這是用戶在實際實現(xiàn)中應(yīng)該看到的。但是話雖這么說,我們?nèi)ツ赀€是就Arm期望用于X1 SoC的8MB L3緩存進行了相同的討論,而Exynos 2100和Snapdragon 888都沒有采用。因此我們還是看最終商用的旗艦SoC將采多大的高速緩存。

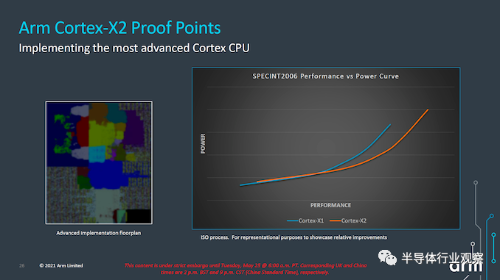

在性能和功耗曲線方面,新的X2內(nèi)核在這兩個指標(biāo)上都超越了X1。盡管峰值性能點的確增加了16%的性能,但這確實要付出更高的功耗。

通常,考慮到我們現(xiàn)在在市場上看到的有關(guān)處理供應(yīng)商的節(jié)點選擇的情況,這有點令人擔(dān)憂。我們已經(jīng)看到,高通公司和S.LSI在Snapdragon 888和Exynos 2100中使用的三星5LPE節(jié)點在性能和能效方面的交付不足,我通常認(rèn)為這兩個大核的功耗都較高限制散熱。我認(rèn)為高通公司在下一代產(chǎn)品中將繼續(xù)使用三星代工廠,因此,我對采用旗艦級SoC的任何節(jié)點(無論是5LPP還是4LPP)在功率改進方面都持悲觀態(tài)度。明年我們可能看不到實際SoC的全部+ 16%改善,這很有可能是合理的。

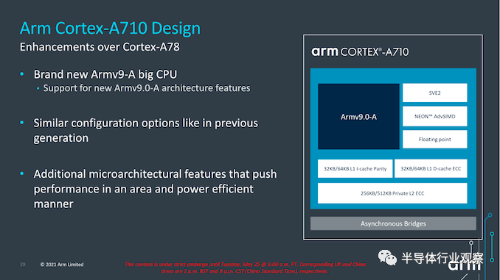

Cortex-A710:性能更高,效率更高

正如前面介紹,Cortex-X2在提供全面性能的同時,要付出功耗和面積上的損失,但Arm的Cortex-A710設(shè)計卻采用了更有效的方法。

首先,就Arm未來的發(fā)展而言,現(xiàn)在新產(chǎn)品的命名是顯而易見了的,他們跳過了A79的名稱,只是簡單地從A710的新的三位數(shù)方案開始。這在公司宏偉計劃中逼哥不是很重要,但卻是有趣的營銷方式。

與X2一樣,Cortex-A710是Armv9內(nèi)核,具有新體系結(jié)構(gòu)版本附帶的所有新功能。與X2不同,A710還支持EL0 AArch32執(zhí)行,并且如介紹中所述,這主要是因應(yīng)中國市場客戶要求所做的的設(shè)計選擇。因為在中國市場,生態(tài)系統(tǒng)將所有應(yīng)用程序遷移到AArch64方面仍然略有滯后。

在前端增強方面,我們看到了與X2相同的分支預(yù)測改進,具有更大的結(jié)構(gòu)和更好的準(zhǔn)確性。其他結(jié)構(gòu)(例如L1I TLB)也已從32個條目增加到48個條目。其他前端結(jié)構(gòu)(例如macro-OP cache )在1.5K條目處保持不變(X2在3K條目處也保持不變)。

A710中核的一個非常有趣的選擇是Arm將macro-OP cache和dispatch stage的吞吐量從6-wide降低到5-wide。這主要是針對這一代產(chǎn)品的有針對性的功率和效率優(yōu)化,因為我們看到Cortex-A和Cortex-X內(nèi)核之間在其專業(yè)性和性能和功耗的目標(biāo)用例方面存在更大的分歧。

Dispatch stage還具有與X2相同的優(yōu)化功能,從流水線中刪除了1個周期,從而實現(xiàn)了整個10周期的pipeline設(shè)計。

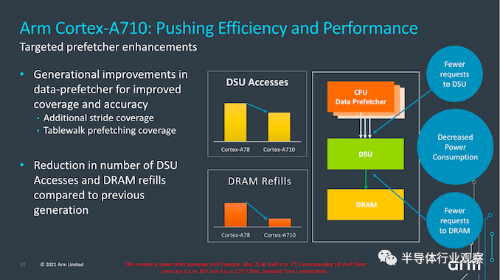

Arm還專注于影響系統(tǒng)非核心部分的核心改進,這要歸功于預(yù)取器設(shè)計的新改進以及它們?nèi)绾闻c新的DSU-110交互。內(nèi)核和DSU的新組合能夠減少從內(nèi)核到L3緩存的訪問時間,并且由于效率更高的預(yù)取器和更大的L3緩存而減少了昂貴的DRAM訪問。

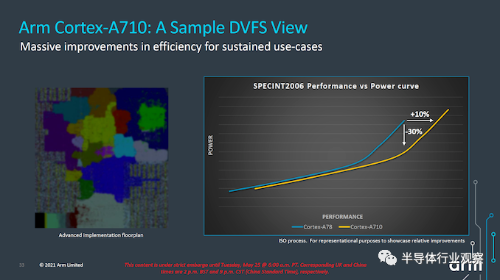

在IPC方面,Arm宣傳了10%的提升,但是這里出現(xiàn)的數(shù)字又是我們將8MB L3緩存設(shè)計與4MB L3緩存設(shè)計進行了比較。雖然這可能會與明年的旗艦SoC進行比較,因為Cortex-A710還是可用于中端或低端SoC(可能使用較小的L3緩存)的內(nèi)核,但我們不太可能看到這樣的IPC提升,除非實際的SoC確實能夠改善其DSU尺寸。

比性能提高+ 10%更為重要的是,當(dāng)稍微降低頻率時,我們可以看到功耗降低幅度可能很大。據(jù)Arm稱,在性能相同的情況下,A710的功耗比Cortex-A78少30%。這將大大有助于Cortex-A710的時鐘頻率適中的“中間”核心實現(xiàn)的持續(xù)性能和電源效率。

總的來說,X2和A710的性能和功率指標(biāo)都相當(dāng)適中,使其成為我們在Arm幾年中看到的最小的一代又一代的數(shù)字。Arm解釋說,由于這一代隨著向Armv9的遷移而進行了較大的體系結(jié)構(gòu)更改,因此對我們在前幾代中看到的通常的效率和性能改進產(chǎn)生了影響。

X2和A710都是該奧斯汀微體系結(jié)構(gòu)家族的第四代產(chǎn)品,因此我們正面臨著不斷減少的收益和成熟的設(shè)計壁壘。幾年前,我們給人的印象是,奧斯汀家族只能進行三代的工作,然后再將其移交給Sophia團隊的全新clean-sheet設(shè)計,但是原來的路線圖已經(jīng)改變,現(xiàn)在我們將期待明年的Sophia新核心在性能上能有更大的飛躍。

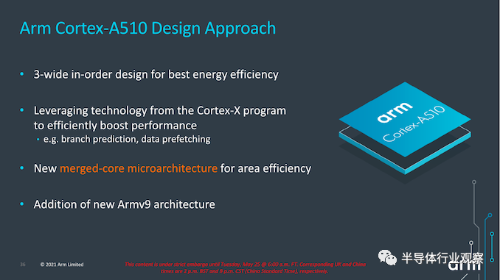

Cortex-A510:全新的小巧設(shè)計

接下來,我們將介紹Arm最新的小內(nèi)核,即全新的Cortex-A510。新設(shè)計是工程師在過去4年中一直在研究的Arm劍橋團隊開發(fā)的一種clean-sheet的微體系結(jié)構(gòu),它在將小內(nèi)核內(nèi)置到SoC中時標(biāo)志著一種截然不同的方法。

首先,Arm明確指出了設(shè)計繼續(xù)使用有序執(zhí)行,并指出他們認(rèn)為這仍然是為此類工作負(fù)載設(shè)計內(nèi)核的最省電方式。當(dāng)將其置于蘋果自己亂序的效率核心的上下文中時,這仍然是一個相對有爭議的話題和討論點,我稍后將再次討論該話題。

其次,Cortex-A510引入了一種稱為“合并核心”(merged-core)的微體系結(jié)構(gòu),這與AMD十年前在其Bulldozer內(nèi)核中對CMT所做的一些非常高的比較和相似之處,但是在某些重要方面卻有很大不同。細(xì)節(jié)和設(shè)計方面。

當(dāng)然,與X2和A710一樣,A510是Armv9設(shè)計,并且所有三個內(nèi)核彼此共享相同的架構(gòu)功能,從而可以將它們集成到同一SoC中。值得注意的是,與X2一樣,A510是僅64位的AArch64內(nèi)核。

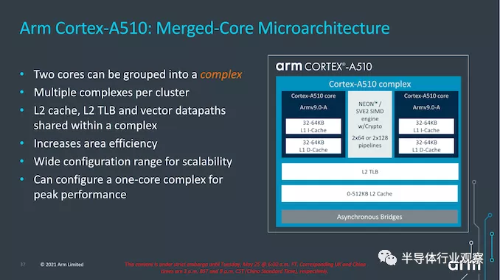

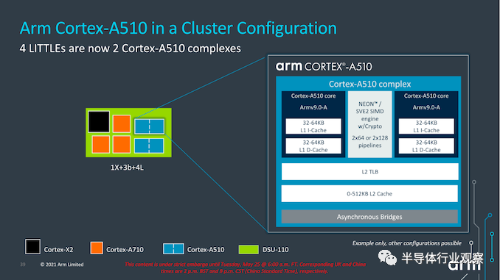

Cortex-A510最有趣的方面是新的合并核心方法。Arm在這里所做的事情是創(chuàng)建一個新的“復(fù)雜”,最多兩個核心對,它們共享L2緩存系統(tǒng)以及它們之間的FP / NEON / SVE pileline。

乍一看,這聽起來與AMD使用Bulldozer和CMT(Clustered Multithreading)方法所做的極為相似,但是Arm的設(shè)計在實際內(nèi)核共享方面更加分散。AMD的CMT模塊主要由兩個整數(shù)后端和一個FP / SIMD后端之間的共享前端組成,而Arm的“合并核心”實際上是具有各自前端,中核,整數(shù)后端和L1緩存層次結(jié)構(gòu)。“核心”之間共享的唯一內(nèi)容是實際的FP / SIMD后端以及L2緩存層次結(jié)構(gòu)。

此外,雖然我們希望在移動市場中,供應(yīng)商能夠在每個復(fù)雜方法中使用這兩個新的合并核心,但實際上有可能僅在每個復(fù)雜中僅使用一個核心。在這種情況下,獨立核心將本質(zhì)上具有其自己的專用(非共享)資源,但是與預(yù)期的合并核心方法相比,其區(qū)域效率顯著降低。

通常,考慮到采用SVE2以及新執(zhí)行后端所需的相對較大的占位面積,為這些微小的新內(nèi)核實際共享這些資源是很有意義的。它們的典型工作負(fù)載也大多僅為整數(shù)綁定后臺工作負(fù)載,這對此類單元造成的壓力較小。

從更高級別的SoC角度來看,內(nèi)核數(shù)量并沒有真正改變,細(xì)節(jié)是我們將看到兩對或小的內(nèi)核現(xiàn)在彼此之間共享更大的L2緩存。該L2最多可配置為512KB,但一如既往,我們在產(chǎn)品中實際看到的內(nèi)容將很大程度上取決于供應(yīng)商要在其設(shè)計中實現(xiàn)的內(nèi)容。由于新的綜合系統(tǒng)也僅占用DSU上的單個接口,因此也為大于8個“核心”的設(shè)計提供了可能性,我希望這種情況不會發(fā)生,或者希望僅通過更多的中型或大型核心發(fā)生。

就新A510的前端而言,我們看到了一個128位的fetch pipeline ,這意味著它每個周期最多可以獲取4條指令,這給前端留出了一些余地來關(guān)閉分支氣泡。解碼器的實際寬度已從2寬增加到3寬。

在分支預(yù)測方面,一如既往Arm并未透露太多細(xì)節(jié),但該公司確實指出,它在大型核上使用了相同的最新方法和技術(shù)。L1指令高速緩存可以是32KB或64KB。

就共享向量執(zhí)行后端而言,這實際上非常有趣,因為Arm可以選擇使用較小的2x64位流水線或2x128b流水線配置復(fù)雜系統(tǒng),后者的吞吐量將是Cortex-A55的2倍。我不太確定將與哪些移動設(shè)備供應(yīng)商合作;我們始終希望有更大的配置,但一如既往,我們將不得不拭目以待,看看實際產(chǎn)品中將采用什么配置。在這兩種配置中,向量長度均為128b,因為這是大型核心微體系結(jié)構(gòu)互操作性的要求。

Arm指出,Shared pipelines對硬件是完全透明的,并且還使用了細(xì)粒度的硬件調(diào)度。在同時使用兩個內(nèi)核的實際多線程工作負(fù)載中,與為每個內(nèi)核專用的pipeline相比,性能影響和不足僅占百分之幾。這基本上是為什么Arm決定使用這種面積更有效的合并核心方法的基石論據(jù)。

盡管這是一個有序的體系結(jié)構(gòu),但Arm仍然擴展了Cortex-A510的后端,該后端現(xiàn)在包括3個ALU,一個復(fù)雜的MAC / DIV單元和一個分支轉(zhuǎn)發(fā)端口。這里的解釋很簡單,當(dāng)有適當(dāng)?shù)闹噶钚蛄幸獔?zhí)行時,就有更多的機會在更少的周期內(nèi)執(zhí)行更多種類的代碼塊。

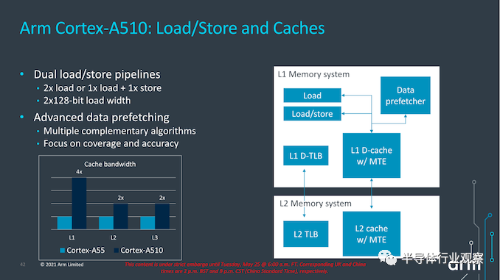

最后,在負(fù)載存儲系統(tǒng)中,與Cortex-A55相比,新結(jié)構(gòu)得到了極大的改進,因為我們看到了從負(fù)載和存儲管道向負(fù)載和負(fù)載/存儲管道的轉(zhuǎn)變,這有效地使存儲結(jié)構(gòu)增加了一倍。每個周期執(zhí)行的負(fù)載數(shù)。管道的寬度也增加了,從64b的寬度增加了一倍,達(dá)到128b的寬度,因此與Cortex-A55相比,負(fù)載帶寬實際上增加了三倍。

A510還采用了我們在其他最近的大型Arm內(nèi)核中已經(jīng)看到的類似的非常先進的預(yù)取器設(shè)計,并增加了該內(nèi)核能夠?qū)崿F(xiàn)的巨大性能改進。

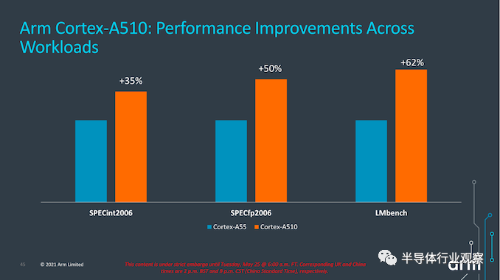

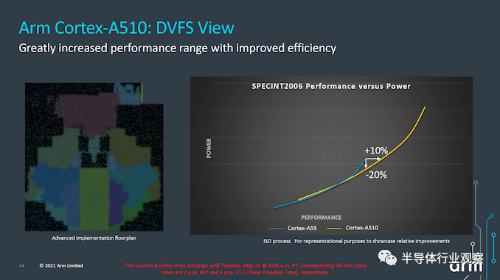

在性能指標(biāo)方面,就像在X2和A710演示幻燈片上一樣,A510的數(shù)字也不盡相同。據(jù)說兩個核心之間的頻率是相同的。在這種情況下,我們看到SPECint2006中的+ 35%和SPECfp2006中的+ 50%,這似乎是非常可靠的世代改進,但是考慮到緩存層次結(jié)構(gòu)的差異以及我們將得分與4年以上進行比較的事實從舊的核心來看,實際的改進,尤其是從復(fù)合年均增長率(CAGR)來看,似乎并沒有那么令人印象深刻。

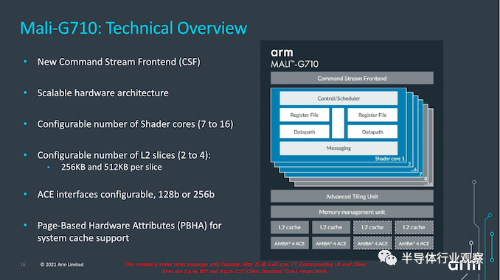

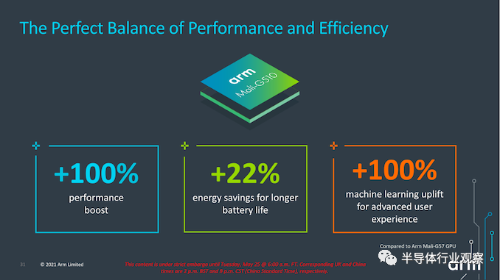

在發(fā)布CPU的同時,Arm還帶來了全新的CPU家族Mali-G710旗艦系列,G510中端系列和新型超區(qū)域高效Mali-G310的廣泛產(chǎn)品陣容。

在高端產(chǎn)品上,Mali-G710是Mali-G78的直接繼承者,在目標(biāo)上是相對簡單的世代改進:Arm的架構(gòu)師可以在Mali GPU中實現(xiàn)最高性能。Mali-G610是一項品牌推廣活動,旨在以更少的核心數(shù)量區(qū)分與G710相同的微體系結(jié)構(gòu),目的是幫助合作伙伴更好地區(qū)分旗艦產(chǎn)品與“高端”產(chǎn)品。

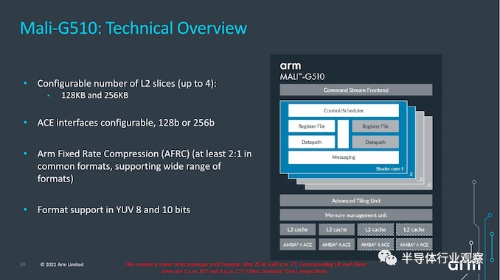

Mali-G510是2019年Mali-G57的后繼產(chǎn)品,是Arm中檔產(chǎn)品組合的重大升級,帶來了極大的功耗性能提升,并在功率效率方面比以前的產(chǎn)品有所提高。

最后,新的Mali-G310是基于Valhall的新低端產(chǎn)品,代表了基于Bifrost的Mali-G31的多代架構(gòu)升級,并瞄準(zhǔn)了以低面積效率為重點的市場我們看到了數(shù)千億的低成本設(shè)備和其他嵌入式市場,例如智能電視。

Mali-G710:使每核性能提高一倍

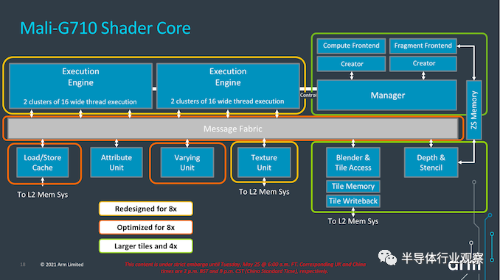

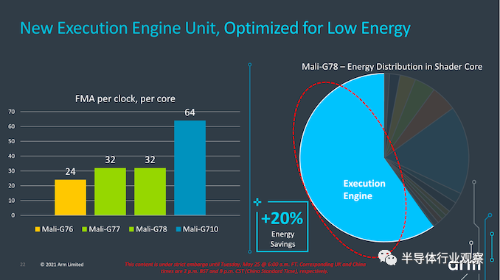

作為Valhall GPU架構(gòu)的延續(xù),新型G710執(zhí)行引擎的基礎(chǔ)特征與上一代Mali-G77和Mali-G78相似且大致相同。

我們在Valhall看到的更大變化包括從wavefront/warp 大小8到16的轉(zhuǎn)變,每個執(zhí)行引擎具有dual datapaths (clusters) ,從而在G77和G78中看到了32 FMA /核心設(shè)計。

據(jù)說ISA已經(jīng)有了Vulkan等新的現(xiàn)代API所設(shè)計的更大改進,但始終很難量化此類更改對GPU的整體性能和效率的影響。

Mali-G710的新增功能是添加了第二個執(zhí)行引擎,有效地將Valhall架構(gòu)的每個著色器核心(shader core)的計算性能提高了一倍。從某種意義上說,Arm在這里重新采用了我們在上一代Mali體系結(jié)構(gòu)中所見過的一些擴展手段,例如與Mali-G76每個著色器核心具有三個執(zhí)行引擎的情況相比。

在上面的幻燈片中,“ 8x”和“ 4x”指標(biāo)與每個內(nèi)核的每個周期的吞吐量有關(guān),通過這些指標(biāo)我們可以看到,GPU的其他功能塊在吞吐量方面也提高了一倍,以保持執(zhí)行引擎的計算執(zhí)行吞吐量提高了一倍。

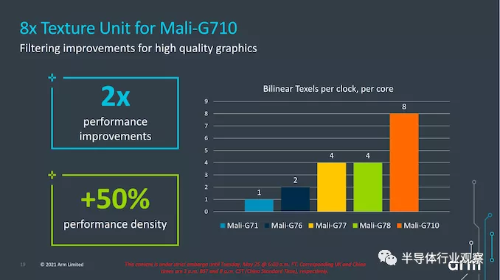

新的G710包括一個全新的紋理單元(texture unit ),現(xiàn)在每個時鐘可以處理多達(dá)8個雙線性紋理元素,Arm通常對新設(shè)計進行了優(yōu)化,以顯著提高面積效率,從而使新的TMU具有+ 50%的性能密度優(yōu)勢。

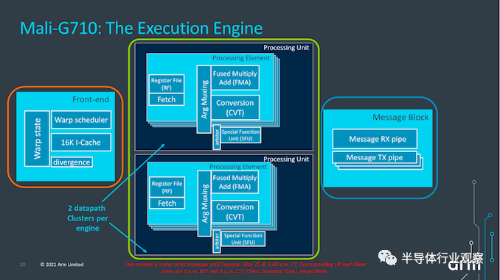

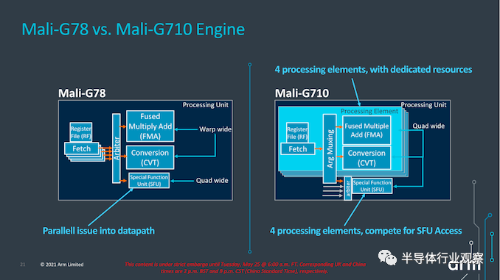

在執(zhí)行引擎中,Arm繼續(xù)使用兩個處理單元或處理元素集群,在這方面,我們看不出各代之間有太大差異,但是,如果我們更深入地研究實際的處理單元,則會對塊進行更改:

在最簡單和基本的解釋中,我們看到的是從一個16寬(warp wide))處理元素和執(zhí)行單元的單個實例轉(zhuǎn)換為四個4寬執(zhí)行單元的實例。設(shè)計之間的吞吐量沒有改變,但是新的微體系結(jié)構(gòu)為處理元素提供了更多的專用資源,并允許更好的結(jié)構(gòu)以提高效率。

總的來說,新的執(zhí)行引擎設(shè)計使FMA每個內(nèi)核的每個時鐘頻率提高了一倍,這在某種程度上是顯而易見的,但是它還具有將執(zhí)行引擎在著色器內(nèi)核內(nèi)的能量分配降低20%的好處。

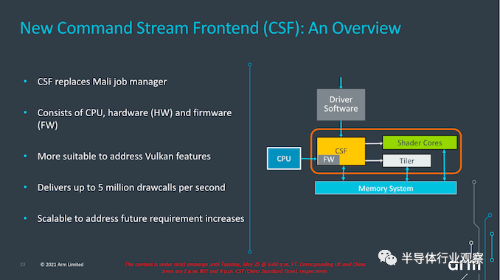

G710的另一個非常重要的亮點是用新的“Command Stream Frontend”代替了傳統(tǒng)的“Job Manager”,該“Command Stream Frontend”可以處理draw-calls的調(diào)度和處理。CSF引入了一個未公開性質(zhì)的新CPU,并且現(xiàn)在還將首次向Mali GPU引入固件層。

該設(shè)計的目標(biāo)是為更復(fù)雜的圖形工作負(fù)載實現(xiàn)更靈活和可擴展的性能,同時通過為其提供非常輕量級的submission path來減少驅(qū)動程序開銷,從而提高系統(tǒng)CPU的電源效率。它有助于簡化對API功能(例如狀態(tài)繼承和輔助緩沖區(qū))的支持,以及處理對時間敏感的應(yīng)用程序(例如VR或time-warp應(yīng)用程序)。靠近硬件的距離以及由此帶來的等待時間的減少也極大地受益于同步事件。

固件與硬件緊密耦合,可以處理來自主機的請求或命令緩沖區(qū)完成通知,減少諸如受保護的入口退出之類的開銷,甚至還可以通過額外的功能來模擬硬件中尚不存在的API功能。指示。

新硬件從頭開始進行了重新設(shè)計,以便能夠跟上最新內(nèi)容,并允許將job submission 吞吐量傳遞到其他GPU單元中。Arm在這里聲稱,新的CSF每秒最多可以進行500萬次調(diào)用。

總體而言,新的G710微體系結(jié)構(gòu)看起來非常有趣,尤其是要解決與Arm的Mali GPU的API開銷相關(guān)的一些弱點。如何發(fā)揮作用還有待觀察,但從這一代人所宣稱的20%的性能和功率效率增益來看,這似乎是一個穩(wěn)固的進步,盡管這些數(shù)字不足以改變移動市場的競爭格局。

Mali-G610是與G710相同的微架構(gòu),只是內(nèi)核配置低于7個內(nèi)核而使用了不同的名稱。

Mali-G510和G310:攻占低端

在中檔中,新的Mali-G510和Mali-G310是對市場上正在使用的前輩產(chǎn)品G57和G31的代升級。這些新設(shè)計代表了微體系結(jié)構(gòu)中的新重大突破,對于Arm的中端和低端產(chǎn)品而言,這是自然而然的大性能提升。

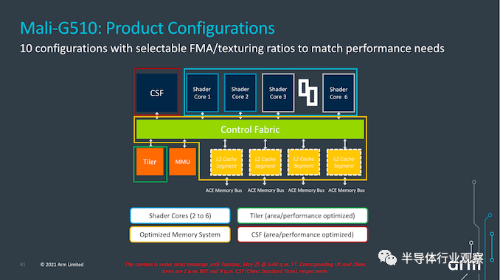

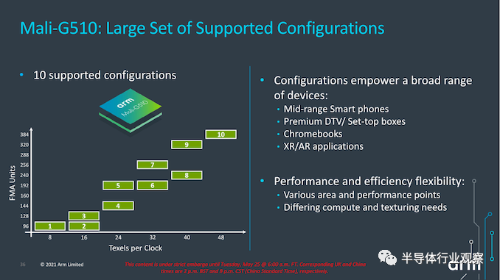

從很高的角度來看,G510可從2核擴展到6核,但通過更改每個核之一的執(zhí)行單元中的簇數(shù),或更改使用的紋理單元的類型(4倍的吞吐量)來提供差異化單位或8x單位。

在執(zhí)行引擎方面,我們總是有兩個執(zhí)行引擎,但是可以將其中一個執(zhí)行引擎配置為僅包含一個集群,從而有效地將核心的計算部分從64 FMA /周期設(shè)計減少到48 FMA /周期設(shè)計。這種粒度的原因是此類GPU的普通客戶具有超優(yōu)化的用例,并將針對特定用例和標(biāo)準(zhǔn)配置其GPU實施,并且僅使用最小的最小配置來滿足這些需求。

Arm在這里重點介紹G510 IP的10種不同配置選項,它們均具有不同的計算或填充率優(yōu)化性能點。對于讀者來說,了解這種可配置性的需求可能有點不直觀,但是在實現(xiàn)方面,有些非移動市場真正關(guān)心每平方毫米的幾分之一。

新的G310可進一步擴展到G510以下。與上一代最小的Mali IP產(chǎn)品G31相比,此GPU實際上是一項重大的性能飛躍,因為我們看到了從Bifrost架構(gòu)到新的Valhall設(shè)計的轉(zhuǎn)變。

在這里,我們看到采用了新的執(zhí)行引擎設(shè)計,但是允許將集群進一步縮小到每個EE僅一個集群,并且還允許在最低配置下僅允許一個EE,從而允許擴展16、32、48或64 FMA每個著色器核心。紋理單元還可以最小縮小到2個紋理像素/周期單元,并且看到一個變化的單元,與其較大的同級對象相比,該單元被縮小了。

G310僅是單個著色器核心設(shè)計,因此配置是通過更改該核心內(nèi)的不同執(zhí)行單元來唯一實現(xiàn)的。不幸的是,Arm似乎并未針對各種配置計劃任何公開的命名方案,因此,廠商將有責(zé)任進行任何形式的披露。