DRAM是存儲(chǔ)器市場(chǎng)當(dāng)中最大細(xì)分領(lǐng)域。同時(shí),隨著服務(wù)器、智能手機(jī)、PC等產(chǎn)品對(duì)DRAM需求的增長(zhǎng),這類半導(dǎo)體產(chǎn)品將迎來新一輪的超級(jí)成長(zhǎng)時(shí)期。

從結(jié)構(gòu)上看,DRAM存儲(chǔ)器,存儲(chǔ)單元由一個(gè)電容器和一個(gè)晶體管組成。電容器用于存儲(chǔ)電荷,晶體管用于訪問電容器,可以讀取存儲(chǔ)了多少電荷,也可以存儲(chǔ)新的電荷。但隨著小型化、集成化的發(fā)展,DRAM的缺點(diǎn)也暴露了出來——單個(gè)晶體管不能很好地將電荷保持在小電容器中。它將使電流從電容器泄漏或流向電容器,從而隨著時(shí)間的流逝而失去其明確定義的充電狀態(tài)。通過定期刷新DRAM可以避免此問題,但這意味著讀取存儲(chǔ)器的內(nèi)容并將其重新寫回。

而在數(shù)據(jù)處理需求的激增下,這種類型的DRAM并更好地滿足未來市場(chǎng)需求。因此,業(yè)界也在尋找新的技術(shù)來改善目前DRAM的技術(shù)。在這個(gè)過程當(dāng)中,有一些企業(yè)和機(jī)構(gòu)對(duì)無電容 DRAM技術(shù)展開了研究。

DFM

動(dòng)態(tài)閃存(Dynamic Flash Memory:DFM)是由Fujio Masuoka博士創(chuàng)立的公司Unisantis Electronics推出的。據(jù)介紹,這是一種比DRAM或其他類型的易失性存儲(chǔ)器更快,更密集的技術(shù),并將有希望成為DRAM的替代者。

DRAM是一種易失性的、基于電容的、破壞性讀取形式的存儲(chǔ)器——長(zhǎng)期以來,它的挑戰(zhàn)一直是在不增加功耗的情況下繼續(xù)封裝在更低的成本中。

DFM也是易失性存儲(chǔ)器的一種,但是由于它不依賴于電容器,因此泄漏路徑較少。采用這種技術(shù)的開關(guān)晶體管和電容器之間沒有連接。

在DFM開發(fā)的過程當(dāng)中,垂直環(huán)繞門晶體管(SGT)技術(shù)充當(dāng)著重要的角色。據(jù)介紹,垂直SGT為最終的電路實(shí)現(xiàn)提供了幾個(gè)關(guān)鍵特性:與平面和FinFET晶體管相比,提高了面密度;由于對(duì)晶體管通道的周圍柵極進(jìn)行了強(qiáng)大的靜電控制,因此降低了泄漏功率,針對(duì)最終應(yīng)用優(yōu)化晶體管寬度和長(zhǎng)度尺寸,無論是高性能還是極低的功耗。

DFM / SGT技術(shù)仍會(huì)泄漏電荷,但速率要比DRAM慢得多,并且讀取是無損的。這意味著刷新周期之間的間隔更長(zhǎng),因此有更多的讀寫帶寬。DFM / SGT提供塊刷新和擦除,并且比DRAM提供更快的訪問速度。

Unisantis聲稱,在仿真中,DFM具有很大的潛力,其密度是DRAM的四倍,并且具有顯著的Gb / mm?改善。它說,使用DFM的單元結(jié)構(gòu),當(dāng)今對(duì)DRAM(當(dāng)前為16Gb)的限制可能會(huì)立即增加到64Gb內(nèi)存。

Unisantis已經(jīng)發(fā)展了DFM概念,現(xiàn)在正尋求發(fā)展一系列的內(nèi)存和鑄造合作伙伴關(guān)系,以公開測(cè)試和演示DFM的功能和潛力。

2T0C DRAM

除了DFM外,來自佐治亞理工、圣母大學(xué)、羅徹斯特理工學(xué)院的研究者也曾提出了一種新型的無電容DRAM。

在去年舉行的 IEEE 國(guó)際電子設(shè)備會(huì)議(IEDM)上,該研究小組表示:“這種新型的DRAM 由氧化物半導(dǎo)體制成,并內(nèi)置在處理器上方的各層中,其位長(zhǎng)是商用 DRAM 的數(shù)百或數(shù)千倍,并且在運(yùn)行大型神經(jīng)網(wǎng)絡(luò)時(shí)可以提供較大的區(qū)域,節(jié)省大量能源。”

這種新的嵌入式DRAM僅由兩個(gè)晶體管制成,沒有電容器(2T0C)。這之所以可行,是晶體管的柵極是自然的(盡管很小)電容器。因此,代表該位的電荷可以存儲(chǔ)在此處。該設(shè)計(jì)具有一些關(guān)鍵優(yōu)勢(shì),特別是對(duì)于AI。

據(jù)了解,2T0C DRAM單元讀取數(shù)據(jù),無需破壞數(shù)據(jù),不必重寫數(shù)據(jù)。該研究小組成員表示,2T0C的排列方式不適用于硅邏輯晶體管。由于晶體管的柵極電容太低并且通過晶體管的泄漏太高,任何位都會(huì)立即流失。因此,研究人員轉(zhuǎn)向由非晶氧化物半導(dǎo)體制成的設(shè)備。

在這種方法的指導(dǎo)下,比利時(shí)微電子研究中心(Imec)的研究人員在國(guó)際電子器件會(huì)議(IEDM)上推出了一種類似的 2T0C 嵌入式方案,該方案使用銦鎵鋅氧化物(IGZO)作為半導(dǎo)體。Imec的高級(jí)科學(xué)家Attilio Belmonte指出,IGZO必須在有氧的情況下進(jìn)行退火,以修復(fù)由氧空位引起的材料缺陷。這具有減少IGZO中可有助于電流流動(dòng)的自由電子數(shù)量的作用,但是如果沒有它,這些設(shè)備將不會(huì)像開關(guān)那樣起作用。

VLT技術(shù)

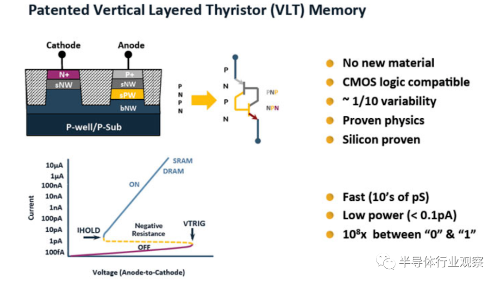

Kilopass也曾在2016年推出過VLT技術(shù)來實(shí)現(xiàn)無電容DRAM。

據(jù)了解,Kilopass的VLT采用無電容結(jié)構(gòu),通過垂直方式實(shí)現(xiàn)晶閘管架構(gòu),從而使存儲(chǔ)單元更加緊湊。緊湊的結(jié)構(gòu)加上所需的物理器件,構(gòu)造出制造工藝簡(jiǎn)單的交叉點(diǎn)內(nèi)存,這將帶來一項(xiàng)與DDR標(biāo)準(zhǔn)兼容,并且比當(dāng)時(shí)頂尖的20納米DRAM制造成本低45%的新技術(shù)。

與2T0C DRAM不同的是,據(jù)當(dāng)時(shí)的媒體報(bào)道稱,VLT技術(shù)存儲(chǔ)技術(shù)無需任何新材料,可以做到與邏輯CMOS工藝100%兼容。

Z-RAM

Z-RAM由Innovative Silicon進(jìn)行開發(fā)的,這也是一種無電容器的新型DRAM。據(jù)此前的報(bào)道顯示,Z-RAM是一個(gè)單晶體管DRAM,僅由一個(gè)晶體管作為存儲(chǔ)位單元。與由單個(gè)晶體管和復(fù)雜電容器組成的DRAM不同,不需要電容器或其他結(jié)構(gòu)即可形成Z-RAM存儲(chǔ)位單元。

Z-RAM依靠floating body效應(yīng),即絕緣體上硅(SOI)工藝的偽影,該工藝會(huì)將晶體管放置在隔離的槽中(晶體管體電壓相對(duì)于槽下方的晶圓襯底“float”)。floating body效應(yīng)導(dǎo)致在 tub的底部和下面的基板之間出現(xiàn)可變電容。floating body效應(yīng)通常是一種寄生效應(yīng),會(huì)影響電路設(shè)計(jì),但也可以在不添加單獨(dú)電容器的情況下構(gòu)建類似于DRAM的單元,然后,floating body效應(yīng)便取代了常規(guī)電容器。因?yàn)殡娙萜魑挥诰w管的下方(而不是像常規(guī)DRAM那樣與晶體管相鄰或位于晶體管上方),所以名稱“ Z-RAM”的另一個(gè)含義是它沿負(fù)z方向延伸。

在Z-RAM存儲(chǔ)單元中,通過使用碰撞電離產(chǎn)生多余的空穴和殘留的正電荷,邏輯狀態(tài)存儲(chǔ)在晶體管的浮體中。與DRAM中的電容器不同,讀取操作不會(huì)嘗試直接測(cè)量存在的電荷量。取而代之的是,電荷將柵極閾值電壓改變?yōu)榇蠹s1伏,從而提供了可觀的讀取噪聲容限。

RAM是在標(biāo)準(zhǔn)SOI邏輯過程中實(shí)現(xiàn)的,因此它將在邏輯上遷移到SOI所在的相同應(yīng)用程序區(qū)域中。有報(bào)道稱,它在速度、功率和密度方面的廣泛可配置性使它幾乎可以應(yīng)用于任何使用高速內(nèi)存的地方,特別是在高性能SOI應(yīng)用程序中。

然而,隨著傳統(tǒng)SRAM制造技術(shù)的進(jìn)步(最重要的是,向32nm制造節(jié)點(diǎn)的過渡),Z-RAM失去了它的優(yōu)勢(shì)。

這種趨勢(shì)也反應(yīng)在其商業(yè)應(yīng)用上。據(jù)維基百科的介紹顯示,雖然AMD在2006年批準(zhǔn)了第二代Z-RAM,但該處理器制造商在2010年1月放棄了Z-RAM計(jì)劃。類似地,DRAM生產(chǎn)商SK Hynix也在2007年授權(quán)Z-RAM用于DRAM芯片,Innovation Silicon在2010年3月宣布,他們正在聯(lián)合開發(fā)一種非SOI版本的Z-RAM,可以用更低成本的批量CMOS技術(shù)生產(chǎn),但該公司在2010年6月29日倒閉了。隨后,其專利組合于2010年12月被美光科技收購(gòu)。

另外一種途徑

與無電容器DRAM這種方式相比,IBM則提出了另外一種方式,這也被視為是推動(dòng)DRAM繼續(xù)發(fā)展的另外一條途徑。

IBM表示,過去的二十年中,人們一直在嘗試擺脫電容器,從而進(jìn)一步減少DRAM單元的面積和制造成本。而為了進(jìn)一步縮小尺寸,拆掉電容器幾乎已成為當(dāng)務(wù)之急。這就要求做到在不減少可存儲(chǔ)電荷量的情況下,縮小cell的橫向尺寸,那就留出了一條可供制造的途徑,即:使電容器“藏”得更深。

但I(xiàn)BM指出,從長(zhǎng)遠(yuǎn)來看,這是一個(gè)瓶頸,這不僅是由于幾何(geometrical)約束,而且還因?yàn)椤翱住保╳ell)頂部的電荷積累使使用整個(gè)存儲(chǔ)容量更具挑戰(zhàn)性。而將電荷存儲(chǔ)在晶體管主體中已被認(rèn)為是進(jìn)一步縮小尺寸的最佳策略。研發(fā)人員已經(jīng)使用硅對(duì)無電容器DRAM cell的不同變體進(jìn)行了實(shí)驗(yàn)研究。但是很少有人關(guān)注基于替代半導(dǎo)體材料的類似概念。在2019年的《自然電子雜志上》,IBM展示了有史以來最小的無電容器DRAM,其存儲(chǔ)單元長(zhǎng)度只有14納米。

這是一個(gè)單晶體管,無電容器的DRAM cell,它使用晶體管主體作為一種電容器,其中的電荷(在這種情況下為空穴)被臨時(shí)存儲(chǔ)在其中。電子空穴從晶體管主體的注入和抽出使得能夠調(diào)節(jié)晶體管的靜電行為,從而導(dǎo)致兩個(gè)不同的電流水平。像InGaAs這樣的III-V材料通常具有比硅更小的帶隙,而硅原則上具有在低得多的電壓下工作的潛在優(yōu)勢(shì)。反過來,這轉(zhuǎn)化為可能更低的功耗。

IBM方便表示,他們已經(jīng)證明了無電容器MSDRAM cell的柵極長(zhǎng)度為14納米的可行性。通過使用晶體管本體來存儲(chǔ)電子空穴數(shù)量,我們能夠獲得對(duì)應(yīng)于二進(jìn)制狀態(tài)0和1的兩個(gè)不同的電流電平。而該存儲(chǔ)器概念的實(shí)驗(yàn)實(shí)現(xiàn)證實(shí)了TCAD仿真獲得的結(jié)果。

與基于硅的實(shí)現(xiàn)相比,IBM使用InGaAs的新穎概念為實(shí)現(xiàn)DRAM存儲(chǔ)器的積極小型化提供了一條有希望的途徑,同時(shí)還降低了功耗。從有關(guān)性能指標(biāo)(例如保留時(shí)間)的這一概念進(jìn)一步改進(jìn)的潛力,而IBM艱辛存在可行的策略來實(shí)現(xiàn)這些改進(jìn)。

從這些新技術(shù)的出現(xiàn)中,我們得以預(yù)見,DRAM正在開啟新一輪的變化。而哪種技術(shù)能夠取代現(xiàn)在的DRAM,還需要市場(chǎng)的考驗(yàn)。