在過去的幾周中,Zen 4引起了很多關注,但有關Zen 5的第一條信息卻產(chǎn)生了更大的期望,并不是因為它可能具有的性能或它可能帶來的高級功能,而是因為這種架構可以代表從AMD過渡到big.LITTLE設計,即具有高性能核心模塊和高效核心模塊的配置。

這些設置并不是什么新鮮的東西。正如我們的許多讀者所知道的那樣,在智能手機領域,一段時間以來,我們一直在看到SoC,這些SoC帶來了具有兩個和三個核心塊的處理器,這些核心塊充當了專用元素,可以根據(jù)所需功率來執(zhí)行不同的工作負載。因此,當工作負載輕時,高效內(nèi)核便開始運行;在要求苛刻的情況下,將激活高性能內(nèi)核;當需要最大功率時,則將激活功能更強大的內(nèi)核,在Snapdragon 888s中使用Cortex-X1建筑學。

蘋果公司是第一個通過Apple M1 SoC將這種結構引入個人計算機領域的公司,該芯片是基于ARM的芯片,具有高性能四核和高效四核配置。根據(jù)我們所看到的最新信息,英特爾將緊隨其后的是Alder Lake-S處理器,該處理器將結合基于Golden Cove架構的高性能Core內(nèi)核(用于Tiger Lake的WillowCove的后繼產(chǎn)品)和Atom內(nèi)核基于Gracemont架構的低能耗產(chǎn)品。

蘋果和英特爾都將在其未來的處理器中采用這種方法,AMD會做什么?我們幾乎可以假設它不會使用Zen 4過渡到big.LITTLE設計,但似乎所有跡象都表明它將與其后續(xù)產(chǎn)品Zen 5一起使用。

AMD還將在Zen 5中采用big.LITTLE

隨著業(yè)界精英準備向具有專用核心模塊的這些類型的配置過渡,很明顯,AMD開始邁向big.LITTLE只是時間問題,盡管我們尚不清楚它是哪一代產(chǎn)品可以做到,或者如何做到。他將能夠執(zhí)行這一舉動。

與AMD不同,英特爾已經(jīng)開發(fā)了兩種架構來支持具有這種配置的處理器,即基于Golden Cove的高性能Core和基于Gracemont的高效Atom。AMD需要一種架構來塑造高效內(nèi)核,根據(jù)新信息,這可能就是Zen 4D。

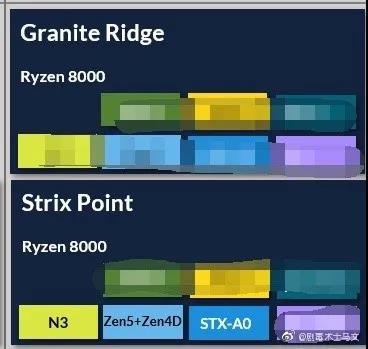

Zen 4D將與Zen 5一起用于Ryzen 8000處理器和APU中。這兩種架構都將以5nm工藝制造,盡管有傳言稱它們可能會躍升至3nm。根據(jù)最新傳聞,它們將使用AM5 LGA1718插座,最早將于2023年某個時候上市。但是,從半導體市場的現(xiàn)狀來看,我認為最終很可能會推遲到2024年。

制程方面,Moepc報告稱,臺積電目前正按計劃在2021年測試3nm,隨后將在2022年下半年進行大批量生產(chǎn)。除AMD之外,蘋果是臺積電3nm節(jié)點的另一個大客戶。現(xiàn)在猜測可以預期的性能和效率提升還為時過早,但臺積電先前曾表示,3nm節(jié)點可將功耗降低多達25%至30%,性能提高10%至15%,與5 nm工藝相比,晶體管密度增加了1.7倍。

我們尚無關于AMD可以采用的可能內(nèi)核配置的信息,但很可能我們將在一個高性能模塊中找到多達16個Zen 5內(nèi)核,以及8至16個高效Zen 4D內(nèi)核。如果確認這一點,那么Ryzen 8000系列產(chǎn)品范圍的頂端將有32個內(nèi)核,分為兩個每個16個內(nèi)核的模塊。

另一方面,基于Zen 5和Zen 4D的Ryzen APU將具有最多8個Zen5內(nèi)核和最多4個Zen 4D內(nèi)核的配置,這使我們在CPU側(cè)總共有12個內(nèi)核。您的GPU可以使用RDNA 3架構和新的大型L4緩存塊,它將用作一種無限緩存來提高性能。

據(jù)VideoCardz報道,Zen 4架構之后的Zen 5架構Ryzen處理器的代號是GraniteRidge,很可能是Ryzen 8000系列,將采用3nm工藝制造,不過對于其相關規(guī)格仍缺乏了解,比如是否繼續(xù)集成RDNA 2架構核顯或者提供PCIe Gen5的支持。

此前已泄露的代號為Strix Point的APU,傳聞稱其會和英特爾的Alder Lake一樣,采用big.LITTLE架構,以8個大核搭配4個小核。其中會使用Zen 5架構的核心,并采用3nm工藝制造。最新的消息指出,會引入新的緩存機制,其結構則是Zen 5+Zen 4D,不清楚是否意味著大核心是Zen 5架構,而小核心是Zen 4D架構?消息源指出,不確定APU的這種做法是否也會應用到CPU上。

此外,據(jù)說 AMD 會在 StrixPoint APU 上配備 L4 級系統(tǒng)緩存,但該系列芯片將只專門針對特定的移動設備推出,臺式機上的芯片依然會采用相同的 CPU 核心設計。

至于 AMD 是否會將 X3D 封裝技術用于 Strix Point APU,目前看來還是相當值得期待的,因為它很像是繼 MCM 多芯片封裝技術之后的新一代 APU 發(fā)展方向。

截至目前,AMD APU 一直都在沿用單芯片設計,包括 CPU / GPU / IO 在內(nèi)的組件模塊都被安裝在了同一芯片上。

與此同時,諸如 RNDA 3 和Infinity Cache 之類的 GPU 技術,也有望隨Strix Point Ryzen APU 一起首次亮相。至于真相究竟如何,仍有待時間去檢驗。

現(xiàn)階段由于缺乏進一步的資料無法判斷,未來需要更多的信息才能了解了。