AMD的CEO一一Lisa Su在5月31日召開的“COMPUTEX TAIPEI Virtual”上做了基礎(chǔ)演講,同時介紹了AMD的最新產(chǎn)品、技術(shù)。本文,筆者就AMD發(fā)布的“3D Chiplet Technology”展開敘述。

AMD的CEO一一Lisa Su公布了采用了3D Chiplet Technology的“Ryzen 5000 Series 3D Chiplet Prototype”。(圖片出自:pc.watch)

“3D Chiplet Technology”是通過應(yīng)用于客戶端PC的“Ryzen”或者應(yīng)用于服務(wù)器方向的“EPYC”導(dǎo)入2D芯片混搭技術(shù)的3D 版本的“Chiplet Technology”。以往是在Package的橫方向搭載數(shù)個芯片,而3D Chiplet Technology采用的是一種被稱為CDD的技術(shù),即在CPU芯片上縱向搭載SRAM的“芯片堆疊(Die Stacking)”技術(shù)。

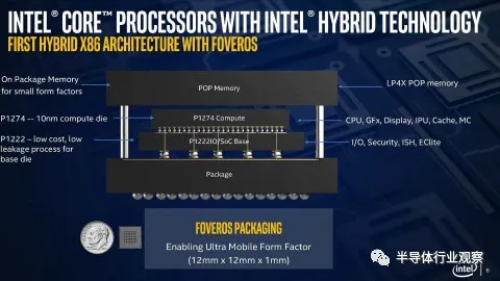

英特爾也于2018年12月發(fā)布了被稱為“Foveros”的3D 堆疊技術(shù),已于2020年作為“Intel Core processors with Intel Hybrid Technology”(研發(fā)代碼:Lakefield)而投產(chǎn)。

由上可知,封裝技術(shù)(即將芯片封裝在基板上)是繼處理器架構(gòu)、制造技術(shù)之后的第三個競爭核心。

英特爾最大40核、AMD為64核,秘密在于Chiplet

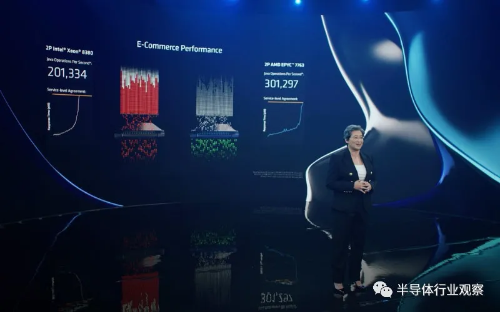

第三代Xeon SP (Xeon Platinum 8830,40核)、第三代EPYC(EPYC 7763,64核,右側(cè))、EC站點(diǎn)服務(wù)器的基準(zhǔn)數(shù)據(jù)。Lisa Su稱,第三代EPYC的性能提高了50%。(圖片出自:pc.watch)

在此次的COMPUTEX TAIPEI Virtual上的基礎(chǔ)演講中,AMD的CEO一一Lisa Su對AMD三月份發(fā)布的第三代EPYC處理器(以下簡稱為第三代:EPYC,研發(fā)代碼:Milan)和英特爾四月份發(fā)布的第三代Xeon Scalable Processors(以下簡稱為:第三代Xeon SP,研發(fā)代碼:Ice Lake)進(jìn)行了比較。

前者為64核的EPYC 7633,后者為40核的Xeon Platinum8380。Lisa Su表示,如果是用于EC(電子商務(wù))的服務(wù)器的話,EPYC7763的性能要高出50%。

服務(wù)器的工作負(fù)荷(Workload)極其復(fù)雜,也并不是由一個應(yīng)用發(fā)揮其他多個應(yīng)用的性能,因此,此處暫時不做敘述。

AMD的處理器在性能上遠(yuǎn)遠(yuǎn)超過英特爾的最大理由是,CPU核數(shù)多于英特爾。當(dāng)我們比較一個封裝基板的時候,AMD的最高核數(shù)為64,英特爾為40。

英特爾的第三代Xeon SP與第三代的EPYC的差異。

(圖片出自:pc.watch)

那么,為什么AMD的CPU核數(shù)多呢?其答案在于“封裝技術(shù)”。

就英特爾的第三代Xeon XP而言,在被稱為“傳統(tǒng)的單一芯片(Traditional Monolithic Die )”的Package中有一個芯片(Die)。而40個CPU核被封裝在一個芯片(Die)里,不僅很難生產(chǎn)單個的芯片,而且很難提高良率(可采用的芯片數(shù)量占總生產(chǎn)數(shù)量的比例)。

與此相對,AMD的EPYC采用的是被稱為“Chiplet Technology”的封裝技術(shù)。Chiplet上混搭有被稱為CCD(Core Chiplet Die)的CPU核的芯片和IOD(I/O Die)。

CCD上的一個芯片由8核的CPU構(gòu)成,與用于客戶端PC的Ryzen等一樣,如果是臺式PC的話,由1個CCD1和IOD組成的八核產(chǎn)品可更改為由2個CCD和IOD組成的16核產(chǎn)品。如果是服務(wù)器的話,組成結(jié)構(gòu)為8個CCD、1個IOD(為最大限度),即可組成的產(chǎn)品為:8核x8=64核。

結(jié)果就在Lisa Su講的產(chǎn)品性能比較表中,用于臺式PC的Ryzen的核數(shù)之所以超過英特爾的用于臺式PC的核處理器,也是一樣的道理,可以說,近幾年來AMD獲得飛躍式進(jìn)步的最大的理由也在于Chiplet的應(yīng)用。

將Chiplet以3D方向擴(kuò)張的“3D Chiplet Technology”,在一個CCD上搭載64MB的SRAM

3D Chiplet Technology的構(gòu)造。

(圖片出自:pc.watch)

如果說AMD的Chiplet是在Package內(nèi)部橫向展開的話,那么,在COMPUTEX TAIPEI上發(fā)布的“3D Chiplet Technology”就是在Package的縱向堆疊芯片。

AMD此次發(fā)布的產(chǎn)品如下,在CCD的芯片上,堆疊由7納米工藝制造的SRAM,將64MB的SRAM芯片堆疊在Zen 3基的CPU核上,SRAM的左右兩邊用硅填充。

芯片和芯片之間采用TSV(Through Silicon Via)技術(shù),穿透CPU芯片上的孔后,與CPU的中介層(Interposer)直接連接。因此,不需要在中間插入基板,可直接將芯片連接,且CPU和SRAM之間可以進(jìn)行高速通信。

Lisa Su表示,SRAM 是作為L3 CACHE來工作的(此外,On-die的SRAM也可繼續(xù)作為L3 CACHE來使用)。當(dāng)然,On-die的SRAM可以高速工作、且可以減少內(nèi)存延遲(Memory Latency),但是像這次的Off-die的話,內(nèi)存延遲會增加。但是,由于容量增加了,也可以提高性能。

Ryzen 9 5900X和Ryzen 5000 Series 3D Chiplet Prototype的區(qū)別,此圖為筆者制作。(圖片出自:pc.watch)

此次Lisa Su展示的樣品有以下,Ryze 9 5900 X以及采用了被稱為“Ryzen 5000 Series 3D Chiplet Prototype”的3D Chiplet Technology的產(chǎn)品。

Ryzen 9 5900X內(nèi)置了兩個CCD(CPU的核數(shù)為12,1個CCD 有六個核,所以6核X2個CCD),搭載64MB的L3 CACHE。5900X中,8核的CCD有兩個,每個CCD的L3 CACHE為32MB。

即,整個封裝為192MB,搭載有現(xiàn)有產(chǎn)品(64MB)三倍的L3 CACHE。

(圖片出自:pc.watch)

Ryzen 9 5900X和Ryzen 5000 系列3D Chiplet Technology的性能比較、平均可以提高15%的性能。(圖片出自:pc.watch)

從Lisa Su公開的資料來看,比較了Ryzen 9 5900 X(12 核、L3 CACHE 、64MB)和Ryzen 5000 系列3D Chiplet Technology(12核,192MB)在游戲時的幀速率, 發(fā)現(xiàn)后者高出前者12%。放入其他游戲中比較后發(fā)現(xiàn),性能高出約15%。

L3 CACHE的容量增加即意味著內(nèi)存延遲(CPU讀取到存儲器數(shù)據(jù)的延遲)的減少,出現(xiàn)這樣的效果的原因在Lisa Su的演講中。

Lisa Su明確表示,3D壓層的SRAM 會在今年(2021年)年末發(fā)布。由于名稱不是“Ryzen 6000 系列”,而是“Ryzen 5000 系列3D Chiplet Technology”,因此,會作為Ryzen 5000系列的追加SKU投入。

此外,Lisa Su還表示,5納米的“Zen 4”世代的產(chǎn)品在明年(2022年)投入。由于TSMC的5納米工藝已經(jīng)用于生產(chǎn)蘋果的M1,因此生產(chǎn)技術(shù)已經(jīng)十分成熟。

英特爾計(jì)劃在未來的產(chǎn)品中使用3D 堆疊技術(shù)一一“Foveros”

英特爾去年(2020年)發(fā)布的“Intel processors with Intel Hybrid Technology(研發(fā)代碼:Lakefield)”的結(jié)構(gòu)。基底(Substrate)上有I/O芯片、CPU/GPU芯片、DRAM,三層結(jié)構(gòu)。(圖片出自:pc.watch)

但是,這種單層構(gòu)造并不是AMD的專利,英特爾也在將同樣的技術(shù)應(yīng)用于產(chǎn)品。在2018年的Intel Architecture Day上,公布的“Foveros”即為3D壓層技術(shù)。

后來,F(xiàn)overos作為2020年投產(chǎn)的“Intel Core processors with Intel Hybrid Technology(研發(fā)代碼:Lakefield)”的芯片壓層技術(shù),而被應(yīng)用。就Lakefield的芯片壓層而言,將由10納米工藝生產(chǎn)的CPU/GPU芯片、22納米工藝生產(chǎn)的PCH按照3D方向封裝,雖然與AMD(以SRAM為壓層對象)的應(yīng)用不同,但是基本思想是一致的。