一份最新報告指出,從 DDR4 到 DDR5 內(nèi)存的過渡應該是迅速的。

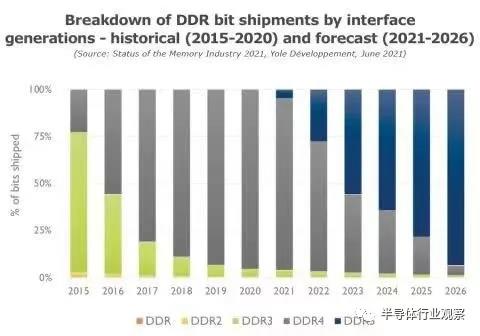

根據(jù)行業(yè)專家Yole Developpement的一份報告,DDR5 的廣泛采用應該會在 2022 年開始,從服務器市場和企業(yè)界開始。然后在 2023 年,我們將最終看到主流市場廣泛采用 DDR5,手機、筆記本電腦和 PC 將充分利用該技術(shù)。事實上,我們應該會在 2023 年看到DDR5 出貨量超過 DDR4,這標志著兩種技術(shù)之間的快速過渡。

更具體地說,據(jù)估計,2022 年 DDR5 的采用率將增加 25%(感謝服務器市場),然后在 2023 年實現(xiàn)更大的躍升,達到超過 50% 的市場份額。最后,到 2024 年至 2026 年,我們應該預計其他市場將效仿 DDR5 的采用,使 DDR4 僅占市場的 5%。

巨大的需求應該會加速向 DDR5 的遷移,需求已經(jīng)顯著回升(盡管 2019 年存在供過于求的問題)。事實上,該公司預測DRAM市場價值 1200億美元,NAND 市場價值 680億美元,創(chuàng)歷史新高。這種趨勢應該會持續(xù)到 2026 年,屆時內(nèi)存市場的價值應該會超過 2000 億美元。

DDR5是對當前 DDR4 內(nèi)存架構(gòu)的重大升級。DDR5 的帶寬將是 DDR4 的兩倍,以及芯片密度的四倍。這將允許顯著更高容量的 DIMM,同時以較低的工作電壓運行。DDR5 還具有內(nèi)置 ECC 支持以提高可靠性,但這是一種芯片級技術(shù),不符合保護傳輸中數(shù)據(jù)的成熟 ECC 內(nèi)存技術(shù)的要求。因此,我們也將看到 DDR5 內(nèi)存的標準和 ECC 風格。

DDR5的優(yōu)勢

作DDR4 的后繼者,DDR5 是下一代同步動態(tài)隨機存取存儲器 (SDRAM)。DDR 存儲器可在單個時鐘周期內(nèi)發(fā)送和接收兩次數(shù)據(jù)信號,并允許更快的傳輸速率和更高的容量。

雖然 DDR 內(nèi)存中的大多數(shù)開發(fā)都是適度的增量,重點是性能改進以滿足服務器和個人計算機應用程序要求,但從 DDR4 到 DDR5 的跨越是一個更大的飛躍。在需要更多帶寬的驅(qū)動下,DDR5 在強大的封裝中帶來了全新的架構(gòu)。

計算能力的迅速發(fā)展使中央處理器制造商努力提供盡可能多的核心數(shù)量。不久前,個人計算機用戶只能期待 4 核芯片。現(xiàn)在,大多數(shù)中央處理器制造商會提供 6 核中端芯片和 12 核高端芯片。對于服務器解決方案,制造商們提供多達 64 內(nèi)核。當前服務器內(nèi)存解決方案(如 DDR4)不能滿足這些高核計數(shù)中央處理器的帶寬需求。

信號完整性、電源傳輸和布局復雜性限制了每個內(nèi)核的內(nèi)存帶寬進度。要釋放下一代中央處理器的強大功能,需要新的內(nèi)存架構(gòu),以符合其更高的每核帶寬要求。這是開發(fā) DDR5 SDRAM 解決方案的主要驅(qū)動力。

為滿足下一代中央處理器的需求,DDR5 帶來了更高的數(shù)據(jù)速率、更低的能耗和更高的密度。DDR5 發(fā)布后的最大數(shù)據(jù)速率為 4800MT/s(百萬次/秒),而 DDR4 為 3200MT/s。系統(tǒng)級仿真中的并行比較顯示,DDR5 的有效帶寬約為 DDR4 的 1.87 倍。

DDR5 將突發(fā)長度增加到 BL16,約為 DDR4 的兩倍,提高了命令/地址和數(shù)據(jù)總線效率。相同的讀取或?qū)懭胧聞宅F(xiàn)在提供數(shù)據(jù)總線上兩倍的數(shù)據(jù),同時限制同一存儲庫內(nèi)輸入輸出/陣列計時約束的風險。此外,DDR5 使存儲組數(shù)量翻倍,這是通過在任意給定時間打開更多頁面來提高整體系統(tǒng)效率的關(guān)鍵因素。所有這些因素都意味著更快、更高效的內(nèi)存以滿足下一代計算的需求。但是,DDR5 不僅提高了性能,還提高了可擴展性。

經(jīng)過優(yōu)化的 DRAM 核心計時和芯片內(nèi)糾錯碼是提高 DDR5 可擴展性的兩個主要因素。雖然內(nèi)存架構(gòu)逐年擴展,但它的代價是 DRAM 單元電容的下降和位線接觸電阻的增加。DDR5 解決了這些缺點,并允許通過優(yōu)化的核心計時進行更可靠的擴展,這對于確保有足夠的時間在 DRAM 單元中寫入、存儲和檢測電荷至關(guān)重要。

芯片內(nèi)糾錯碼 (ECC) 通過輸出數(shù)據(jù)之前在讀取命令期間執(zhí)行更正,提高了數(shù)據(jù)完整性并減少了系統(tǒng)糾錯負擔。DDR5 還引入了錯誤檢查清理,其中 DRAM 將在發(fā)生錯誤時讀取內(nèi)部數(shù)據(jù)并寫回已更正的數(shù)據(jù)。

為了提高記憶體的存取效能,DDR8采用由8個Bank Group組成的32 Bank(可以單獨啟用/停用的存儲單元)架構(gòu),比DDR4由4個Bank Group組成的16 Bank架構(gòu),多出1倍的存取可用性(Access Availability)。而DDR5的Burst Length(DRAM單個讀/寫指令可以存取的資料量)從DDR4的8增加到16,也是增加效能的關(guān)鍵功能。

不同于DDR4在更新(Refresh)時無法執(zhí)行其他操作,DDR5則透過Same Bank Refresh功能,讓系統(tǒng)可以在更新某些Bank的時候,存取其他Bank的資料,另一方面DDR5也透過決策回饋等化器(Decision Feedback Equalization,DFE)消除雜訊,以增加整體效能表現(xiàn)。

在電力消耗部分,DDR5的工作電壓為1.1V,低于DDR4的1.2V,能降低單位頻寬的功耗達20%以上。