從深度嵌入式系統(tǒng)到超大規(guī)模數(shù)據(jù)中心部署,人工智能(AI)和機器學習(ML)技術正在為其中迅速擴展的一系列的產品和應用提供支持。盡管支持這些應用的硬件設計存在很大程度的差異,但都需要硬件加速。

深度學習技術需要大量的張量算術運算(tensor arithmetic operation)。為了支持實時執(zhí)行,存儲器和處理器的性能必須滿足比標準軟件驅動架構盡可能高得多的性能目標。這種需求導致去使用基于專用硬件加速器的設計,來執(zhí)行并行化和高度流水線化的張量算術運算。為了避免通道阻塞,數(shù)據(jù)必須在合適的位置,合適的時間,以合適的格式出現(xiàn)。專用的數(shù)據(jù)編排硬件避免了加速器通道阻塞,從而支持以最高效率運行。

數(shù)據(jù)編排包括預處理和后處理操作,確保數(shù)據(jù)以最佳速度和最適合進行高效處理的格式傳輸?shù)綑C器學習引擎中。操作范圍從資源管理和使用規(guī)劃,到I/O適配、轉碼、轉換和傳感器融合,再到共享存儲陣列內的數(shù)據(jù)壓縮和重新排列。如何部署這些功能將取決于目標應用的性能和成本要求,但對于大多數(shù)應用場景而言,針對數(shù)據(jù)攝取、轉換和傳輸進行優(yōu)化的可編程邏輯平臺為機器學習加速器提供了最佳的數(shù)據(jù)編排策略。

引言

深度學習給計算硬件帶來了巨大的壓力。向專用加速器的轉變?yōu)樾酒夹g提供了一種與人工智能發(fā)展保持同步的方法,但這些單元本身并不能夠滿足以更低的成本獲得更高性能的需求。

可以理解的是,集成電路(IC)供應商和系統(tǒng)公司一直專注于其矩陣和張量處理陣列的原始性能。在峰值吞吐量下,這些架構可以輕松達到以每秒萬億次操作(TOPS)衡量的性能水平,即使對于旨在用于邊緣計算的系統(tǒng)也是如此。盡管可以理解,但如果由于數(shù)據(jù)不可用或需要為每個模型層轉換為正確的格式而導致延遲,那么對峰值TOPS的關注會帶來硬件利用率不足的風險。

系統(tǒng)必須對網(wǎng)絡和存儲延遲進行補償,并確保數(shù)據(jù)元素的格式和位置合適,同時以一致的速率傳入和傳出人工智能加速器。數(shù)據(jù)編排提供了在每個時鐘周期上確保數(shù)據(jù)格式和位置合適的方法,從而最大限度地提高系統(tǒng)吞吐量。

由于典型人工智能實現(xiàn)的復雜性,所以無論是位于數(shù)據(jù)中心、邊緣計算環(huán)境還是實時嵌入式應用,如自動駕駛輔助系統(tǒng)(ADAS)設計,有許多任務必須由數(shù)據(jù)編排引擎處理,這些任務包括:

數(shù)據(jù)操作(manipulation)

在多個矢量單元之間進行調度和負載平衡

數(shù)據(jù)損壞的數(shù)據(jù)包檢查,例如由傳感器故障造成的數(shù)據(jù)損壞

盡管可以通過向核心處理陣列添加數(shù)據(jù)控制和異常處理硬件來實現(xiàn)這些功能,但是由于可能需要的操作種類繁多,以及隨著人工智能模型的發(fā)展對靈活性的需求也越來越高,這使得將這些功能硬連線到核心加速器芯片中可能成為一種昂貴的短期選擇。例如,在一些應用環(huán)境中,加密支持正迅速成為確保高數(shù)據(jù)安全性的需求,但根據(jù)每層數(shù)據(jù)的應用敏感性,可能會使用不同級別的加密。固定架構解決方案存在著無法適應不斷變化的需求的風險。

一種可能的方法是使用一個可編程的微處理器來控制通過加速器的數(shù)據(jù)流。這種方法的問題在于軟件執(zhí)行根本無法滿足加速器硬件的需求。需要一個更加以硬件為中心的數(shù)據(jù)編排響應,這使得加速器設計完全專注于核心通道效率成為可能。外部數(shù)據(jù)編排可以處理所有的存儲和I/O管理,確保操作數(shù)和權重的傳輸不間斷。由于數(shù)據(jù)編排引擎必須處理應用程序和模型設計的修訂和更改,因此硬連線邏輯不是一種合適的方法。可編程邏輯支持修改,并避免了數(shù)據(jù)編排引擎無法更新的風險。

原則上,現(xiàn)場可編程邏輯門陣列(FPGA)結合了分布式存儲器、算術單元和查找表,從而提供了組合功能,該組合功能非常適合人工智能驅動的應用程序所需的流數(shù)據(jù)實時重組、重新映射和存儲器管理。FPGA支持創(chuàng)建定制的硬件電路,支持深度流水線化人工智能加速器的密集數(shù)據(jù)流,同時使用戶能夠根據(jù)需要改變實現(xiàn)方式以適應新的架構。然而,數(shù)據(jù)編排的性能要求需要新的FPGA設計方法。

數(shù)據(jù)編排的應用場景

在數(shù)據(jù)中心、邊緣計算和嵌入式系統(tǒng)部署等應用場景中,有許多不同類型的數(shù)據(jù)編排架構。例如,在數(shù)據(jù)中心應用環(huán)境中,多個加速器可以部署在單個模型上,它們的數(shù)據(jù)吞吐量由一個或多個數(shù)據(jù)編排引擎管理。

推理系統(tǒng)需要數(shù)據(jù)編排來確保每個工作引擎的最大效用,以避免瓶頸,并確保盡可能快地處理輸入的數(shù)據(jù)樣本。分布式訓練增加了對神經元權重快速更新的要求,這些更新必須盡快分配給處理相關模型部件的其他工作引擎,以避免停滯。

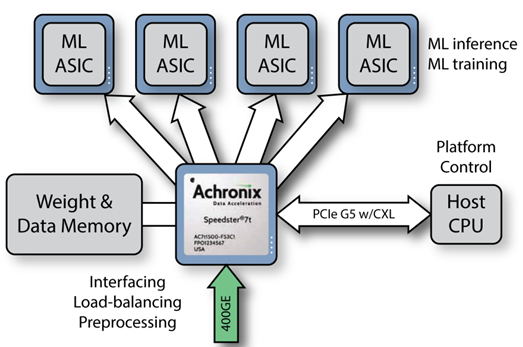

FPGA中的數(shù)據(jù)編排邏輯支持處理廣泛的權重分配和同步協(xié)議,以支持高效的運行,同時減輕加速器本身的數(shù)據(jù)組織負擔。下圖展示了一種可能的實現(xiàn)方法,使用一個FPGA器件管理同一塊電路板上的多個人工智能引擎。使用一種合適的低噪聲通信協(xié)議,單個機器學習專用集成電路(ASIC)不需要存儲控制器。相反,數(shù)據(jù)編排引擎在本地存儲器中組織所有的權重和數(shù)據(jù)元素,并簡單地將它們以合適的順序傳輸?shù)剿芾淼拿總€ASIC。其結果是通過減少重復的存儲和接口邏輯,以更低的總體成本獲得高性能。

圖1:數(shù)據(jù)編排可以為并行化的人工智能實現(xiàn)應用快速地提供負載平衡和其他數(shù)據(jù)轉發(fā)功能

利用數(shù)據(jù)編排,硬件可以在不增加成本的情況下進一步提高性能。一種選擇是利用網(wǎng)絡或系統(tǒng)總線數(shù)據(jù)的壓縮,避免使用更昂貴的互連。FPGA的邏輯層面可編程性支持通過網(wǎng)絡接口對數(shù)據(jù)進行壓縮和解壓縮。數(shù)據(jù)編排硬件還支持使用前向糾錯協(xié)議來確保以全流水線速度傳輸有效數(shù)據(jù)。在大多數(shù)設計中,損壞事件通常很少發(fā)生,但是如果沒有外部的糾錯支持,那么對于高度流水線化的加速器設計來說,恢復成本將會很高。

圖2展示了數(shù)據(jù)編排引擎可以通過多種方式優(yōu)化數(shù)據(jù)流和給機器學習引擎提供的呈現(xiàn)結果。例如,單個數(shù)據(jù)元素的格式和結構為利用數(shù)據(jù)編排的優(yōu)勢提供了一個重要的機會,因為源數(shù)據(jù)通常必須以一種適合深度神經網(wǎng)絡(DNN)進行特征提取的格式來表示。

在圖像識別和分類應用中,像素數(shù)據(jù)通常被通道化,以便在通過提取形狀和其他高級信息的池化層進行聚合結果之前,可以單獨處理每個顏色平面。通道化有助于識別邊緣和其他特征,這些特征可能不易于用組合的RGB表示法識別。在語音和語言處理中會執(zhí)行更廣泛的轉換。數(shù)據(jù)通常被映射成一種更容易被DNN處理的形式。由于不是直接處理ASCII或Unicode字符,而是將模型中要處理的詞和子詞轉換為向量和one-hot表示。類似地,語音數(shù)據(jù)可能不會以原始時域樣本的形式呈現(xiàn),而是轉換為聯(lián)合時頻表示,從而使重要特征更容易被早期DNN層識別。

盡管數(shù)據(jù)轉換可以通過人工智能加速器中的算術內核來執(zhí)行,但它可能不太適合張量引擎。重新格式化的性質使其適合由基于FPGA的模塊進行處理。FPGA能夠有效地以線速度進行轉換,而不會出現(xiàn)在通用處理器上運行軟件時所產生的延遲。

在涉及傳感器的實時和嵌入式應用中,預處理數(shù)據(jù)可以帶來更多的好處。例如,雖然可以通過訓練DNN以消除噪聲和環(huán)境條件變化的影響,但使用前端信號處理對數(shù)據(jù)進行去噪或歸一化處理,可提高其可靠性。在汽車先進駕駛輔助系統(tǒng)(ADAS)實現(xiàn)中,攝像頭系統(tǒng)必須處理照明條件的變化。通常,通過使用亮度和對比度調整,可以利用傳感器中高水平的動態(tài)范圍。FPGA可以執(zhí)行必要的操作,為DNN提供變化較少的像素流。

傳感器融合是ADAS設計日益重要的一個方面,有助于提高終端系統(tǒng)的性能。由于環(huán)境條件會使單個傳感器數(shù)據(jù)難以解讀,因此人工智能模型必須有效地從眾多不同類型的傳感器(包括攝像頭、激光雷達和雷達)中獲取輸入。

格式轉換是至關重要的。例如,激光雷達(LIDAR)為笛卡爾空間中的目標物體提供深度信息,而雷達在極坐標系統(tǒng)上運行。許多模型通過將一個坐標空間轉換為另一個坐標空間,更容易地進行傳感器融合。類似地,來自多個攝像頭的圖像數(shù)據(jù)必須拼接在一起,并使用投影進行轉換,從而將最有用的信息傳遞給人工智能模型。

較低級別的轉換也同樣需要。汽車原始設備制造商(OEM)從不同的供應商那里購買傳感器模塊,每個供應商都以自己的方式解讀連接通信標準。這需要一些功能來解析這些傳感器通過車載網(wǎng)絡發(fā)送的數(shù)據(jù)包,并將數(shù)據(jù)轉換為DNN可以處理的標準格式。出于安全考慮,模塊也必須向ADAS單元進行身份驗證,在某些情況下,還要發(fā)送加密數(shù)據(jù)。數(shù)據(jù)編排芯片支持從人工智能加速器引擎上卸載解密和格式轉換功能。

通過使用在數(shù)據(jù)編排子系統(tǒng)中實現(xiàn)的前端信號處理功能來去除不必要的數(shù)據(jù),可以實現(xiàn)進一步的優(yōu)化。例如,用于處理來自麥克風和其他一維傳感器輸入的傳感器,可以消除靜音時或低級背景時的噪音,并減少車輛靜止時傳送的視頻幀數(shù)量,從而減輕人工智能引擎的負載。

圖2:數(shù)據(jù)編排為人工智能功能加速提供了多種選擇

一種針對數(shù)據(jù)編排而優(yōu)化的架構

盡管FPGA內可配置互連和可編程邏輯的結合有助于數(shù)據(jù)編排任務,但FPGA架構則天生各不相同,它們如何處理對高帶寬數(shù)據(jù)的需求是關鍵。傳統(tǒng)上,F(xiàn)PGA并不被期望作為數(shù)據(jù)路徑的核心元素,而是主要為與存儲和I/O交互的處理器提供控制平面輔助。數(shù)據(jù)編排需要代表處理器和加速器去實現(xiàn)內核接收、轉換和管理數(shù)據(jù)元素,這給傳統(tǒng)的FPGA架構帶來了巨大的壓力。

為了支持數(shù)據(jù)編排的帶寬要求,傳統(tǒng)的FPGA需要極寬的總線來處理通過PCI Express和千兆以太網(wǎng)接口的多個數(shù)據(jù)流。例如,為了支持超過400Gb/s以太網(wǎng)數(shù)據(jù)的傳輸,設計人員必須使用可編程的互連電路,來對大約2048位寬的總線進行布線,以可靠地滿足時序要求,這通常需要一個運行頻率為幾百兆赫茲的時鐘。由于這種大型結構的擁塞和時序收斂問題,這樣如此寬的互連是非常難以布線的。互連可能會消耗數(shù)十萬個查找表(LUT),因為它們是無法用于執(zhí)行數(shù)據(jù)編排或格式轉換任務的。

Achronix Speedster7t系列FPGA器件克服了傳統(tǒng)FPGA所面臨的問題,其中部分原因是它采用了一種專用的二維片上網(wǎng)絡(2D NoC),通過在網(wǎng)絡的不同部分進行多個并行操作,這種互連可以實現(xiàn)高達20Tb/s的總帶寬。相對于FPGA架構互連,二維片上網(wǎng)絡不僅在速度上有了巨大的提升,而且能夠在多個PCIe Gen5、400Gbps以太網(wǎng)端口和GDDR6存儲器接口之間以更高的速率傳輸大量的數(shù)據(jù),而不會消耗任何FPGA的可編程資源。

在Speedster7t FPGA器件中,片上網(wǎng)絡在FPGA的整個表面提供了一個二維互連架構。它使用專用的網(wǎng)絡接入點(NAP)將數(shù)據(jù)包發(fā)送到器件內任何位置的軟核。每個NAP通過行業(yè)標準的AXI端口結構提供對FPGA內可編程邏輯模塊或硬件資源的訪問。東西向和南北向數(shù)據(jù)流都有獨立的NAP,為訪問二維片上網(wǎng)絡的邏輯提供了額外的靈活性和性能。這種定向分割有助于優(yōu)化在相同的二維片上網(wǎng)絡路徑上開始和結束的傳輸延遲。在一個正交的二維片上網(wǎng)絡路徑上走線會增加一個小的、確定性的延遲。

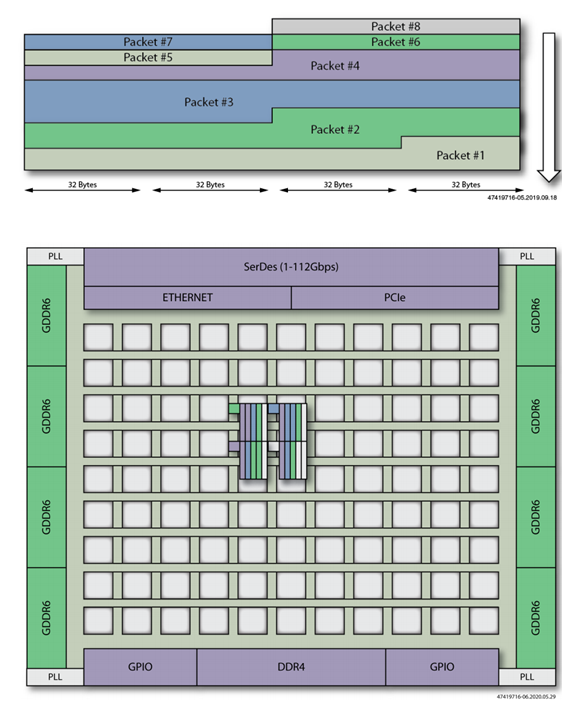

二維片上網(wǎng)絡提供的一項重要功能是分組模式(Packet Mode),該模式旨在更容易地將到達高帶寬端口(如以太網(wǎng))的數(shù)據(jù)重新排列為多個數(shù)據(jù)流。分組模式可以分離到達速率為200Gb/s或400Gb/s以太網(wǎng)端口的數(shù)據(jù)包,并將它們傳輸?shù)讲煌能浐恕_@種數(shù)據(jù)包分離如下圖所示,連續(xù)的數(shù)據(jù)包被分布到FPGA的不同部分。因此,分組模式可以輕松創(chuàng)建負載平衡架構,而使用傳統(tǒng)FPGA是難以實現(xiàn)這樣的功能。

圖3:片上網(wǎng)絡的分組模式支持將網(wǎng)絡有效負載自動分配到架構的不同部分

另一個好處是,二維片上網(wǎng)絡更容易支持部分重新配置:二維陣列中的每個邏輯模塊都能作為一個可隔離的資源,可以在不影響任何其他邏輯模塊的情況下完成交換新功能。由二維片上網(wǎng)絡和接入點控制器實現(xiàn)的虛擬化和轉換邏輯進一步增強了此功能。

地址轉換表的作用類似于微處理器中的存儲管理單元,以防止任務之間的數(shù)據(jù)相互干擾。接入點中的地址轉換表意味著每個軟核可以訪問相同的虛擬地址范圍,但訪問外部物理存儲的范圍完全不同。訪問保護位提供了進一步的安全性,防止內核訪問受保護的地址范圍。在一系列基于人工智能的應用中,這種級別的保護很可能變得極其重要。在這些應用中,數(shù)據(jù)編排和其他可編程邏輯功能在集成到最終產品之前由不同的團隊實現(xiàn)。

除了高度靈活的數(shù)據(jù)路由,數(shù)據(jù)編排還需要去應用快速算術功能來增強核心人工智能加速器。Speedster7t FPGA部署了一系列機器學習處理器(MLP)模塊。每個MLP都是一個高度可配置的、計算密集型的模塊,最多可配置32個乘法器,提供高達60 TOPS的性能。MLP支持4到24位的整數(shù)格式和各種浮點模式,包括直接支持Tensorflow的bfloat16格式和塊浮點(BFP)格式。周圍的可編程邏輯架構提供了多種方法來優(yōu)化數(shù)據(jù)流,以充分利用MLP提供的數(shù)據(jù)重用和吞吐量機會。

由于數(shù)據(jù)編排硬件需要適用于各種應用環(huán)境,因此對靈活部署有著明確的需求。數(shù)據(jù)中心應用可能需要使用一個或多個分立的、大容量器件(例如Speedster7t FPGA器件),來為單個電路板上或分布在一個托盤或機架內的多個機器學習引擎路由和預處理數(shù)據(jù)流。對于尺寸、功耗和成本是主要限制因素的邊緣計算應用來說,采用系統(tǒng)級芯片(SoC)解決方案存在明顯的爭論。

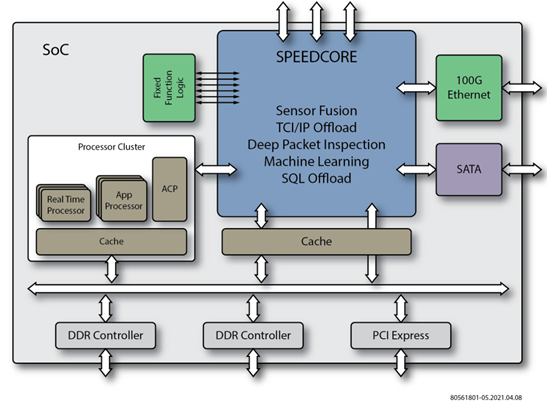

Achronix是唯一一家能夠同時提供獨立FPGA芯片和嵌入式FPGA(eFPGA)半導體知識產權(IP)技術的公司,因此在支持成本降低計劃方面具有獨特的優(yōu)勢,其中可編程邏輯和互連功能可以集成到一個SoC中,如下圖所示。Speedcore eFPGA IP使用與Speedster7t FPGA相同的技術,支持從Speedster7t FPGA到集成Speedcore模塊的ASIC的無縫轉換。當使用Speedcore IP將Speedster7t FPGA轉換為ASIC時,客戶有望降低高達50%的功耗和節(jié)省高達90%的單位成本。

另一種選擇是在多芯片模塊中使用多芯片合封chiplets。這在基于FPGA的合封的數(shù)據(jù)編排模塊和機器學習引擎之間提供了高速互連的好處。Achronix支持所有這些實現(xiàn)選項。

圖4:嵌入式FPGA技術能夠將數(shù)據(jù)編排集成到加速器芯片中

結論

深度學習的快速發(fā)展給大規(guī)模實現(xiàn)該技術所需的硬件架構帶來了巨大壓力。盡管由于意識到性能是一個絕對要求,因此業(yè)界高度關注峰值TOPS分數(shù),但智能數(shù)據(jù)編排和管理策略提供了一種用于交付高成本效益和高能效系統(tǒng)的方法。

數(shù)據(jù)編排包括許多預處理和后處理操作,確保了數(shù)據(jù)以最佳速度和最適合進行高效處理的格式傳輸?shù)綑C器學習引擎。操作范圍從資源管理和使用規(guī)劃,到I/O適配、轉碼、轉換和傳感器融合,再到共享存儲陣列內的數(shù)據(jù)壓縮和重新排列。一些編排引擎根據(jù)目標機器學習架構的核心需求使用這些功能的子集。

Achronix Speedster7t FPGA架構為這些數(shù)據(jù)編排策略提供了高度靈活的平臺。這種FPGA具有高吞吐量、低延遲和極高靈活性等特點,其數(shù)據(jù)傳輸形式可使即使是高度專業(yè)化的加速器也能去適應不斷變化的需求。此外,Speedster7t FPGA廣泛的邏輯和算術能力加上高吞吐量互連,使得前端信號調節(jié)和后端機器學習的整體設計能夠最大限度地提高整體效率。