當(dāng)今世界已經(jīng)到處都是功能繁多和性能卓越的,以往只出現(xiàn)在科幻小說里的高科技產(chǎn)物。當(dāng)我們使用聯(lián)網(wǎng)設(shè)備并使用可以媲美過去的“超級計算機(jī)”的手機(jī)拍攝高清照片時,很少有人會考慮其中的底層技術(shù)。

而更加鮮為人知的是,產(chǎn)品規(guī)格與市場需求的相互作用所形成的矛盾愈趨強(qiáng)烈與復(fù)雜,使得產(chǎn)品迭代的設(shè)計生產(chǎn)與相關(guān)投入產(chǎn)出的合理性,也變得愈發(fā)棘手。

對具有更低功耗和更多功能的小型設(shè)備的不懈追求,推動了對更高集成度的需求。因此,這需要更小的硅片尺寸,要求設(shè)計人員采用 28nm、16nm、12nm、7nm、5nm 及更精微的工藝。

而每一次硅工藝的更新,對設(shè)計和制造成本都會帶來非線性增長。基于精微工藝的設(shè)計需要越來越稀缺的專業(yè)知識、更長的設(shè)計時間、更昂貴的設(shè)計工具,并帶來更高的程序風(fēng)險。

這些呈指數(shù)增長的設(shè)計成本必須由項(xiàng)目生命周期內(nèi)出貨的產(chǎn)品分?jǐn)偂2恍业氖牵S著全球競爭的加劇、應(yīng)用功能多樣性在增加、而產(chǎn)品的生命周期卻在縮短。因此,符合經(jīng)濟(jì)效益的定制型芯片項(xiàng)目越來越少,同時能匯聚這些愈發(fā)稀缺的人才的公司也越來越少。

至少從理論上講,諸如 FPGA 之類的可重新編程技術(shù)可以緩解其中的許多問題,但傳統(tǒng)的 FPGA 體積大、效率低且價格昂貴,通常只用來做原型驗(yàn)證和調(diào)試。易靈思 通過生產(chǎn)低功耗、高效、密度足以運(yùn)行計算密集型任務(wù)、且為大批量采用定價的FPGA,直接滿足了這些相互制掣的動態(tài)市場需求。

本文討論了 AI 硬件設(shè)計和部署背后的經(jīng)濟(jì)學(xué),將其優(yōu)勢和考慮與 易靈思 的 FPGA 技術(shù)聯(lián)系起來,闡明了當(dāng)有更好的硬件平臺可選時,芯片設(shè)計和制造的巨額成本與負(fù)擔(dān)如何變得越來越不合理。

定制硅的巨大成本——細(xì)細(xì)道來

從頭開始設(shè)計芯片,從成本、專業(yè)知識和時間角度來看,需要幾乎無法估量的投資;最終,IC/芯片設(shè)計只能交由在此領(lǐng)域具有持續(xù)積累的公司。有時,一群懷才不遇的工程師會從一家大公司出來,創(chuàng)建一家初創(chuàng)公司并制造 IP。然而,進(jìn)入的門檻通常如此之高,以至于新想法甫一出世,就立馬夭折了。

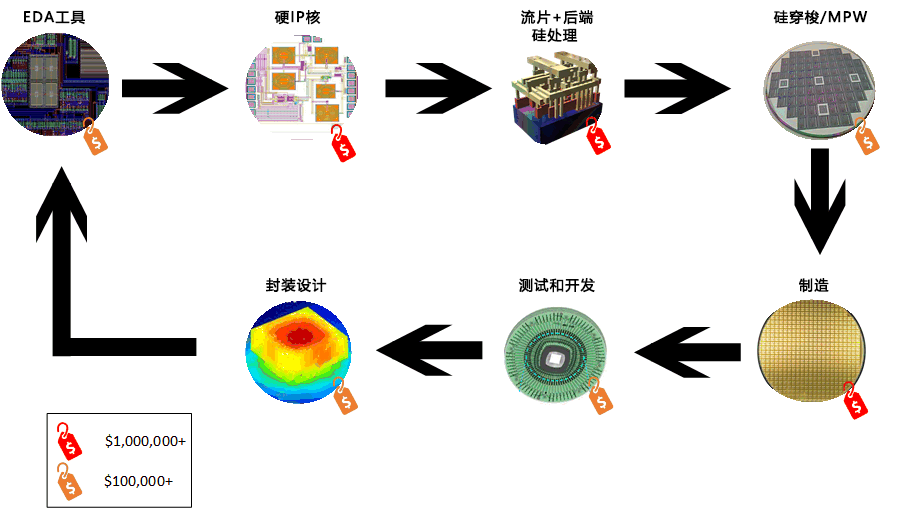

這種硬件“障礙”從本質(zhì)上扼殺了創(chuàng)新,尤其是在新興的計算密集型 AI 領(lǐng)域;在該領(lǐng)域,特別是每個垂直行業(yè)的關(guān)鍵和非關(guān)鍵任務(wù)的應(yīng)用層出不窮。這種軟件所需的處理能力具有復(fù)雜、計算密集、高耗電、且總在更新等特征。通常情況下,用定制芯片來支持這些不斷變化的需求,其成本是不合理的(圖 1)。

設(shè)計開發(fā)成本

首先,需要電子設(shè)計自動化 (EDA)軟件來執(zhí)行基本的 IC 和布局設(shè)計、模擬和驗(yàn)證。EDA 軟件生態(tài)系統(tǒng)為設(shè)計流程的各個方面提供了豐富的工具,可以在預(yù)期框架內(nèi)優(yōu)化設(shè)計。EDA軟件的價格高昂,單個授權(quán)每年的費(fèi)用從數(shù)萬美元到數(shù)十萬美元。考慮到要用在數(shù)十到數(shù)百臺機(jī)器上,相應(yīng)成倍增加的費(fèi)用、會輕易突破百萬美元大關(guān)。

這只是涉足芯片制造成本的一方面。為了生成最終產(chǎn)品,公司可能會購買 模擬或數(shù)字的軟硬核IP,以將特殊的 I/O 功能集成到他們的設(shè)計中。IP核開發(fā)行業(yè)本身就是個價值數(shù)十億美元的產(chǎn)業(yè);

正因如此,購買IP的成本也將輕易突破百萬美元量級。如果一家公司資金充裕,那么購買來自專業(yè)無晶圓廠半導(dǎo)體公司的硅片級 IP, 比花費(fèi)時間和工程開工費(fèi)(NRE),在企業(yè)內(nèi)部自己做IP要簡單和快捷得多。

制造成本

完成芯片設(shè)計是一項(xiàng)艱巨工作,其中流片過程需要工程師團(tuán)隊(duì)在廣泛的全局模擬、分析、關(guān)鍵設(shè)計審查、電路迭代/布局改進(jìn)和掩模數(shù)據(jù)準(zhǔn)備后才簽發(fā),以確保設(shè)計的可制造性并生成光掩模的最終 GDSII 文件。隨著晶體管尺寸的縮小,光掩模的質(zhì)量對于精確制造最初設(shè)計的芯片至關(guān)重要。

整個過程很容易出錯,因?yàn)樗菑能浖O(shè)計到芯片生成的轉(zhuǎn)變。公司在這種耗資數(shù)百萬美元的制造過程中投入巨資,通常會依靠多項(xiàng)目晶圓 (MPW,又稱為silicon“shuttle”)來降低風(fēng)險。

它們允許設(shè)計公司通過購買部分 MPW 并與多方分?jǐn)偪傃谀3杀荆诹髌吧a(chǎn)該芯片的樣片。這些選擇允許 IC 公司在完全流片投資之前,拿到并驗(yàn)證幾千個樣片。

測試和封裝成本

為了最大限度地提高新型堆疊芯片級封裝 (SCSP)和系統(tǒng)級封裝 (SiP)設(shè)計的良率,供應(yīng)商要求芯片制造商提供已知良好的裸片(KGD)。雖然這會增加裸片的成本,但最終會降低封裝缺陷器件的成本。

裸片測試是個棘手過程,涉及定制的測試卡,其中數(shù)以千計的探針壓在微凸塊上,通過電壓、電流和溫度應(yīng)力測試來測試缺陷。有缺陷的裸片被封存,而 KGD 被運(yùn)到封裝廠進(jìn)行組裝。所有這些額外的步驟都伴隨著額外的成本考慮。封裝裸片本身是門科學(xué),既有寄生電感和電容、也有嚴(yán)格的熱管理考慮。

電-熱協(xié)同仿真對于檢測和優(yōu)化熱問題是必要的,這又為最終設(shè)計增加了另一層次的復(fù)雜性和專業(yè)知識。熱分析后,封裝廠交付測試好的器件準(zhǔn)備組裝。但是,經(jīng)常會出現(xiàn)硬件/軟件升級的情況,這時,整個過程將從頭再來。這令整個流程的成本飛漲,致使較小玩家無法進(jìn)入 ASIC 或 IP 設(shè)計領(lǐng)域。

圖 1:圍繞定制芯片的設(shè)計和開發(fā)過程及其相關(guān)成本

滿足 AI 成本和計算需求的當(dāng)前解決方案

摩爾定律的崩潰:更小的器件幾何尺度背后的挑戰(zhàn)

摩爾定律的明顯放緩進(jìn)一步加劇了出品定制芯片的不可行性,從而使晶體管尺寸和功率密度呈指數(shù)級改良的黃金時代已止步不前。遵循此邏輯,為滿足芯片越來越高的性能要求,制造商不得不轉(zhuǎn)向制造大芯片。

然而,隨著芯片尺寸的增加,缺陷和錯誤制造的風(fēng)險會增加,良率就會下降。這促使半導(dǎo)體制造商和設(shè)計公司尋求其它可行的解決方案,包括將單片 IC 的功能分解為互連的較小芯片,以執(zhí)行計算密集型處理。

小芯片

小型器件的封裝在 1980 年代,已從多芯片模組(MCM)發(fā)展到系統(tǒng)級封裝設(shè)計,再到現(xiàn)在的小芯片。在小芯片設(shè)計中,原本的“大芯片”被劃分為定制設(shè)計的、硬化的 IP 模塊(或較小的裸芯),它們可被更經(jīng)濟(jì)地制造。

這些小芯片與其它模塊共同優(yōu)化,并通過標(biāo)準(zhǔn)化接口連接,猶如SoC 的功能,但以更低成本和更短時間構(gòu)建。裸芯可以由不同的工藝建構(gòu),其中一些采用更經(jīng)濟(jì)的 28nm工藝,或者最新最尖端的 7nm(或更精微)光刻工藝。

而封裝的拓?fù)浣Y(jié)構(gòu)則可以是基于 TSV 的硅中介層(2.5D)、堆疊芯片(3D)、嵌入式多芯片互連橋 (2.5D)或扇出 MCM 等。

與制造大型 SoC 并試圖通過加進(jìn)更多功能和性能來更新技術(shù)相比,基于小芯片的 ASIC 更具成本效益。理論上,每個模塊都有可能被重用或擴(kuò)展用于未來的硬件設(shè)計迭代;其中芯片到芯片的標(biāo)準(zhǔn)化接口可實(shí)現(xiàn)模塊之間的互操作性,從而縮短上市時間。

從設(shè)計角度看,這種易于升級的能力不容忽視——庫中易于取用的已成熟的芯片設(shè)計可與其它小芯片混合和匹配,以形成一個新系統(tǒng)。在實(shí)踐中,定義良好的標(biāo)準(zhǔn)接口只占少數(shù)。

仍然有許多未標(biāo)準(zhǔn)化的接口對采用來自第三方的小芯片庫造成障礙,因?yàn)檫@些第三方根本不知道要使用什么標(biāo)準(zhǔn)進(jìn)行設(shè)計且只能承受選擇其中的一個。通常,這些接口的速度非常快,因此往往會推動封裝設(shè)計朝著更昂貴的方向發(fā)展。

小芯片設(shè)計是一項(xiàng)相對新的技術(shù),其中大部分知識由大型芯片開發(fā)商和制造商掌握。對于芯片設(shè)計人員來說,在未來的 ASIC 項(xiàng)目中使用小芯片具有很大潛力。

這種新的設(shè)計方法在一定程度上規(guī)避了越來越棘手的成本和開發(fā)時間瓶頸。然而,對于那些沒有實(shí)力投資于生成和優(yōu)化小芯片所需資源的公司來說,這條路并不行得通。

嵌入式處理器

通常,最能讓設(shè)計人員隨意使用的工具是標(biāo)準(zhǔn)嵌入式處理器并盡可能多地用軟件進(jìn)行設(shè)計,僅在必要時才訴諸硬件。這樣,已定義好的標(biāo)準(zhǔn)和功能使標(biāo)準(zhǔn)硬件器件可跨多個市場使用,以積累所需的數(shù)量。

設(shè)計人員只能在軟件中盡可能多地實(shí)現(xiàn)功能,并在必要時連接少量膠合邏輯和外圍器件。在某些情況下,模型分區(qū)是跨多個內(nèi)核完成的,以加快并行處理時間。GPU 是當(dāng)前深度神經(jīng)網(wǎng)絡(luò)(DNN)訓(xùn)練的寵兒。這也帶來了若干挑戰(zhàn)。

首先,需要一個復(fù)雜的控制單元,而且經(jīng)常有冗余內(nèi)存訪問,導(dǎo)致系統(tǒng)功耗上升。其次,由于這些處理器的通用性本質(zhì),基于特定DNN 算法的硬件優(yōu)化難以見到。第三,對 ML 算法的升級和更改就變得難以實(shí)施,從而尋求更多的處理能力。綜上,充其量,這是種不得已的折中;理想情況下,處理器和加速器應(yīng)位于同一硅片。這樣,可以快速優(yōu)化系統(tǒng)性能。

使用 FPGA 進(jìn)行硬件加速的成本和計算優(yōu)勢

將 ML 算法映射到硬件是個復(fù)雜過程,牽涉到數(shù)據(jù)準(zhǔn)確性、吞吐量、延遲、功耗、硬件成本、靈活性和可擴(kuò)展性之間的權(quán)衡和取舍。通過投入更多處理內(nèi)核的方式解決問題,很快就會變得不切實(shí)際,特別是如果問題涉及成本和功耗。

在 FPGA 上實(shí)現(xiàn)硬件加速比使用嵌入式處理器要簡單得多,這是由于硬件架構(gòu)的根本差異。CPU和GPU只能實(shí)現(xiàn)數(shù)據(jù)并行,而FPGA(和ASIC)提供數(shù)據(jù)和流水線并行。

在 CPU 或 GPU 中,每個處理器根據(jù)單指令、多數(shù)據(jù)運(yùn)行模型執(zhí)行相同的任務(wù),對不同的分布式數(shù)據(jù)執(zhí)行相同任務(wù),或者處理單元(PE)在每個時鐘周期執(zhí)行相同操作,同時對數(shù)據(jù)進(jìn)行分區(qū)并并行分發(fā)給各PE。

在 FPGA(和 ASIC)中,指令集中的不同任務(wù)可以在每個時鐘周期并發(fā)執(zhí)行,從而流水線中的每個 PE 可以并行獲取具有不同時間戳的數(shù)據(jù)。這為具有數(shù)據(jù)并發(fā)性和依賴性的 DNN 提供了快速的硬件加速。

為了更好地形象化表述這點(diǎn),可以實(shí)際的托盤壓印工廠作為示例。工廠通過切割、壓印和貼標(biāo)簽來處理托盤。CPU 或 GPU 可能處理一大排托盤。然而,每一行在進(jìn)行壓印之前都會經(jīng)歷相同的切割操作。

壓印一行后,下一個時鐘周期將專門于對其標(biāo)記。另一方面,F(xiàn)PGA 將能夠同時處理多排托盤——當(dāng)一排托盤被切割時、另一排被壓印、另一排被標(biāo)記,所有這些都在同一個時鐘周期內(nèi)實(shí)現(xiàn)。通過這種方式,可以充分利用 FPGA 流水線,使其本質(zhì)上更高效。

DNN 計算和數(shù)據(jù)移動的優(yōu)化技術(shù)可以在 FPGA 硬件上更好地實(shí)現(xiàn)。FPGA 允許設(shè)計人員處理適合特定應(yīng)用的數(shù)據(jù)包大小,且可為應(yīng)用精準(zhǔn)匹配和調(diào)整通信協(xié)議和拓?fù)洹?/p>

與 ASIC 相比,F(xiàn)PGA 還為 AI 提供了重要優(yōu)勢。無論制造商是否使用了更具成本效益的小芯片封裝技術(shù),一旦 ASIC 被制造出來,設(shè)計人員或多或少會被計算的數(shù)據(jù)類型以及由器件到其外圍設(shè)備的數(shù)據(jù)流的性質(zhì)所困擾。

FPGA 提供了一個更通用的平臺,它提供了 ASIC 的流水線并行能力,且沒有基于特定應(yīng)用的傾向性、電路固化和高成本等缺憾。FPGA 還受益于使用尖端電路設(shè)計、制造、晶圓加工和封裝技術(shù)的最先進(jìn)工藝帶來的好處。越來越多的 FPGA 使用 FinFET 技術(shù)構(gòu)建在 16nm或更精微的工藝節(jié)點(diǎn)1。

但是,最終用戶可以或多或少地從這種先進(jìn)工藝的成本負(fù)擔(dān)中得到紓解。因?yàn)榕c模擬/混合信號 IC、布局、信號完整性、電源完整性和半導(dǎo)體封裝工程師團(tuán)隊(duì)相比,獲得 掌握VHDL技術(shù)的人才 不僅便宜得多,也要容易得多。

軟 IP 核本身只是硬 IP 核成本的一小部分,比硬件過時相關(guān)的成本風(fēng)險要小得多,因只要應(yīng)用需求發(fā)生變化,I/O 接口也會隨之變化。

FPGA 生態(tài)系統(tǒng)概覽

到 2026 年,全球 FPGA 市場預(yù)計將超過 90 億美元,其中大部分增長歸功于數(shù)據(jù)中心和高性能計算應(yīng)用。現(xiàn)代 FPGA 市場主要由計算頻譜的兩個極端來驅(qū)動:一端是高端、高耗電的 FPGA;另一端是低端、膠合邏輯 FPGA(圖 2)。

在 1980 年代,F(xiàn)PGA 在具有晶體管-晶體管邏輯 (TTL) 的膠合邏輯中找到了自己的利基市場——用于快速設(shè)計和系統(tǒng)原型設(shè)計,將 IP 與通用 I/O 協(xié)議和通信接口“膠合”在一起。

近十年后,F(xiàn)PGA 變得越來越復(fù)雜,引入了大型 SRAM 模塊、嵌入式數(shù)字信號處理 (DSP)模塊中的乘法器-累加器、嵌入式處理器軟核、I/O 和 SerDes 接口。

這為之前由 CPU、GPU 和 SoC 主導(dǎo)的市場帶來了一定程度的設(shè)計靈活性,它能夠通過可重新配置的平臺生成軟 IP。數(shù)據(jù)中心開始利用功能強(qiáng)大的高端 FPGA 來提升大規(guī)模數(shù)據(jù)系統(tǒng)的性能,用于加密、壓縮、過濾和虛擬交換,作為從多核處理的一種轉(zhuǎn)變。

這形成了性能和計算效率之間的平衡以及可重構(gòu)性的額外巨大優(yōu)勢。深度學(xué)習(xí)網(wǎng)絡(luò)正處于由新的層類型和不斷變化的數(shù)據(jù)集驅(qū)動的不斷升級的過程中。基于該原因,F(xiàn)PGA 被寄予厚望、用于推理的可編程加速器。

FGPA 已被證明是通過優(yōu)化數(shù)據(jù)移動、修剪網(wǎng)絡(luò)、降低算術(shù)精度和稀疏化(sparsification)來有效實(shí)現(xiàn) DL 算法的強(qiáng)大工具。

在這個不斷增長的AI應(yīng)用生態(tài)系統(tǒng)中——更新的模型、優(yōu)化技術(shù)和支持硬件加速——低端和高端 FPGA 之間的差距越來越明顯。

自動航空機(jī)載和地面車輛、醫(yī)療保健、視覺識別、欺詐檢測以及更多應(yīng)用的機(jī)會將不可避免地需要完全相同的可重新配置平臺,但要求采用更具成本效益、耗電更少的封裝。

圖 2:FPGA 及其潛在應(yīng)用

使用可定制、經(jīng)濟(jì)高效的 FPGA 打破定制芯片的束縛

本文主旨是揭示研制定制芯片的成本和專業(yè)知識方面的困難。可以在市場上競爭并最終推動適合 AI 小芯片的價格點(diǎn)和硬件能力的芯片制造商,幾乎組成了一個排他俱樂部。

大行其道的通用 CPU 和 GPU 解決方案非常適合某些 AI 應(yīng)用,但在其它應(yīng)用中存在固有限制,這進(jìn)一步限制了開發(fā)人員可用的解決方案。而易靈思的 FPGA 就非常適合需要低功耗、低延遲、低成本、小尺寸和易于開發(fā)的 AI 應(yīng)用。

使用易靈思量子計算結(jié)構(gòu)的 FPGA 體積小、功耗低且高效。它們是按批量級別來定價,其中最低端型號起價不超過 10 美元,開發(fā)套件起價為 48 美元(圖 3)。這些是預(yù)定義的標(biāo)準(zhǔn)產(chǎn)品,并且通過易靈思平臺進(jìn)行了硬件加速、需要零 NRE,從而將上市時間縮短數(shù)年并可節(jié)省數(shù)百萬美元的開發(fā)成本。

這些新的經(jīng)濟(jì)方面的好處,重啟了曾因芯片開發(fā)成本而被窒息的可能性。它們的可重新編程特性確保了快速調(diào)試、降低了程序風(fēng)險,且使最終的設(shè)計在現(xiàn)場部署之前(及之后)保有靈活性。

設(shè)計人員可“免費(fèi)”創(chuàng)新,可在每個產(chǎn)品的基礎(chǔ)上實(shí)現(xiàn)自定義功能,在標(biāo)準(zhǔn)芯片平臺中通過創(chuàng)新功能、區(qū)分產(chǎn)品 SKU。這之所以成為可能,是因?yàn)橐嘴`思量子結(jié)構(gòu)的突破性效率將高性能注入了主流市場。

圖 3:[一種比較其它流行 FPGA方案、關(guān)鍵 FPGA 參數(shù)(例如,LE 數(shù)量、大小、成本、外設(shè)數(shù)量等)的可能對比]

鈦金系列的規(guī)格概覽(圖 4)呈現(xiàn)了高密度計算架構(gòu)與 DSP 模塊、高速 I/O 和收發(fā)器接口的集成,以滿足從低功耗小尺寸的邊緣應(yīng)用到高性能工業(yè)自動化和嵌入式視覺應(yīng)用的廣泛需求。

這種 LE的密度與尺寸比形成了 FPGA 應(yīng)用的新視野。易靈思的設(shè)計足夠小、功能足夠強(qiáng)大,既可以替代傳統(tǒng)的低端 FPGA(這些 FPGA 太小而無法容納完整的設(shè)計、因此用作橋接器件);又可以取代將小型 FPGA膠合在一起的完全定制芯片。

圖 4:鈦金FPGA規(guī)范

易靈思 量子結(jié)構(gòu)中的動態(tài)硬件和軟件分區(qū)

易靈思 FPGA 設(shè)計流程還采用了現(xiàn)在熟悉的開發(fā)方法,即在系統(tǒng)設(shè)計時最大程度地使用軟件,僅在需要提高性能的地方訴諸硬件。開源和軟件定義的 RISC-V 處理器可以在 FPGA 內(nèi)免費(fèi)實(shí)例化。

它仿佛為設(shè)計人員提供了加速器的“插座”,把部分 C/C++ 代碼通過插入些小塊的硬件來加速執(zhí)行。并且可以在同一個可配置結(jié)構(gòu)中實(shí)現(xiàn)動態(tài)硬件和軟件分區(qū),以實(shí)現(xiàn)最佳性能和效率、加快上市時間并降低開發(fā)成本。

RISC-V 指令集架構(gòu)從它在加州大學(xué)伯克利分校低調(diào)的濫觴至今,已經(jīng)有了巨大發(fā)展。作為 RISC-V 計劃的直接結(jié)果,現(xiàn)在已有一組豐富的開源軟核。

因此,它已成為全域 AI 供應(yīng)商(從商業(yè)科技巨頭到美國軍方)越來越受歡迎的芯片架構(gòu),與流行的 Arm 和 x86 架構(gòu)競爭2。

與許多開源軟件/硬件平臺一樣,該新興的 RISC-V 生態(tài)系統(tǒng)通過更高效、更安全的設(shè)計促進(jìn)了更多協(xié)作。此舉降低了設(shè)計人員進(jìn)入市場的障礙,能夠?qū)嵗罱咏囟☉?yīng)用需求的 RISC-V 實(shí)現(xiàn)并相應(yīng)地對其進(jìn)行配置。

設(shè)計人員可以在處理器上開發(fā) C 代碼,當(dāng)運(yùn)行不可避免地變得太慢時,可以輕松地逐步將任何瓶頸遷移到 FPGA 中實(shí)現(xiàn),直到滿足所需的系統(tǒng)性能。

如果沒有 FPGA 平臺,這種直接的硬件加速很難實(shí)現(xiàn)——即使在現(xiàn)場部署設(shè)備后,用戶仍然可以使用該功能。

結(jié)論

在更精微的芯片工藝的實(shí)現(xiàn)成本變得非線性飆升的情況下,持續(xù)的芯片工藝迭代變得越來越難以證明其合理性。然而,加大的集成度增加了封裝的復(fù)雜性和成本。這種復(fù)雜性的增加會導(dǎo)致設(shè)計時間延長、費(fèi)用增加。

由于這些因素,從 IC 的批量生產(chǎn)中獲得的利潤在下降。首先,競爭的加劇為消費(fèi)者提供了更多選擇,從而減少了每款產(chǎn)品的出貨量。競爭的加劇還縮短了產(chǎn)品的使用壽命和供貨周期。

新的計算密集型節(jié)點(diǎn)和技術(shù)必須越來越敏捷,不僅要支持不斷變化的市場需求,還要跟上深度學(xué)習(xí)模型的升級。對于很多復(fù)雜度適中的人工智能應(yīng)用,由于缺乏合適的 FPGA,導(dǎo)致設(shè)計人員只能依賴定制小芯片或嵌入式處理器進(jìn)行硬件加速。

易靈思 肇始的新 FPGA 經(jīng)濟(jì)視野,使設(shè)計人員能夠在一個將為社會帶來革命性利益的領(lǐng)域中更靈活地進(jìn)行創(chuàng)新。這可以說是千載難逢的量子劇變,為產(chǎn)品設(shè)計的可能性提供了這樣一個拐點(diǎn)——遠(yuǎn)離定制芯片的死胡同,進(jìn)入任運(yùn)揮灑的定制FPGA 的新篇章。