計算隔離式精密高速DAQ的采樣時鐘抖動的簡單步驟

2022-03-17

作者:Lloben Paculanan,ADI應用開發(fā)工程師 John Neeko Garlitos,ADI產(chǎn)品應用工程師

來源:ADI公司

簡介

出于魯棒性、安全性、高共模電壓考量,或為了消除可在測量中帶來誤差的接地環(huán)路,許多數(shù)據(jù)采集(DAQ)應用都需要隔離DAQ信號鏈路徑。ADI的精密高速技術(shù)使系統(tǒng)設計人員能夠在相同的設計中實現(xiàn)高交流和直流精度,無需犧牲直流精度來換取更高的采樣速率。然而,為實現(xiàn)高交流性能,如信噪比(SNR),系統(tǒng)設計人員必須考慮采樣時鐘信號或控制ADC中采樣保持(S&H)開關(guān)的轉(zhuǎn)換啟動信號上的抖動所帶來的誤差。隨著目標信號和采樣速率的增加,控制采樣保持開關(guān)的信號抖動會成為主要誤差源。

當DAQ信號鏈被隔離之后,控制采樣保持開關(guān)的信號一般來自進行多通道同步采樣的背板。系統(tǒng)設計人員選擇低抖動數(shù)字隔離器至關(guān)重要,以使進入ADC的采樣保持開關(guān)的控制信號具有低抖動。精密高速ADC應首選使用LVDS接口格式,以滿足高數(shù)據(jù)速率要求。它還會對DAQ電源層和接地層帶來極小的干擾。本文將說明如何解讀ADI公司的LVDS數(shù)字隔離器的抖動規(guī)格參數(shù),以及與精密高速產(chǎn)品(例如ADAQ23875DAQ μModule?解決方案)接口時,哪些規(guī)格參數(shù)比較重要。本文的這些指導說明也適用于其他帶有LVDS接口的精密高速ADC。在介紹與ADN4654千兆LVDS隔離器配合使用的ADAQ23875時,還將說明計算對SNR預期影響采用的方法。

抖動如何影響采樣過程

通常,時鐘源在時域中存在抖動。在設計DAQ系統(tǒng)時,了解時鐘源中包含多少抖動是非常重要的。

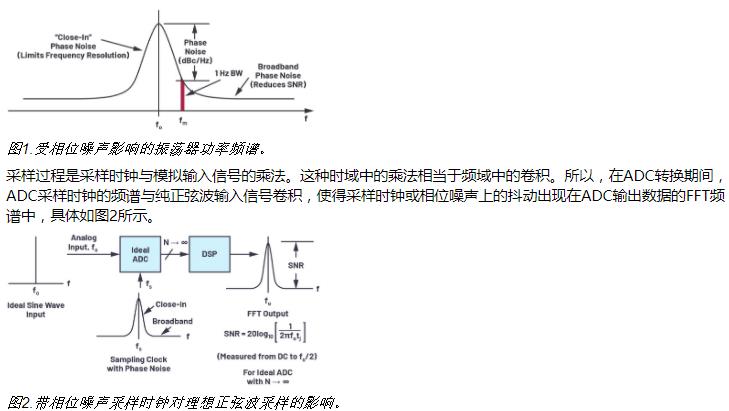

圖1展示了非理想型振蕩器的典型輸出頻譜,在1 Hz帶寬時噪聲功率與頻率成函數(shù)關(guān)系。相位噪聲的定義為指定頻率偏移fm下1 Hz帶寬內(nèi)的噪聲與基波頻率fo下振蕩器信號幅度的比率。

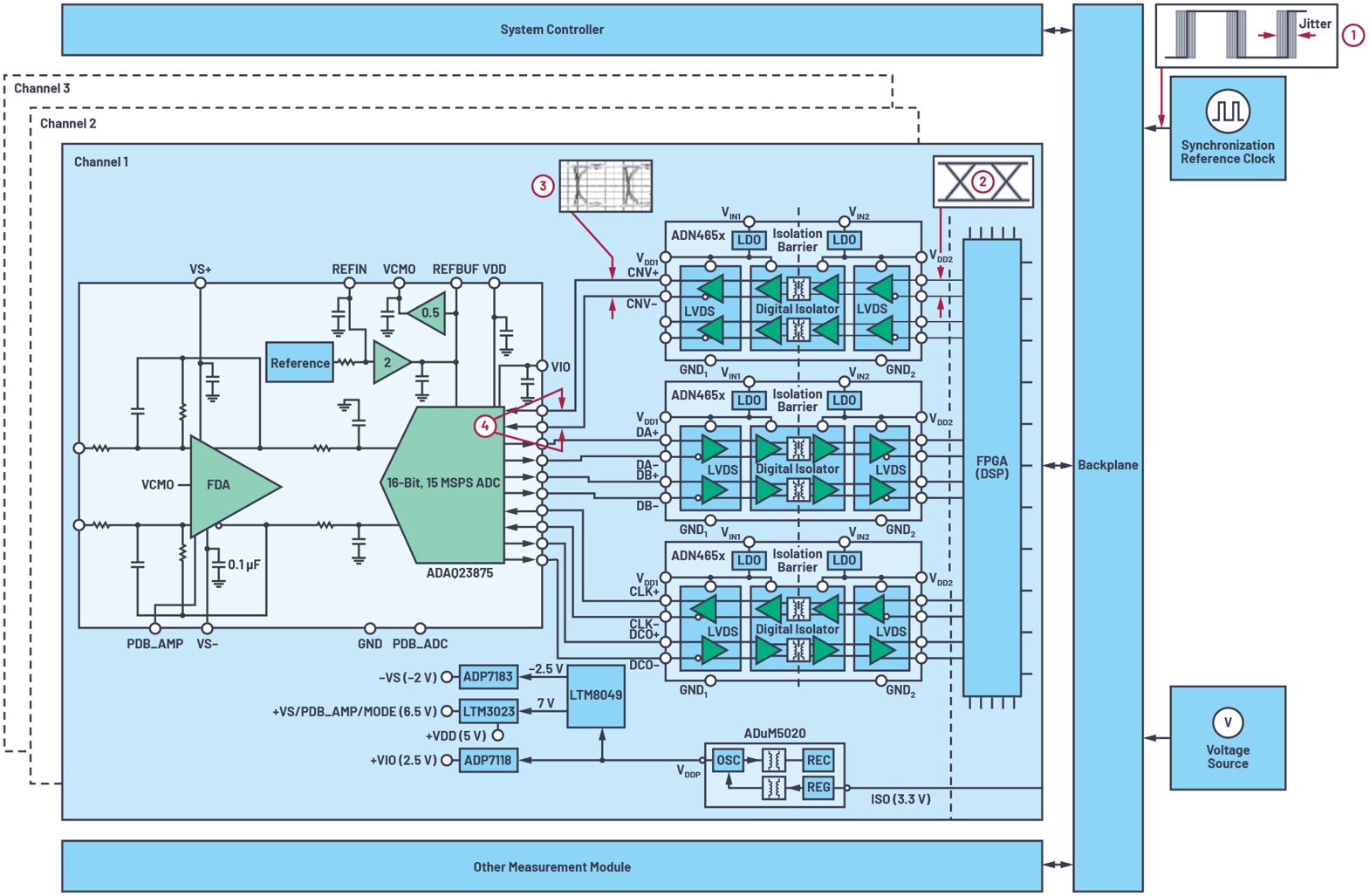

隔離式精密高速DAQ應用

多相功率分析儀就是一個隔離式精密高速DAQ應用示例。圖3顯示典型的系統(tǒng)架構(gòu),其中通道與通道之間隔離,通過共用背板用于與系統(tǒng)計算或控制器模塊通信。在本示例中,我們選擇ADAQ23875精密高速DAQ解決方案,因為其尺寸小,所以能夠在狹小空間內(nèi)輕松安裝多個隔離DAQ通道,從而可以減輕現(xiàn)場測試應用中移動儀器的重量。使用LVDS千兆隔離器(ADN4654)將DAQ通道與主機箱背板隔離。

通過隔離每個DAQ通道,可以在不損壞輸入電路的情況下,將每個通道直接連接至具有不同共模電壓的傳感器。每個隔離DAQ通道的接地跟蹤具有一定電壓偏移的共模電壓。如果DAQ信號鏈能夠跟蹤與傳感器相關(guān)的共模電壓,就無需使用輸入信號調(diào)理電路來支持較大的輸入共模電壓,并消除對下游電路來說較高的共模電壓。這種隔離還可帶來安全性,并消除可能會影響測量精度的接地環(huán)路。

在功率分析儀應用中,在所有DAQ通道中實現(xiàn)采樣事件同步至關(guān)重要,因為與采樣電壓相關(guān)的時域信息不匹配會影響后續(xù)計算和分析。為了在通道間同步采樣事件,ADC采樣時鐘通過LVDS隔離器從背板發(fā)出。

在圖3所示的隔離式DAQ架構(gòu)中,以下這些抖動誤差源會增加控制ADC中采樣保持開關(guān)的采樣時鐘上的總抖動。

1.參考時鐘抖動

采樣時鐘抖動的第一來源是參考時鐘。該參考時鐘通過背板傳輸至每個隔離式精密高速DAQ模塊和其他插入背板的測量模塊。該時鐘用作FPGA的時序參考;所以,F(xiàn)PGA中的所有事件、數(shù)字模塊、PLL等的時序精度都取決于參考時鐘的精度。在沒有背板的某些應用中,使用板載時鐘振蕩器作為參考時鐘源。

2.FPGA抖動

采樣時鐘抖動的第二來源是FPGA帶來的抖動。注意,F(xiàn)PGA中包含一條觸發(fā)-執(zhí)行路徑,并且FPGA中PLL和其他數(shù)據(jù)模塊的抖動規(guī)格都會影響系統(tǒng)的整體抖動性能。

3.LVDS隔離器抖動

采樣時鐘抖動的第三來源是LVDS隔離器。LVDS隔離器產(chǎn)生附加相位抖動,會影響系統(tǒng)的整體抖動性能。

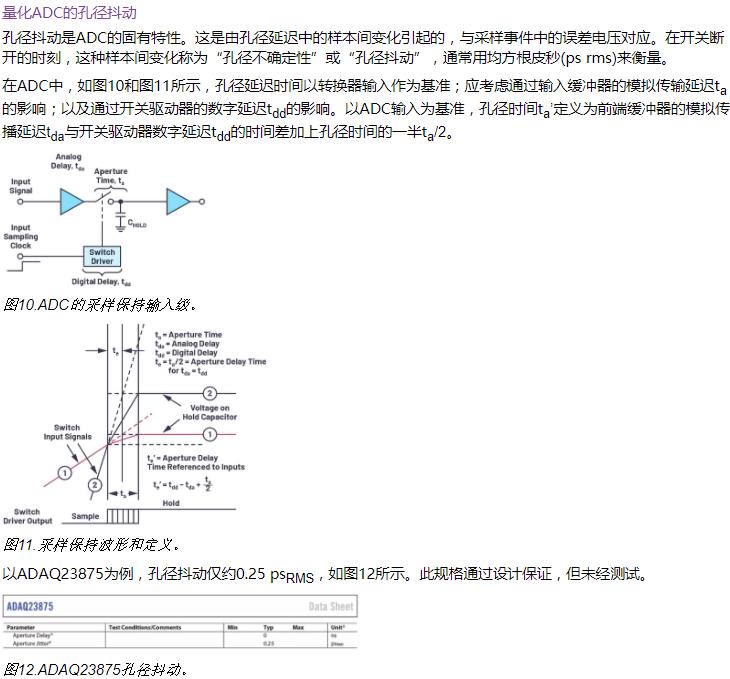

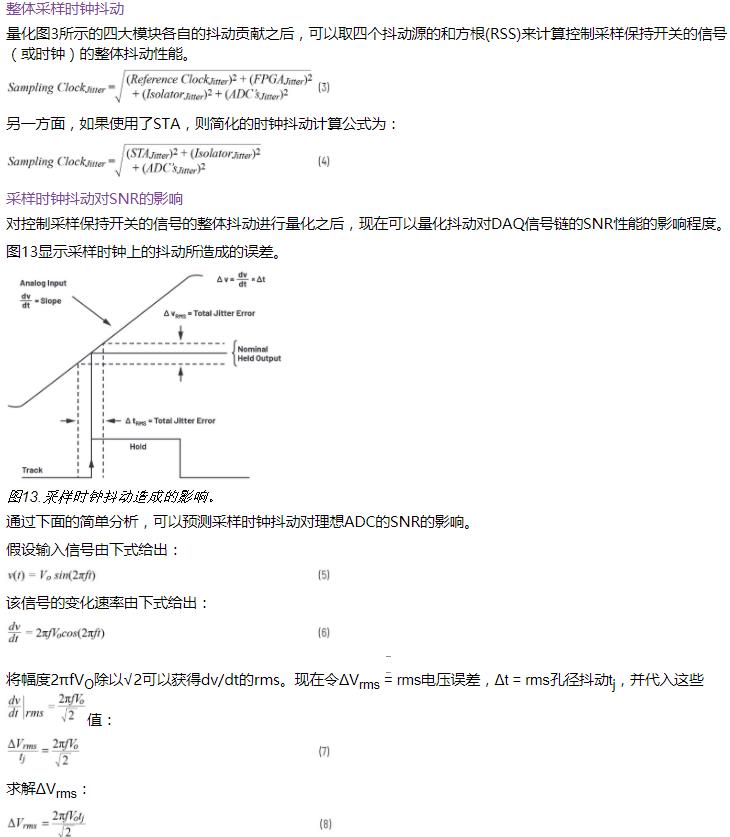

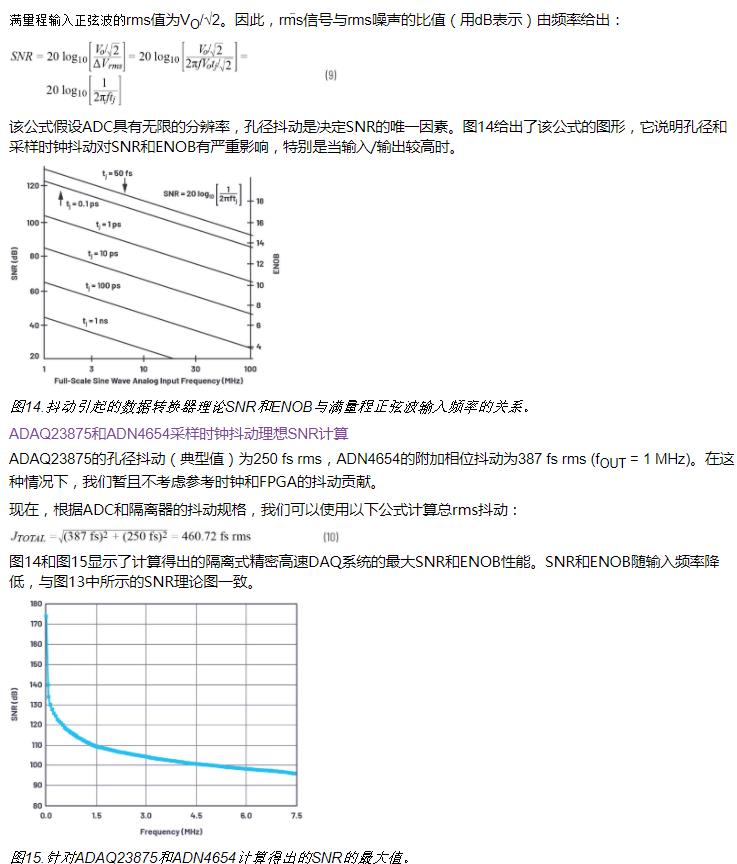

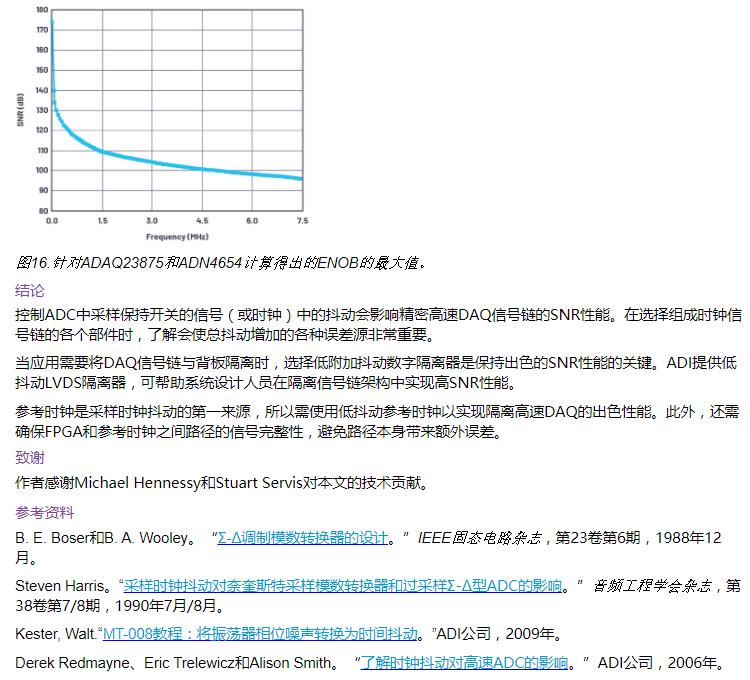

4.ADC的孔徑抖動

采樣時鐘抖動的第四來源是ADC的孔徑抖動。這是ADC本身固有的特性,請參閱數(shù)據(jù)手冊查看具體定義。

圖3.通道與通道之間的隔離DAQ架構(gòu)

有些參考時鐘和FPGA抖動規(guī)格基于相位噪聲給出。要計算對采樣時鐘的抖動貢獻,需要將頻域中的相位噪聲規(guī)格轉(zhuǎn)化為時域中的抖動規(guī)格。

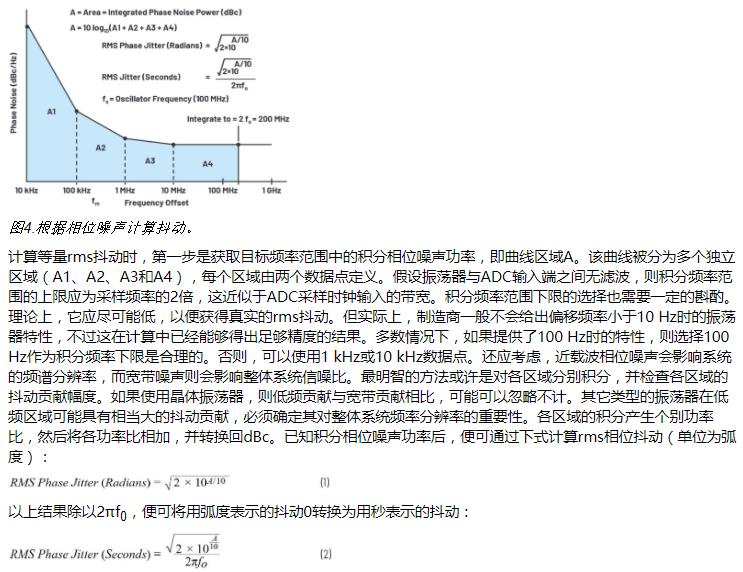

根據(jù)相位噪聲計算抖動

相位噪聲曲線有些類似于放大器的輸入電壓噪聲頻譜密度。與放大器電壓噪聲一樣,最好在振蕩器中使用1/f低轉(zhuǎn)折頻率。振蕩器通常用相位噪聲來描述性能,但為了將相位噪聲與ADC的性能關(guān)聯(lián)起來,必須將相位噪聲轉(zhuǎn)換為抖動。為將圖4中的圖與現(xiàn)代ADC應用關(guān)聯(lián)起來,選擇100 MHz的振蕩器頻率(采樣頻率)以便于討論,典型曲線如圖4所示。請注意,相位噪聲曲線由多條線段擬合而成,各線段的端點由數(shù)據(jù)點定義。

量化參考時鐘抖動

高性能DAQ系統(tǒng)中使用的參考時鐘源一般為晶體振蕩器,與其他時鐘源相比,它可以提供更出色的抖動性能。

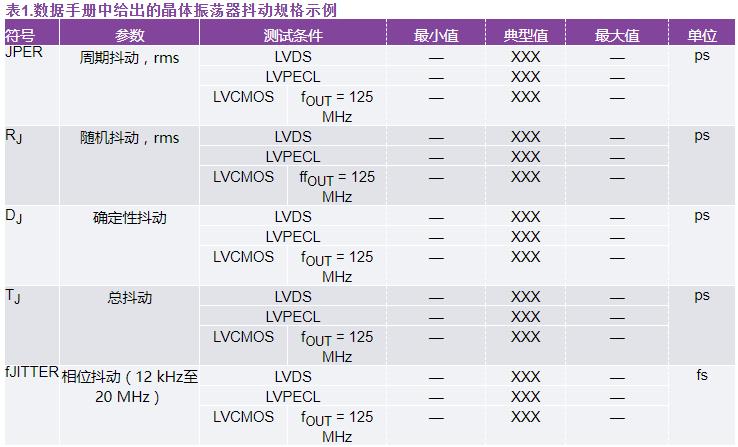

我們一般使用表1所示的示例在數(shù)據(jù)手冊中定義晶體振蕩器的抖動規(guī)格。在量化參考時鐘的抖動貢獻時,相位抖動是最重要的規(guī)格指標。相位抖動通常定義為邊沿位置相對于平均邊沿位置的偏差。

另一方面,有一些晶體振蕩器指定相位噪聲性能,而不是指定抖動。如果振蕩器數(shù)據(jù)手冊定義了相位噪聲性能,可以將噪聲值轉(zhuǎn)化為抖動,如“根據(jù)相位噪聲計算抖動”部分所述。

量化來自FPGA的抖動

FPGA中參考時鐘的主要作用是提供觸發(fā)信號,以啟動FPGA中設定的不同并行事件。換句話說,參考時鐘協(xié)調(diào)FPGA中的所有事件。為了提供更好的時間分辨率,參考時鐘通常被傳遞到FPGA中的PLL,以增大其頻率,因此,可能出現(xiàn)短時間隔事件。此外,需注意FPGA中包含一條觸發(fā)-執(zhí)行路徑,其中,參考時鐘被傳遞至時鐘緩沖器、計數(shù)器、邏輯門等。處理抖動敏感型重復事件(例如,通過隔離將LVDS轉(zhuǎn)化-開始信號提供給ADC)時,需要量化來自FPGA的抖動貢獻,以合理預估整體系統(tǒng)抖動對高速數(shù)據(jù)采集性能的影響。

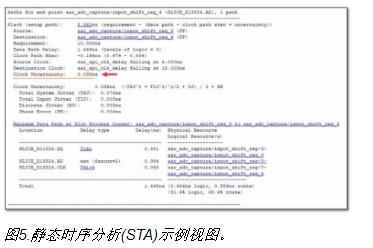

FPGA的抖動性能通常在FPGA數(shù)據(jù)手冊中給出。也會在大部分FPGA軟件工具的靜態(tài)時序分析(STA)中給出,如圖5所示。時序分析工具可以計算數(shù)據(jù)路徑源和目的地的時鐘不確定性,并將它們組合以獲得總時鐘不確定性。為了自動在STA中計算參考時鐘抖動量,必須在FPGA項目中將其添加為輸入抖動約束。

量化數(shù)字隔離產(chǎn)生的抖動

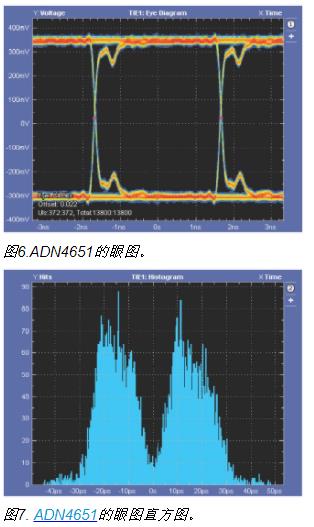

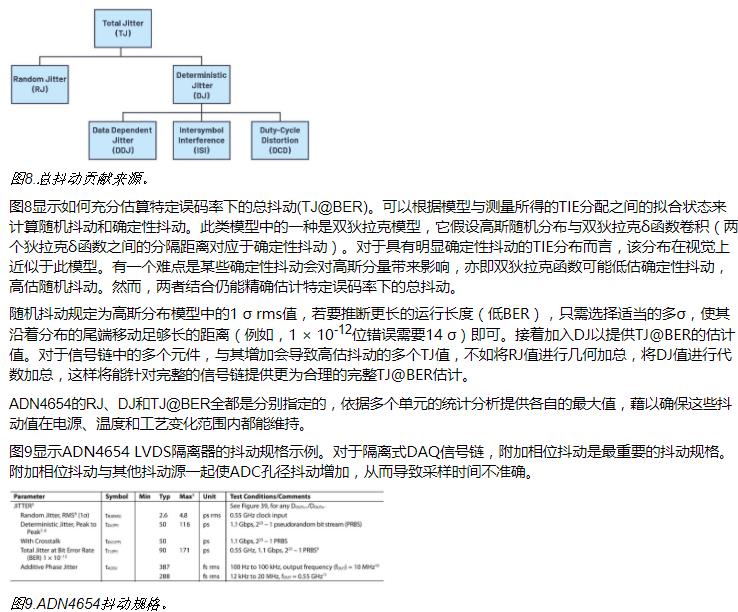

查看抖動的最基本方法是用差分探針去測量LVDS信號對,并且上升沿和下降沿上均要觸發(fā),示波器設定為無限持續(xù)。這意味著高至低和低至高的躍遷會相互迭加,因此可以測量交越點。交越寬度對應于峰峰值抖動或截至目前所測得的時間間隔誤差(TIE)。比較圖6和圖7所示的眼圖和直方圖。有一些抖動是隨機來源(例如熱噪聲)所導致,此隨機抖動(RJ)意味著示波器上所看到的峰峰值抖動會受到運行時間的限制(隨著運行時間增加,直方圖上的尾巴會升高)。

相比之下,確定性抖動(DJ)的來源是有界限的,例如脈沖偏斜所導致的抖動、數(shù)據(jù)相關(guān)抖動(DDJ)和符碼間干擾(ISI)。脈沖偏斜源于高至低與低至高傳輸延遲之間的差異。這可以通過偏移交越實現(xiàn)可視化,即在0 V時,兩個邊沿分開(很容易通過圖7中直方圖內(nèi)的分隔看出來)。DDJ源于不同工作頻率時的傳輸延遲差異,而ISI源于前一躍遷頻率對當前躍遷的影響(例如,邊沿時序在一連串的1s或0s與1010模式碼之后通常會有所不同)。

作者簡介

Lloben Paculanan是ADI菲律賓GT公司的產(chǎn)品應用工程師。他于2000年加入ADI公司,先后擔任多個測試硬件開發(fā)和應用工程職位;一直從事精密高速信號鏈μModule開發(fā)。他擁有美國澤維爾大學Ateneo de Cagayan學院工業(yè)工程技術(shù)學士學位,以及Enverga University的計算機工程學士學位。

John Neeko Garlitos是ADI公司的信號鏈μModule解決方案產(chǎn)品應用工程師。他從事信號鏈μModule開發(fā),以及適用于Circuits from the Lab和參考電路的嵌入式軟件工作。他于2017年開始在ADI菲律賓GT公司工作。他擁有菲律賓科技大學沙鄢分校電子工程理學士學位,以及菲律賓迪里曼大學電子工程碩士學位。