11年能發(fā)生什么?

網(wǎng)絡(luò)平臺從天涯論壇、百度貼吧變成微博、抖音;手機(jī)霸主從HTC、諾基亞變成蘋果、三星;大學(xué)新生三件套從床上三件套變成“蘋果三件套”。而這一系列變化的背后離不開芯片的發(fā)展。2011年,人們還在為芯片晶體管規(guī)模創(chuàng)新紀(jì)錄達(dá)39億個而歡呼,11年后,人們已經(jīng)被高達(dá)1140億個晶體管的芯片所震撼。

即使聽上去如同天方夜譚,但11年,已經(jīng)足夠讓這個高科技產(chǎn)業(yè)發(fā)生翻天覆地的變化。縱觀芯片發(fā)展歷史,“極限”兩字可以說是存在于每個時代,但無一例外都被一一突破。從22nm工藝節(jié)點(diǎn)推出3D晶體管之后,芯片產(chǎn)業(yè)仿佛打通了任督二脈,F(xiàn)lash、封裝、甚至NAND,都開始走向3D,芯片3D時代悄然已至。

邁出第一步的3D晶體管

晶體管是最早實現(xiàn)3D化的,畢竟按照摩爾定律,晶體管的數(shù)量與芯片性能息息相關(guān),在平面晶體管時代,22nm基本就是大家公認(rèn)的極限了,為了突破這個工藝極限,F(xiàn)inFET晶體管誕生了。

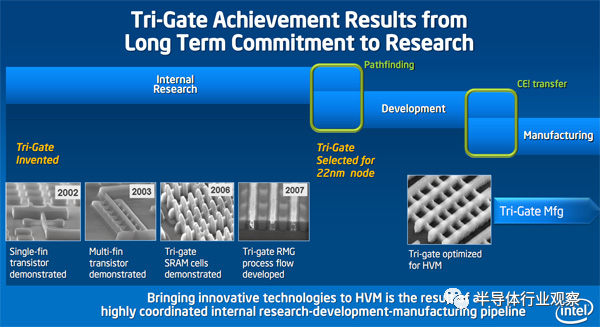

FinFET確切的說,是一個技術(shù)的代稱。世界上第一個3D三維晶體管是由英特爾在2011年5月宣布研制成功,當(dāng)時英特爾稱其為 “Tri-Gate”( 三柵極晶體管)。早在2002年,英特爾就已經(jīng)提出了相關(guān)技術(shù)專利,花了將近10年完善,并在2011年年底用Tri-Gate技術(shù)量產(chǎn)22nm工藝的新一代處理器lvy Bridge,于2012年初正式發(fā)布。雖然叫法不同,但Tri-Gate的本質(zhì)就是FinFET。

圖源:英特爾

FinFET 晶體管

FinFET晶體管又叫鰭式場效應(yīng)晶體管,由3D晶體管之父胡正明教授于1999年發(fā)明。相較于平面晶體管,F(xiàn)inFET運(yùn)用立體的結(jié)構(gòu),對柵極形狀進(jìn)行改制,閘門被設(shè)計成類似魚鰭的叉狀3D架構(gòu),位于電路的兩側(cè)控制電流的接通與斷開,大幅度提升了源極和柵極的接觸面積,減少柵極寬度的同時降低漏電率,讓晶體管空間利用率大大增加,讓電路更加穩(wěn)定,同時也達(dá)成了半導(dǎo)體制程持續(xù)微縮的目標(biāo)。

而胡正明教授在發(fā)明了FinFET晶體管之后,又投身產(chǎn)業(yè)界,2001~2004年期間擔(dān)任臺積電CTO。在其任職期間,臺積電于2002年制造出操作電壓僅0.7伏特的25納米晶體管,命名為“Omega FinFET”。

上述提到,英特爾是最先推出商業(yè)化FinFET的企業(yè),但由于其14nm推遲了整整兩個季度,因此被臺積電、三星、格芯等代工廠迎頭趕上。

三星方面,2013年1月,新思科技宣布采用三星的14LPE工藝成功實現(xiàn)了首款測試芯片的流片。2014年,三星還和格芯聯(lián)合宣布達(dá)成新的戰(zhàn)略合作,將共同為客戶提供14nm FinFET制造工藝。

臺積電則是在2012年10月16日的年度大會中,宣布制訂了20nm平面、16nmFinFET和2.5D發(fā)展藍(lán)圖,并表示將于2013年11月開始生產(chǎn)16納米FinFETs。在臺積電宣布前一個月,格芯已經(jīng)宣布在2014年開始提供23納米FinFET。

不過隨著芯片制程的不斷縮小,F(xiàn)inFET晶體管也遇到了發(fā)展瓶頸。臺積電首席科學(xué)家黃漢森曾表示,在16nm的制程中采用FinFET架構(gòu),每個晶體管可以有很多的鰭,但當(dāng)制程逐漸縮小的時候,鰭的數(shù)量也會隨之減少。因為不可能有0.5個鰭,所以當(dāng)制程越往下走、空間越來越小的時候,F(xiàn)inFET最特別的垂直設(shè)計將會碰上空間跟技術(shù)上的挑戰(zhàn)。

之前人們都認(rèn)為5nm將是FinFET的極限,但2020年臺積電打破了這個瓶頸,其在2020年第一季的法人說明會上,透露了3nm將繼續(xù)采取FinFET晶體管技術(shù)。而臺積電3nm也預(yù)計將于今年下半年出貨。不過,這個立體結(jié)構(gòu)的微縮也非無極限,3nm似乎真的已經(jīng)是極限了,從當(dāng)前的消息來看,臺積電到了2nm也將轉(zhuǎn)采其他的技術(shù),也就是下面要說到的GAA

GAA FET 晶體管

GAA全稱Gate-All-Around,是一種環(huán)繞式柵極晶體管技術(shù),被認(rèn)為是FinFET技術(shù)的升級版。與FinFET的不同之處在于,GAA通過使用納米片設(shè)備制造出了MBC FET(多橋通道場效應(yīng)管),其設(shè)計通道的四個面周圍有柵極,減少漏電壓并改善了對通道的控制,這是縮小工藝節(jié)點(diǎn)時的基本步驟。

由于GAAFET 晶體管只在先進(jìn)制程中有所采用,所以能參與其中的只有三星、臺積電、和英特爾三家巨頭。

三星自稱在2002 年就對GAA 保持關(guān)注并投入研究,并于2019年宣布,將在3nm制程世代,改采GAA技術(shù),作為FinFET之后的接班制程。根據(jù)三星的說法,與7nm制造工藝相比,3nm GAA技術(shù)的邏輯面積效率提高了45%以上,功耗降低了50%,性能提高了約35%。據(jù)悉,搭載此項技術(shù)的首批3nm三星芯片將于今年上半年實現(xiàn)量產(chǎn)。

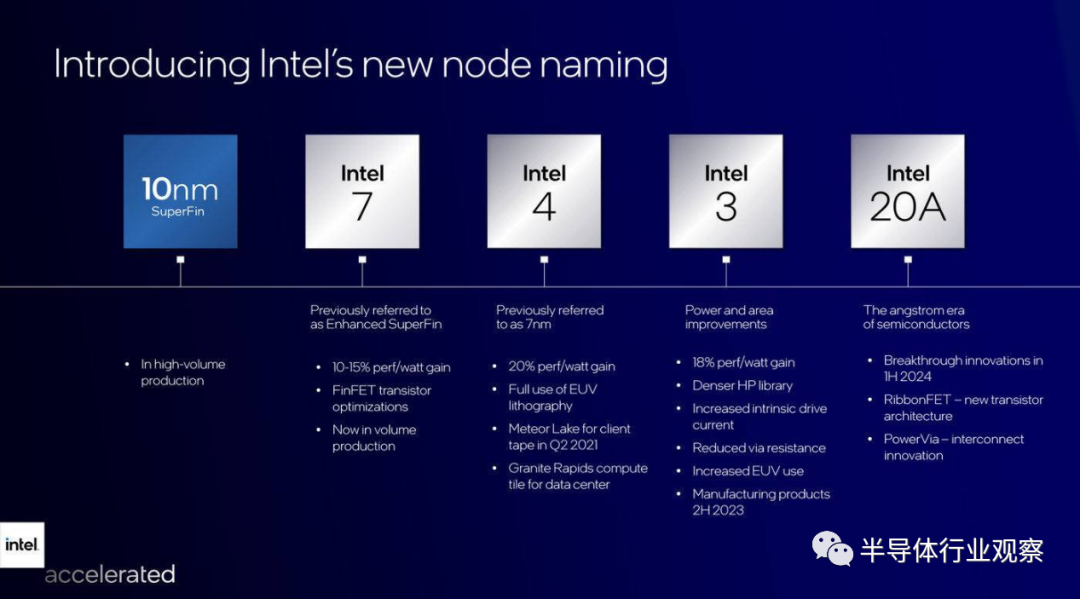

英特爾方面,2020年年初《Profesionalreview》曾報導(dǎo),英特爾在5納米節(jié)點(diǎn)上將會放棄FinFET電晶體,轉(zhuǎn)向GAA環(huán)繞柵極電晶體。不過從英特爾去年公布的未來五年的芯片制程工藝的技術(shù)路線圖來看,預(yù)計要在2024年的Intel 20A(相當(dāng)于我們說的2nm)制程上才會用到RibbonFET即英特爾的GAA技術(shù)。

圖源:英特爾

對于臺積電2nm制程將采用GAA晶體管好像已成產(chǎn)業(yè)內(nèi)默認(rèn)的事實,不過筆者搜尋資料發(fā)現(xiàn),臺積電官方關(guān)于2nm并未給出明確的說法,最初是在2020年7月,據(jù)臺灣經(jīng)濟(jì)日報報道,臺積電2nm技術(shù)研發(fā)有重大突破,已成功找到路徑,將切入GAA技術(shù)。而在日前2022年第一季度財報電話會議上,雖然臺積電總裁魏哲家透露2nm計劃2024年預(yù)生產(chǎn),2025年投產(chǎn),但當(dāng)分析師詢問“有關(guān)在 N2 上臺積電首次使用 GAA FET,逐漸取代 finFET”的問題,魏哲家也是避而不答。

不過臺積電(南京)有限公司總經(jīng)理羅鎮(zhèn)球曾在去年年底透露,臺積電研發(fā) Nanosheet / Nanowire 的晶體管結(jié)構(gòu)(類似 GAA)超過 15 年,已經(jīng)達(dá)到非常扎實的性能。

臺積電2nm是否真的采用GAA,或許只能交給時間來揭開這個謎底。

沖向200層的3D Flash

從時間上看,第一個3D晶體管和第一代3D NAND閃存芯片推出的時間相差無幾。2011年,英特爾推出世界上第一個3D三維晶體管,2012年三星推出第一代3D NAND閃存芯片,也是第一款32層 SLC V-NAND SSD——850 PRO。

閃存走向3D也是發(fā)展的必然趨勢,畢竟這些年,我們的網(wǎng)絡(luò)社交方式從文字到圖片再到視頻,數(shù)據(jù)量呈指數(shù)級增長,平面 NAND已達(dá)到其產(chǎn)能發(fā)展的極限,再發(fā)展下去只會影響其性能、耐用性和可靠性。為了能在有限的空間里存儲更多的數(shù)據(jù),也為了追求更高的存儲密度,閃存工業(yè)也開始向3D邁進(jìn)。

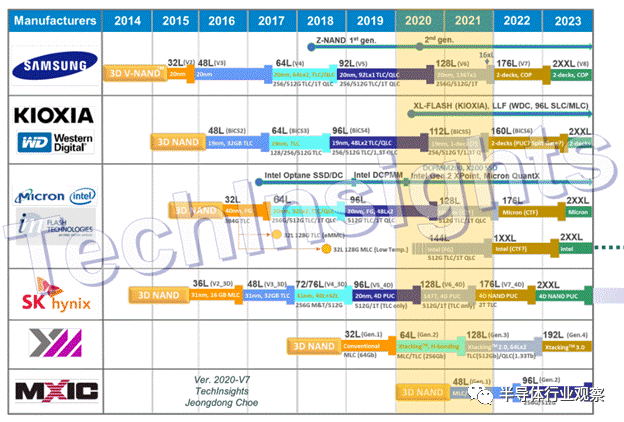

最開始是東芝在2008年開發(fā)了3D NAND結(jié)構(gòu)BICS,4年后,三星在2012年推出了第一代3D NAND閃存芯片,隨后,東芝、西部數(shù)據(jù)、美光等存儲大廠接連跟上,拉開了3D NAND 層數(shù)之戰(zhàn)的序幕。

2014-2023年的世界領(lǐng)先存儲公司的閃存路線圖圖源:TechInsights

對于3D NAND,層數(shù)越高,可具有的容量就越大,時至今日,3D NAND的層數(shù)廝殺已經(jīng)邁入200層。今年2月,有韓媒報道稱,三星電子將在今年底最晚明年上半年推出超過200層的第八代V NAND產(chǎn)品,采用雙堆棧技術(shù),預(yù)計率先推出224層NAND產(chǎn)品,與上一代176層NAND產(chǎn)品相比,第八代V NAND可以將生產(chǎn)力和數(shù)據(jù)傳輸速度提高了30%。有業(yè)內(nèi)人士表示,三星是目前業(yè)內(nèi)僅采用單堆棧技術(shù)實現(xiàn)128層NAND Flash的廠商,采用雙堆棧技術(shù)的200+層NAND產(chǎn)品也被認(rèn)為是超高技術(shù)領(lǐng)域,技術(shù)挑戰(zhàn)也十分嚴(yán)峻。

西部數(shù)據(jù)閃存業(yè)務(wù)部門負(fù)責(zé)人、執(zhí)行副總裁Robert Soderbery在5月投資者活動日中公布了其SSD產(chǎn)品路線圖,并預(yù)言3D NAND即將進(jìn)入200+層堆疊,西部數(shù)據(jù)稱其為BiCS+。據(jù)介紹,西部數(shù)據(jù)下一步要推出162層的BiCS6閃存,預(yù)計2022年底開始量產(chǎn)采用QLC和TLC配置的BiCS6 3D NAND,而176層的NAND也在制造中。此外,西部數(shù)據(jù)技術(shù)路線圖顯示將在2032年達(dá)到500+層堆疊。

圖源:西部數(shù)據(jù)

美光近日也發(fā)布了業(yè)界首個 232 層堆棧的 3D NAND Flash芯片,雖然暫時還沒有公布232層3D NAND閃存芯片的具體參數(shù),但可以知道采用的是CuA架構(gòu),初始容量為1Tb(128GB),并預(yù)計在 2022 年底左右開始量產(chǎn)。美光透露,其正在批量生產(chǎn)176層閃存芯片,而作為第五代3D NAND的此款芯片將在2022年之內(nèi)完成自己的歷史使命。此外,美光還就500層以上閃存制定發(fā)展路線圖,只是尚未披露具體時間表。

圖源:美光

相比之下,SK海力士近期在NAND層數(shù)上的新聞并不多,不過早在2020年,SK海力士就已經(jīng)宣布完成了業(yè)內(nèi)首款多堆棧176層4D閃存的研發(fā)。

我國方面,長江存儲于2018年研發(fā)了32層3D NAND芯片并在年底量產(chǎn),2019年量產(chǎn)了基于Xtacking架構(gòu)的64層256 Gb TLC 3D NAND閃存。2020年,長江存儲宣布,其128層QLC 3D閃存(X2-6070)研制成功。而在近期,有業(yè)內(nèi)人士透露,長江存儲最近已向一些客戶交付了其自主研發(fā)的192層3D NAND閃存的樣品,預(yù)計將在今年年底前正式推出產(chǎn)品。

對于3D NAND未來發(fā)展,SK 海力士曾預(yù)計 3D NAND 可以擴(kuò)展到多達(dá) 600 層,從這方面來看,相關(guān)制造工藝的線性推進(jìn)策略還能將持續(xù)數(shù)年。

火爆的3D封裝

3D封裝在前段時間也是狠狠火了一把,引爆點(diǎn)在于蘋果在3月9日凌晨推出的M1 Ultral芯片,就是筆者在開頭提到的那個擁有1140億個晶體管的芯片,而該芯片采用的就是臺積電的3D Wafer-on-Wafer封裝技術(shù)。

隨著芯片越來越復(fù)雜,芯片面積、良率和復(fù)雜工藝的矛盾難以調(diào)和,3D封裝是發(fā)展的必然趨勢。與傳統(tǒng)的封裝相比,3D封裝技術(shù)有望提供更高的芯片連接性和更低的功耗。一般來說,3D封裝就是將一顆原來需要一次性流片的大芯片,改為若干顆小面積的芯片,采用引線鍵合、倒裝芯片或二者混合的組裝工藝,也可采用硅通孔技術(shù)進(jìn)行互連,組裝成一顆大芯片,從而實現(xiàn)大芯片的功能和性能,而這種小面積的芯片就是Chiplet。

從當(dāng)前局勢來看,各大IDM廠、晶圓代工廠、封測廠等頭部企業(yè)都已積極布局3D封裝。

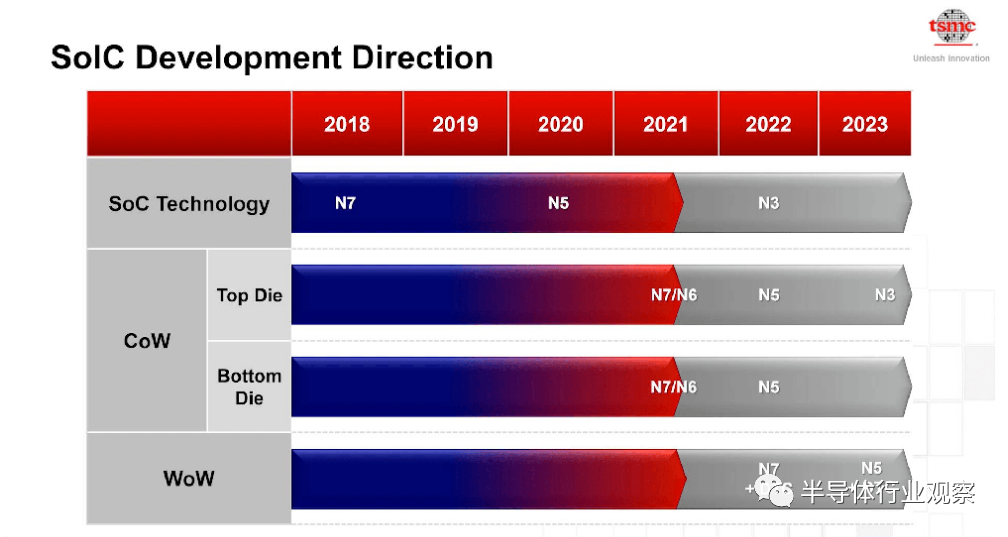

在晶圓代工廠領(lǐng)域,臺積電的3D封裝技術(shù)一馬當(dāng)先,早在2008年底臺積電就成立導(dǎo)線與封裝技術(shù)整合部門,正式進(jìn)軍封裝領(lǐng)域。據(jù)悉,臺積電的3D封裝工藝主要分為前端芯片堆疊SoIC技術(shù)和后端先進(jìn)封裝CoWoS和InFO技術(shù)。

2018年4月臺積電首度對外界公布創(chuàng)新的SoIC技術(shù)。作為一種多芯片堆棧技術(shù),SoIC可分為CoW(Chip on Wafer)和WoW(Wafer on Wafer)兩種鍵合方式。其中,WoW就是將兩層Die以鏡像方式垂直堆疊起來,上述蘋果M1 Ultral芯片以及今年年初Graphcore推出的IPU都采用的這種封裝技術(shù)。

在2021年Hot Chips上,臺積電公布了其SoIC研發(fā)進(jìn)度,在CoW方面正在開發(fā)N7-on-N7和N5-on-N5等;WoW方面,則在開發(fā)Logic-on-DTC,預(yù)計2022年CoW和WoW將會實現(xiàn)基于N5工藝。

圖片來源:臺積電

英特爾則是在2018年推出了3D堆疊封裝技術(shù)“Foveros”,第一代 Foveros于2019年在Lakefield芯片中推出。英特爾方面預(yù)計在2023 年消費(fèi)級處理器 Meteor Lake上使用其第二代 Foveros 技術(shù),實現(xiàn) 36 微米的凸點(diǎn)間距,與第一代相比,連接密度有效地增加了一倍。除了第二代Foveros 技術(shù)外,英特爾預(yù)測第三代Foveros Omni以及第四代Foveros Direc都將在2023年量產(chǎn)。

圖片來源:英特爾

三星在2020年8月公布了自家的3D封裝技術(shù)“X-Cube”。據(jù)了解,X-Cube是一種利用垂直電氣連接而不是電線的封裝解決方案,三星在 7nm制程的測試過程中,成功利用 TSV 技術(shù)將SRAM 堆疊在邏輯芯片頂部,從而釋放了空間以將更多的內(nèi)存封裝到更小的占位空間中。三星表示,這項技術(shù)將用于 5G、AI、AR、HPC(高性能計算)、移動和 VR 等領(lǐng)域。

中國大陸封測廠在3D封裝技術(shù)領(lǐng)域也是頻頻發(fā)力。比如長電科技在五年7月推出了面向3D封裝的XDFOI全系列極高密度扇出型封裝解決方案,該技術(shù)所運(yùn)用的極窄節(jié)距凸塊互聯(lián)技術(shù)能夠?qū)崿F(xiàn)44mm×44mm的封裝尺寸,預(yù)計于2022年下半年完成產(chǎn)品驗證并實現(xiàn)量產(chǎn)。而通富微電南通通富工廠則是在去年8月搬入2.5D/3D生產(chǎn)線首臺設(shè)備——化學(xué)機(jī)械拋光設(shè)備(CMP),標(biāo)志著該生產(chǎn)線全面進(jìn)入設(shè)備安裝調(diào)試和工程驗證階段。

此外,華為最近也有一項芯片堆疊封裝專利曝光,在日前的分析師大會上,華為常務(wù)董事、ICT基礎(chǔ)設(shè)施業(yè)務(wù)管理委員會主任汪濤指出,華為正嘗試用堆疊芯片的相關(guān)技術(shù),用不那么先進(jìn)的芯片工藝也可以讓華為的產(chǎn)品更有競爭力。

指日可待的3D DRAM

雖然與3D NAND同屬于存儲領(lǐng)域,但DRAM更多得是比拼工藝節(jié)點(diǎn),制造工藝從 1x nm 緩慢推進(jìn)到 1y、1z、1-alpha 和 1-beta,為此像三星、SK海力士和美光這三大DRAM廠商都已經(jīng)擁抱了EUV技術(shù),相比之下,3D進(jìn)程就慢了很多,至今未有產(chǎn)品面市。

目前DRAM制造商仍在通過降低技術(shù)生產(chǎn)標(biāo)準(zhǔn)來提高存儲單元的密度,并且通過向 EUV 掃描儀的過渡可以繼續(xù)維持一段時間的平面技術(shù),但這種資源也將很快耗盡,而對內(nèi)存的需求卻仍在攀升。由此來看,單元垂直排列,增加DRAM 體積才是未來趨勢。

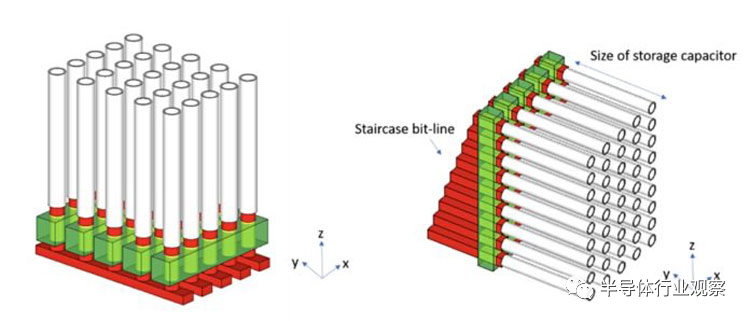

左邊是傳統(tǒng)的平面DRAM陣列,右邊是垂直排列的單元(灰色長管是電容器)。圖片來源:Monolithic3D

瑞銀投資銀行全球研究部也指出,對于DRAM,使用EUV只能應(yīng)對部分挑戰(zhàn),無法解決所有難題。采用3D DRAM是更有希望的解決方案,能縮小DRAM存儲元件尺寸,從而提高密度。為此,瑞銀投資銀行全球研究部預(yù)計 3D DRAM最早可能于2027年開始初期生產(chǎn)到2028到29年開始實質(zhì)性量產(chǎn)。

目前,幾家存儲大廠也開始逐漸向3D DRAM邁進(jìn)。今年年初,BusinessKorea 報道稱,三星電子正在加速 3D DRAM 的研發(fā),已經(jīng)開始加強(qiáng)招聘人員等相關(guān)團(tuán)隊建設(shè)。

此外,美光科技和 SK 海力士也在考慮開發(fā)3D DRAM。美光提交了與三星電子不同的 3D DRAM 專利申請,希望能在不放置單元的情況下改變晶體管和電容器的形狀。也有日本媒體報道稱,華為將在6月份舉行的 VLSI Symposium 2022上發(fā)表其與中科院微電子研究所合作開發(fā)的 3D DRAM 技術(shù)。Applied Materials和Lam Research等全球半導(dǎo)體設(shè)備制造商也在開發(fā)與3D DRAM相關(guān)的解決方案。

不過,由于開發(fā)新材料的困難和物理限制,3D DRAM 的商業(yè)化還需要一些時間,業(yè)內(nèi)人士預(yù)測,3D DRAM 將在 2025 年左右開始問世,雖然與瑞銀投資銀行全球研究部預(yù)計的時間有所出入,但不難看出,未來DRAM或許也將迎來3D DRAM的天下。

寫在最后

每個時代有每個時代發(fā)展的瓶頸,但同時也有他們的破解之道。在芯片3D化過程中出現(xiàn)了很多新技術(shù),這些新技術(shù)在打破平面技術(shù)發(fā)展極限的同時,也創(chuàng)造出新的難題、新的挑戰(zhàn),未來芯片競爭只會越來越激烈。但“芯片有夢,技無止境”。