摘要

CMOS 圖像傳感器的發(fā)展及其使用先進成像技術的前景有希望改善生活質(zhì)量。隨著并行模數(shù)轉(zhuǎn)換器 (ADC) 和背照式 (BI) 技術的迅速出現(xiàn),CMOS 圖像傳感器目前在數(shù)碼相機市場占據(jù)主導地位,而堆疊式 CMOS 圖像傳感器繼續(xù)在移動設備中提供增強的功能和用戶體驗。本文回顧了堆疊圖像傳感器在圖像傳感器架構(gòu)演進方面的最新成果,以加速性能改進、擴大傳感能力以及將邊緣計算與各種堆疊器件技術結(jié)合。

I. 引言

圖像傳感器目前用于多種應用。自 1969 年電荷耦合器件 (CCD) 發(fā)明以來,固態(tài)圖像傳感器已蔓延到各種消費市場,例如小型攝像機和數(shù)碼相機。自 2005年以來已成為主流固態(tài)圖像傳感器的 CMOS 圖像傳感器在為 CCD 開發(fā)的技術的基礎上不斷發(fā)展。除了目前最大的圖像傳感器市場智能手機之外,對圖像傳感器的需求正迅速擴大到用于安全的網(wǎng)絡攝像頭、用于工廠自動化的機器視覺以及用于輔助駕駛和自動駕駛系統(tǒng)的汽車攝像頭。

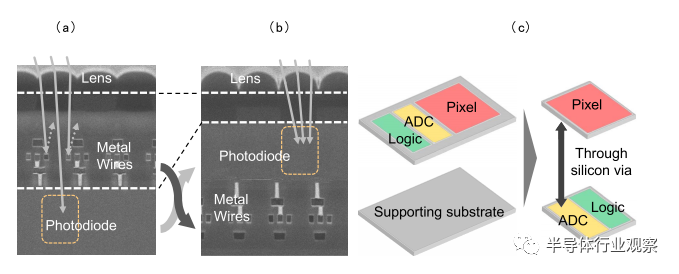

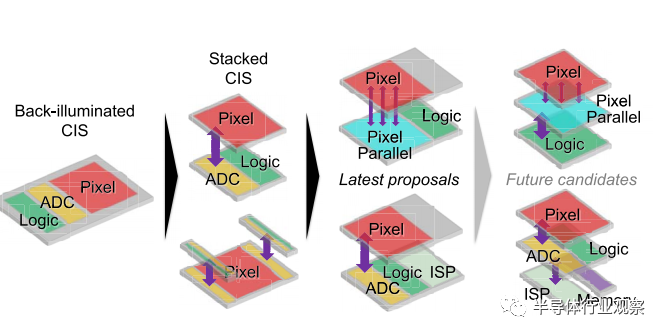

CMOS圖像傳感器技術的一個主要轉(zhuǎn)折點是背照式(BI)圖像傳感器的成功開發(fā),這使得圖像傳感器的堆疊結(jié)構(gòu)的發(fā)展成為可能,如圖1所示。在最初的前照式 (FI) 結(jié)構(gòu)中,很難減小傳感器的像素尺寸,因為入射光必須由光電二極管通過金屬線包圍的間隙收集。由于背照式(BI)結(jié)構(gòu)大大提高了靈敏度并允許金屬布線的靈活性,而且由于晶圓鍵合和極其均勻的晶圓減薄技術,它已成為圖像傳感器的熱門產(chǎn)品。圖像傳感器逐漸向堆疊結(jié)構(gòu)發(fā)展,其中邏輯電路直接集成在基底晶片上。堆疊工藝允許更先進的CMOS工藝中高度并行的模數(shù)轉(zhuǎn)換器 (ADC) 和信號處理元件的更高集成度,獨立于為像素光電二極管定制的傳感器工藝。堆疊設備結(jié)構(gòu)繼續(xù)極大地改變圖像傳感器架構(gòu)。

圖 1. CMOS 圖像傳感器的結(jié)構(gòu)。(a) FI 結(jié)構(gòu),(b) BI 結(jié)構(gòu),和(c)具有通孔的堆疊結(jié)構(gòu)。

本文回顧了具有堆疊設備的圖像傳感器架構(gòu)的發(fā)展趨勢,以顯著加速性能改進、擴展傳感能力以及集成連接到傳感器層的邊緣計算功能。第二部分介紹了堆疊設備配置的不同傳感器架構(gòu),這些架構(gòu)通過高度并行的列并行 ADC 實現(xiàn)高像素分辨率和高幀率成像。第三部分介紹了一些使用像素間距 Cu-Cu 連接(pixel-pitch Cu–Cu connections)實現(xiàn)的高級像素電路,這些電路對于在實際像素分辨率下實現(xiàn)更好的像素性能至關重要。像素間距 Cu-Cu 連接也使傳感器架構(gòu)逐漸向像素并行數(shù)字化方向發(fā)展。第四部分介紹了擴展傳感能力的傳感器架構(gòu)的一些進展,例如空間深度、時間對比傳感和不可見光成像。第五部分介紹了集成邊緣人工智能 (AI) 加速器的視覺傳感器。最后,第六部分給出了一些結(jié)論。

II.使用超過百萬像素的電影錄制

電影錄制需要至少每秒 30 或 60 幀 (fps) 的幀速率,即使像素數(shù)量正在從 200 萬像素高清 (HD) 格式增加到 800 萬像素 4K 格式。此外,更高的幀速率操作,例如 120、240 或 1000 每秒傳輸幀數(shù)(fps),可以提供慢動作回放。自 1997 年提出列并行 ADC 架構(gòu)以來,通過增加并行 ADC 的數(shù)量和加快 ADC 操作本身的速度,幀速率得到了改善 。由于可以將最佳工藝技術應用于傳感器像素和外圍設備,堆疊結(jié)構(gòu)有助于充分提高幀速率。傳感器制造需要幾種離子注入工藝來形成具有低結(jié)泄漏的光電二極管和晶體管。然而,邏輯工藝(the logic process)需要低電阻和高速晶體管。對于像素來說,三層或四層布線通常就足夠了,但邏輯電路大約需要十層布線。所使用的堆疊技術可以緩解同一芯片上非堆疊圖像傳感器的沖突約束,包括傳感器像素和邏輯電路。

A. 雙列 ADC 架構(gòu)

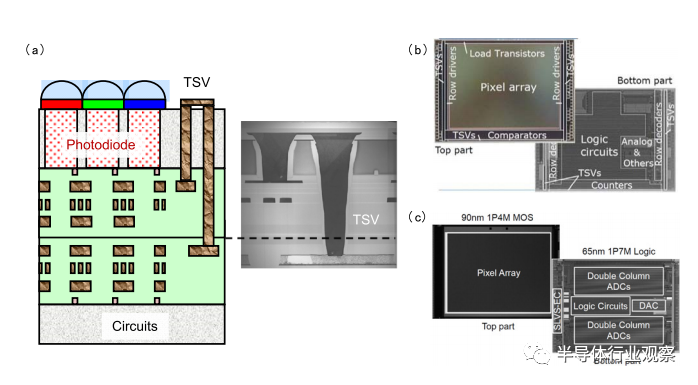

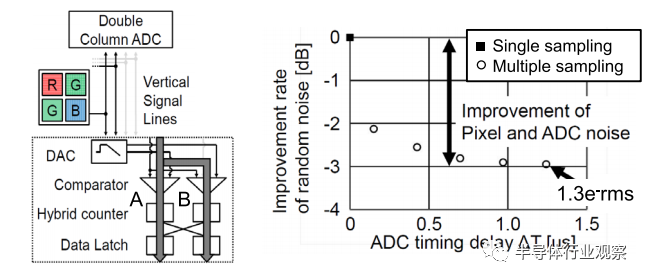

目前,大多數(shù) CMOS 圖像傳感器包括一個像素陣列、數(shù)千個以列并行結(jié)構(gòu)組織的 ADC 和邏輯電路。如圖 2(a) 所示,位于像素陣列外部的硅通孔 (TSV) 以高度并行的方式將像素列連接到 ADC。在 2013 年推出的第一個堆疊 CMOS 圖像傳感器 中,列 ADC 的模擬和數(shù)字部分分別被分成頂部和底部芯片,如圖 2(b) 所示。2015 年,提出了雙列 ADC 架構(gòu),并在 16M 像素下實現(xiàn)了 120 fps 的幀速率,其中列 ADC 完全移至底部芯片,如圖 2(c) 所示。傳感器芯片采用用于光電二極管的 90 納米傳感器定制工藝制造,僅使用 NMOS 邏輯。而邏輯芯片采用 65 納米標準 CMOS 工藝制造。由于列 ADC 可以獨立于傳感器芯片來實現(xiàn),因此 ADC 可以高度集成。除了提高幀速率外,還將冗余并行 ADC用在通過平均多個模數(shù) (AD) 轉(zhuǎn)換來降低噪聲,如圖 3 所示。一個像素的輸出同時分配給兩個 ADC,兩個數(shù)字輸出相加以再現(xiàn)圖像幀。兩個 ADC 的時序相位略有不同,以通過降低其噪聲信號之間的相關性來實現(xiàn)降噪。

圖 2. 堆疊 CMOS 圖像傳感器的實現(xiàn)。(a) 光電二極管和邏輯電路之間的 TSV 連接。(b) 首個堆疊的 CMOS 圖像傳感器。(c) 雙列 ADC 架構(gòu)。

圖 3. 雙列 ADC 架構(gòu)的簡化框圖(左)和噪聲特性的改進(右)。

B. 具有動態(tài)隨機存取存儲器 (DRAM) 的三層堆疊 CMOS 圖像傳感器

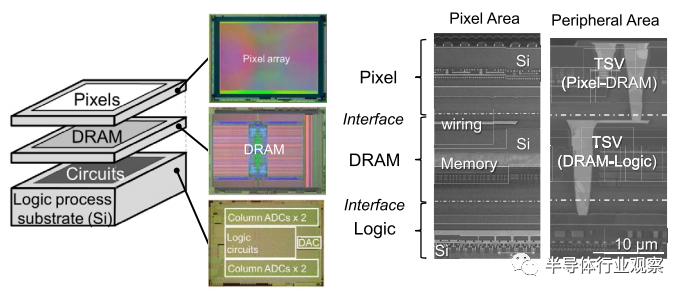

隨著像素和并行 ADC 數(shù)量的增加,圖像傳感器會輸出大量數(shù)據(jù)。2017 年,提出了一種三層堆疊的 CMOS 圖像傳感器以記錄 960 fps 的慢動作視頻,如圖 4 所示;三層之間通過硅通孔(TSV)連接,從并行 ADC 獲得的數(shù)據(jù)緩存在第二層 DRAM 中,以實現(xiàn)慢動作捕捉。對于超慢動作錄制,當來自 ADC 的數(shù)字數(shù)據(jù)通過 102-Gbit/s 總線臨時緩沖在 DRAM 中時,該傳感器可以在全高清分辨率下以 960 fps 的速度運行。當傳感器在 30 fps 的電影拍攝過程中檢測到用戶的觸發(fā)或場景中的快速運動時,讀出速度將變?yōu)?960 fps。在 DRAM 中一次最多可以存儲 63 幀全高清分辨率,并在隨后的電影捕捉過程中輸出緩沖數(shù)據(jù)。

圖 4. 帶有 DRAM 的三層堆疊 CMOS 圖像傳感器。

C. 用于Large Optical Format芯片堆疊于晶圓之上(Chip-on-Wafer)技術

迄今為止推出的堆疊式 CMOS 圖像傳感器是在晶圓上晶圓 (WoW) 鍵合工藝中制造的。然而,由于傳感器和邏輯芯片的尺寸必須相同,這種工藝并不總是最佳的選擇,特別是對于大光學格式(a large optical format),另一種堆疊方法涉及 CoW 鍵合,如圖 5 所示。當尺寸與光學格式(optical format)相同的邏輯芯片完全充滿高度并行的 ADC 和數(shù)字構(gòu)建塊(digital building blocks)時,面積效率在 WoW 鍵合中是最佳的。然而,如果邏輯電路小于光學格式(optical format),則 CoW 配置有最佳的面積效率,而 WoW 配置存在成本問題。

圖 5. 大型光學格式圖像傳感器的 WoW 和 CoW 鍵合工藝的面積效率。

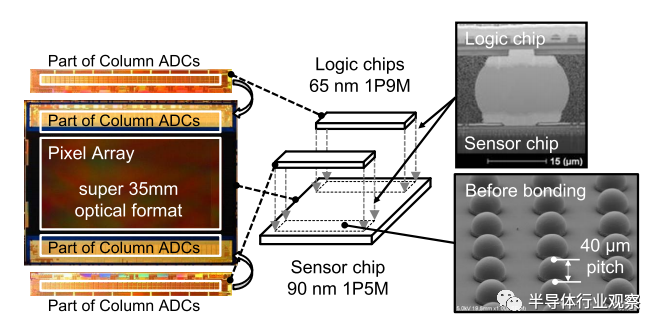

2016 年報道了一種使用 CoW 鍵合工藝的堆疊 CMOS 圖像傳感器 [12],實現(xiàn)了具有超 35 毫米光學格式(optical format)的廣播攝像機的全局快門圖像傳感器。在這里,兩個切開的邏輯芯片采用 65-nm CMOS 工藝設計,具有并行 ADC 和微凸塊(microbumps),并堆疊在為全局快門像素定制設計的大型傳感器芯片上,如圖 6 所示。具有高縱橫比的切開的邏輯芯片通過間距為 40 μm 的微凸塊連接到傳感器。因此,連接總數(shù)約為 38 000。該傳感器還允許通過 800 萬像素以 480 fps 的速度進行超慢動作回放。

圖 6. 使用 CoW 鍵合工藝的堆疊式 CMOS 圖像傳感器。

圖 7 顯示了大型光學格式圖像(large optical-format)傳感器的性能趨勢, 2021 年,全 35 毫米格式(full-35-mm-format)圖像傳感器具有 5000 萬像素和 250 fps。為了增加并行 ADC 的數(shù)量并逐步增加靜態(tài)隨機存取存儲器 (SRAM) 幀緩沖區(qū),使用 WoW 工藝來實現(xiàn)高性能。另一方面,CoW 工藝用來平衡成本效率和大型光學格式(large optical-format)傳感器的性能。2021 年還推出了 3.6 英寸圖像傳感器,具有 1.27 億像素和四個使用 CoW 工藝堆疊的邏輯芯片。CoW 工藝的下一個挑戰(zhàn)是提高晶片上芯片放置的吞吐量,以提高生產(chǎn)率。

圖 7. 大型光學格式圖像傳感器的性能趨勢。

III.像素并行架構(gòu)

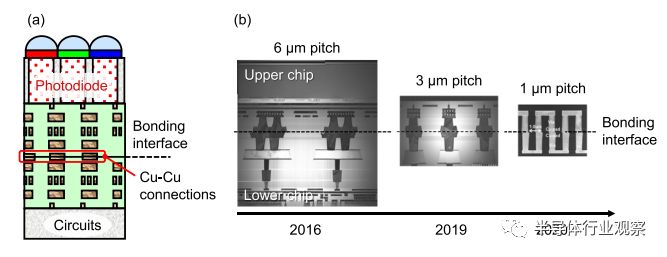

在上一節(jié)中,使用堆疊器件的傳感器架構(gòu)主要用于提高基于列并行 ADC 架構(gòu)的幀速率。本節(jié)介紹了基于使用細間距 Cu-Cu 連接(fine-pitch Cu–Cu connections)的像素并行架構(gòu)的一些進展。在這里,傳感器和邏輯層之間的連接已從 TSV 更改為混合鍵合的 Cu-Cu 連接,如圖 8(a) 所示。在 TSV 配置中,信號線被傳送到像素陣列外圍的邏輯層。相比之下,Cu-Cu 連接可以直接集成在像素下方,并且這些連接允許增加連接的數(shù)量。關于 Cu-Cu 連接間距的最新趨勢如圖 8(b)所示。圖像傳感器的混合鍵合過程中需要數(shù)百萬個沒有連接缺陷的 Cu-Cu 連接,而隨著大量觸點的穩(wěn)定連接,觸點間距逐漸減小;此外,最近報道了 1-μm Cu-Cu 混合鍵合間距。這些細間距連接將使像素并行電路架構(gòu)能夠以實際的像素尺寸制造。

圖 8.Cu-Cu 連接間距趨勢 (a) 簡化的器件結(jié)構(gòu)和 (b) 橫截面。

A. 堆疊像素電路擴展

文獻中已經(jīng)提出了許多技術和實現(xiàn)方式,通過像素電路擴展來提高像素性能,例如滿阱容量 (FWC) ,并實現(xiàn)附加功能,例如全局快門。圖 9(a) 和 (b) 分別顯示了單轉(zhuǎn)換增益和雙轉(zhuǎn)換增益的像素配置。較小的電容 CFD 會經(jīng)歷來自光電子的高電壓擺幅,以實現(xiàn)低噪聲讀出,但它很容易被大量信號電子飽和。然而,具有雙轉(zhuǎn)換增益的像素通過兩個轉(zhuǎn)換增益之間的順序操作切換,可以在 CFD 上實現(xiàn)低噪聲讀數(shù),在 CDCG 上實現(xiàn)高動態(tài)范圍 (HDR) 讀數(shù);此外,附加晶體管和電容器的面積開銷通過限制像素尺寸可以減小的量限制實現(xiàn)高像素分辨率。2018年,提出了具有雙轉(zhuǎn)換增益的堆疊像素電路擴展;通過像素平行的Cu-Cu連接在底部芯片上實現(xiàn)了額外的電路,如圖9(c)所示。通過在 20 和 200 μV/e- 的轉(zhuǎn)換增益之間切換,成功顯示了 1.5-?m 像素具有 83.8 dB 的動態(tài)范圍和 0.8 e-rms 的低噪聲。如圖 10 所示,像素級堆疊電路配置已應用于電壓域全局快門功能和具有雙轉(zhuǎn)換增益的像素。2019 年展示了快門效率超過 100 dB 的 2.2 μm 全局快門像素。具有雙轉(zhuǎn)換增益和電壓域全局快門的最先進像素分別實現(xiàn)了0.8μm和2.3 μm的像素尺寸,沒有像素級堆疊電路擴展;然而,堆疊像素配置仍有望為增強較小像素的像素性能。

圖 9. 像素電路配置 (a) 具有單轉(zhuǎn)換增益,(b) 具有雙轉(zhuǎn)換增益,以及 (c) 具有雙轉(zhuǎn)換增益并堆疊像素平行 Cu-Cu 連接。

圖 10. 通過像素平行 Cu-Cu 連接堆疊的電壓域全局快門的像素電路配置。

B. 像素并行 ADC

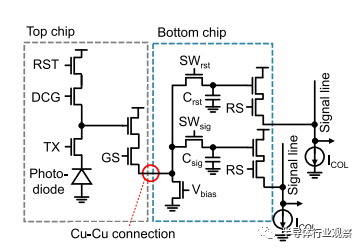

自 2001 年提出像素并行數(shù)字化概念以來,也提出了具有混合鍵合工藝的像素平行 Cu-Cu 連接的堆疊圖像傳感器。復雜電路中的像素內(nèi)區(qū)域開銷(within-pixel area overheads)絕對限制了像素分辨率,但 2017 年提出了具有陣列并行 ADC 架構(gòu)的 410 萬像素堆疊圖像傳感器,接著2018年提出了具有 146 萬像素并行ADC的堆疊圖像傳感器 。由于混合鍵合工藝的細間距 Cu-Cu 連接,像素并行 ADC 架構(gòu)已經(jīng)實現(xiàn)了 Mpixel 分辨率。如圖 11 所示,單斜率 ADC 用于像素并行和傳統(tǒng)列并行架構(gòu),但沒有源跟隨器電路。像素內(nèi)晶體管放大器直接集成在比較器中,通過兩個 Cu-Cu 連接將每個像素連接到底部芯片。由于計數(shù)器的面積限制,格雷碼被分配到像素內(nèi)(in-pixel)的鎖存器,數(shù)字讀出管道(digital readout pipelines)已經(jīng)使用像素陣列下的 ADC 實現(xiàn)。

圖 11. 像素并行 ADC 的電路配置。

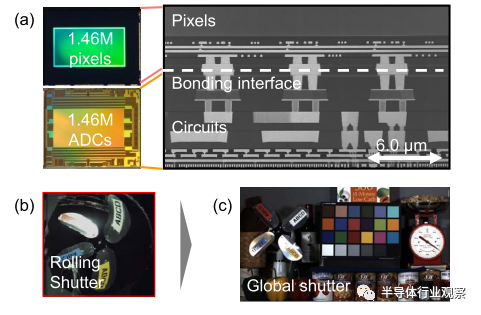

圖12(a)顯示了具有像素并行ADC架構(gòu)的原型芯片;盡管每個 ADC 僅以 6.9 μm 的像素間距實現(xiàn),其中比較器的靜態(tài)電流限制為 7.74 nA,但由于有效的帶寬控制,本底噪聲被抑制到 8.77 e-rms。所有像素并行 ADC 同時作為全局快門運行;因此,如圖 12(c) 所示,在使用原型捕獲的圖像中沒有觀察到如圖 12(b) 所示的滾動快門焦平面失真。仍在繼續(xù)開發(fā)像素并行 ADC 架構(gòu)。2020 年的最新的一項工作顯示像素間距為 4.6 μm,動態(tài)范圍為 127-dB,噪聲為 4.2e-rms,一項工作像素間距為 4.95 μm,噪聲為 2.6e-rms。

圖 12. 像素并行 ADC 的芯片實現(xiàn)。(a) 芯片顯微照片。(b) 使用滾動快門操作和 (c) 使用全局快門操作捕獲的圖像。

C. 像素平行光子計數(shù)器

光子計數(shù)成像,也稱為量子成像,是一種實現(xiàn)具有無噪聲讀出和 高動態(tài)范圍成像(HDR) 的圖像捕獲的有前途的技術。使用單光子雪崩二極管 (SPAD) 的光子計數(shù)圖像傳感器是通過堆疊技術實現(xiàn)像素并行數(shù)字化的挑戰(zhàn)之一。雪崩電流由單個光電子觸發(fā),在沒有來自模擬前端電路的任何噪聲的情況下,該事件可以數(shù)字化地視為光子計數(shù)。這需要為每個 SPAD 實現(xiàn)復雜的電路;而具有像素連接的堆疊器件結(jié)構(gòu)具有高度集成的光子計數(shù)成像的潛力。

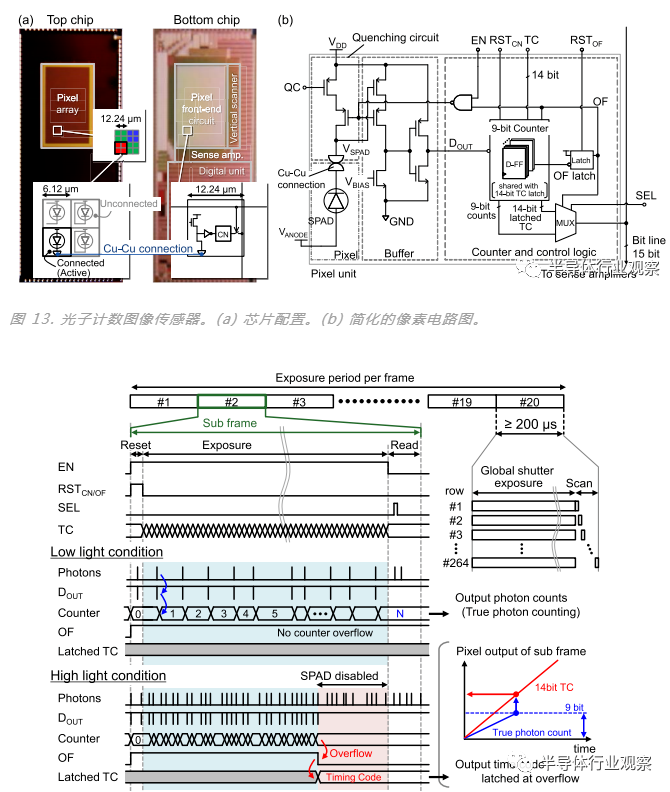

2021 年報道了一種動態(tài)范圍為 124 dB 并使用子幀外推架構(gòu)(subframe extrapolating architecture)的 SPAD 光子計數(shù)圖像傳感器 。一個背照式( BI) 單光子雪崩二極管(SPAD )像素陣列堆疊在底部芯片上,讀出電路通過像素平行的 Cu-Cu 連接,如圖 13(a) 所示。圖13(b)是像素單元的簡圖。每個像素都有一個 9-b 數(shù)字紋波計數(shù)器 (CN),用于計算入射光子的數(shù)量。來自計數(shù)器的溢出進位 (OF) 返回到淬滅電路以控制 SPAD 激活并鎖存時序代碼 (TC)。然后將 14-b時序代碼 (TC) 分配給所有像素,并在 OF 標志發(fā)生變化時覆蓋計數(shù)器,如圖 14 的時序圖所示。讀出光子的 9-b 計數(shù)或鎖存的 14-b TC,并且在弱光條件下準確獲得所有光子計數(shù),而不會出現(xiàn)計數(shù)器溢出。但是,當計數(shù)器在高光條件下溢出時,溢出像素會記錄時間,并外推整個曝光期間的實際入射光子數(shù)。

圖 14. 光子計數(shù)與子幀外推的時序圖。

如圖 15(a) 所示,已經(jīng)證明了 124 dB 的動態(tài)范圍,信噪比 (SNR) 沒有任何下降。在高光條件下計數(shù)器溢出后的 SNR 在擴展的動態(tài)范圍內(nèi)保持在 40 dB,因為真正的光子計數(shù)操作可以計數(shù)多達 10 240 個光子,即 9 位 × 20 子幀。圖 15(b) 顯示了以 250 fps 拍攝的 HDR 圖像;由于全局快門和 20 子幀 HDR 操作,即使使用 225 rpm 的旋轉(zhuǎn)風扇,也沒有觀察到運動偽影。20 子幀外推有效地抑制了運動偽影,如圖 15(c) 所示。SPAD 需要大約 20 V 的高偏置電壓以及低電源電壓下的像素并行觸發(fā)檢測器。由于不同電源電壓之間的器件隔離,通常難以實現(xiàn)具有小間距的 SPAD 像素。然而,堆疊器件結(jié)構(gòu)有效地分離了 SPAD 和 CMOS 邏輯層,從而加速了具有 SPAD 和擴展功能的小像素配置的開發(fā)。

圖 15. 光子計數(shù)的測量結(jié)果。(a) 動態(tài)范圍和信噪比。(b) 捕獲的 HDR 圖像。(c) 具有運動偽影抑制的捕獲圖像。

IV.傳感能力的擴展

除了之前介紹的動態(tài)范圍和全局快門功能之外,堆疊設備技術不僅增強了傳感器架構(gòu)的圖像質(zhì)量,還增強了傳感功能,例如空間深度、時間對比傳感和不可見光成像。

A. 空間深度

如第 III-C 節(jié)所述,具有 Cu-Cu 混合鍵合的堆疊器件結(jié)構(gòu)是實用 SPAD 技術在廣泛應用中的一種有前景的方法,并將 SPAD 像素間距減小到小于 10 ?m。為了提高光子檢測效率 (PDE) 并減少小像素間距的光學串擾,2020 年報道了一種包含全溝槽隔離 (FTI) 和 Cu-Cu 鍵合的 BI SPAD 像素陣列 。如圖 16 所示,在 BI 堆疊 SPAD 結(jié)構(gòu)中,SPAD 像素陣列對入射光完全開放,所有像素晶體管都在底部芯片上實現(xiàn)。金屬埋入式 FTI 有助于抑制與相鄰像素的串擾。10-?m 間距 SPAD 像素具有 7-?m 厚的硅層,以提高近紅外 (NIR) 光譜測量的靈敏度,并在 850 nm 和 940 nm 處分別實現(xiàn)了31.4% 和 14.2%以上的高 PDE。

圖 16. SPAD 器件結(jié)構(gòu)。(a) FI SPAD。(b) BI-stacked SPAD。

據(jù)報道,2021 年,一種使用了 BI 堆疊 SPAD, 189 × 600 SPAD 直接飛行時間 (ToF) 傳感器 用于汽車 LiDAR 系統(tǒng)。所有的像素前端電路都在SPAD陣列下的底層芯片中實現(xiàn),如圖17所示。在 LiDAR 系統(tǒng)中,當接收到反射的激光脈沖時,SPAD 會在 6 ns 的死區(qū)時間內(nèi)產(chǎn)生一個觸發(fā)脈沖,并將其傳送到時間數(shù)字轉(zhuǎn)換器 (TDC)。頂部和底部芯片分別使用具有 10 個銅層的 90-nm SPAD 和 40-nm CMOS 工藝。由于采用堆疊結(jié)構(gòu),傳感器包括重合檢測電路、TDC 和數(shù)字信號處理器 (DSP) 作為深度感測的構(gòu)建模塊。直接 ToF 傳感器在高達 200 m 的擴展范圍內(nèi)表現(xiàn)出 30 cm 的距離精度,使其能夠在 117k 勒克斯的陽光條件下檢測具有 95% 反射率的物體。

圖 17. 帶有直接 ToF 深度傳感器的 BI 堆疊 SPAD。

BI堆疊SPAD結(jié)構(gòu)是基于SPAD的成像和深度傳感的突破,具有改進的特性。與將電路放置在每個 SPAD 旁邊的傳統(tǒng)像素相比,BI 堆疊結(jié)構(gòu)提高了量子效率,并將 SPAD 和電路分成最佳硅層。因此,堆疊實現(xiàn)克服了 SPAD 傳感器的傳統(tǒng)限制,適用于更廣泛的應用。

B. 時間對比傳感

基于事件的視覺傳感器 (EVS) 檢測超過預設相對閾值的單個像素時間對比度,以跟蹤相對光變化的時間演變,并為絕對強度的無幀像素級測量定義采樣點。自 2006 年首次報告 EVS以來,已經(jīng)提出了許多使用 EVS 的應用,例如由于記錄數(shù)據(jù)的時間精度導致的高速低功耗機器視覺、對時間冗余的固有抑制導致減少后處理成本和廣泛的場景內(nèi) DR 操作 。盡管像素尺寸在 2019 年通過 BI 結(jié)構(gòu)減小到 9 μm 的間距,但由于大量像素級模擬信號處理,EVS 遭受了大像素尺寸和通常小分辨率的困擾。因此,EVS 特別受益于具有像素級 Cu-Cu 連接的堆疊器件結(jié)構(gòu)的進步。

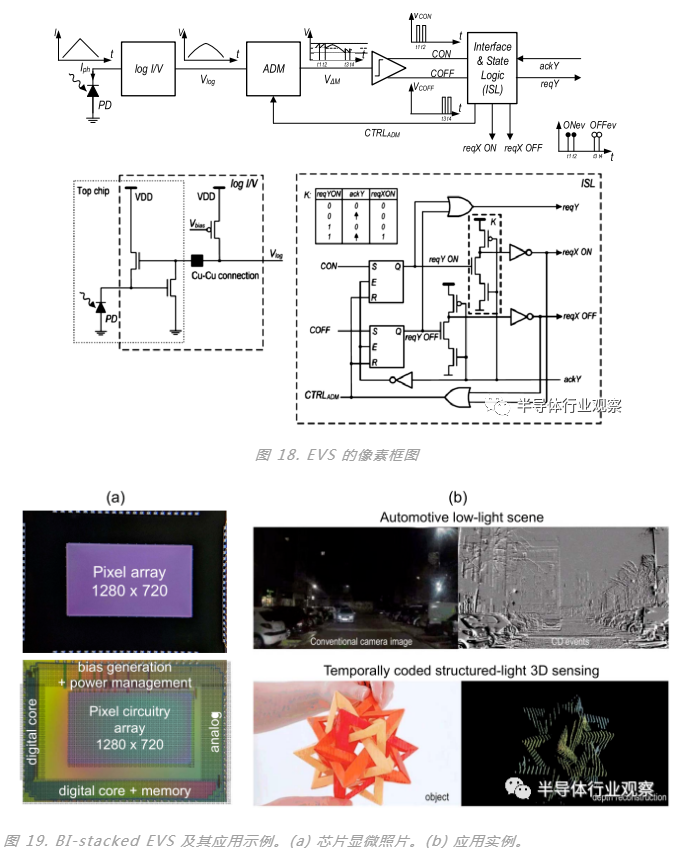

2020 年報道了 1280 × 720 4.86-μm 像素間距 BI 堆疊 EVS。圖 18 顯示了對比度檢測 (CD) 功能的像素框圖以及像素內(nèi)異步讀出接口和狀態(tài)邏輯塊的示意圖。光電流被轉(zhuǎn)換為電壓信號 Vlog,然后通過使用電平交叉比較器檢測的異步增量調(diào)制 (ADM) 獲得對比度變化。圖 19(a) 中的 BI-stacked EVS 實現(xiàn)了 1-μs 行級時間戳、每秒 10.66 億個事件 (eps) 的最大事件率,以及 35 nW/像素和 137 pJ/事件的數(shù)據(jù)格式化流水線 用于高速低功耗機器視覺應用。圖 19(b) 顯示了一些示例應用的傳感器操作。大約 1 勒克斯的交通場景記錄展示了低光對比敏感度。低延遲像素和高速讀出操作帶來的高時間精度允許傳感器在 3D 深度傳感應用中解碼時間編碼的結(jié)構(gòu)光圖案。圖 20 顯示了 EVS 中像素間距的趨勢。由于堆疊設備技術,對于百萬像素的實際使用案例EVS 的像素尺寸現(xiàn)在低于 5 μm 間距。

圖 20. EVS 中像素間距的趨勢。

C. 不可見光成像

堆疊器件技術還有助于在混合集成中使用非硅光電探測器實現(xiàn)不可見光成像。具有混合集成的非硅光電探測器的示例包括 InGaAs 光電探測器、Ge-on-Si光電探測器和有機光電導膜。在本節(jié)中,總結(jié)了使用 Cu-Cu 混合鍵合的 InGaAs 傳感器的最新成果。

工業(yè)、科學、醫(yī)療和安全應用對短波紅外 (SWIR) 范圍(即 1000 到 2000 nm 之間的波長)成像的需求一直在增加。InGaAs 器件已用于 SWIR 傳感器,因為它們在 SWIR 范圍內(nèi)的吸收特性是硅基器件無法覆蓋的。在傳統(tǒng)的 InGaAs 傳感器中,光電二極管陣列 (PDA) 的每個像素通過使用凸塊的倒裝芯片混合連接到讀出集成電路 (ROIC)。由于凸塊的可擴展性有限,這種結(jié)構(gòu)通常使細間距像素陣列的制造復雜化。2019 年,推出了一種 InGaAs 圖像傳感器,其中 PDA 的每個 5-?m 像素使用 Cu-Cu 鍵合連接到 ROIC。InGaAs/InP 異質(zhì)結(jié)構(gòu)在直徑小于 4 的市售小型 InP 襯底上外延生長。如圖 21 所示,外延 InGaAs/InP 晶圓被切割成芯片,并使用 III-V 裸片到硅晶圓工藝轉(zhuǎn)移到大型硅晶圓上。在制造 Cu 焊盤后,III-V/Si 異質(zhì)晶片使用 Cu-Cu 鍵合將每個 III-V 像素連接到 ROIC 與 ROIC 混合。圖 22 顯示了倒裝芯片凸塊的接觸間距趨勢和 InGaAs 傳感器的 Cu-Cu 鍵合。使用凸塊的倒裝芯片混合是制造 InGaAs 傳感器的傳統(tǒng)方法,由于工藝裕度窄且可重復性差,不適合按比例縮小像素間距。然而,自 2016 年以來,Cu-Cu 雜化已用于 CMOS 圖像傳感器的大規(guī)模生產(chǎn)并具有高產(chǎn)量,是縮放互連到 InGaAs 傳感器的關鍵技術。圖 22 還顯示了在有霧的場景中涉及檢查和安全監(jiān)控的應用示例。因此,InGaAs 圖像傳感器通過像素級 Cu-Cu 連接為 HD SWIR 成像創(chuàng)造了條件。

V.智能視覺傳感器

在物聯(lián)網(wǎng) (IoT) 市場、零售、智慧城市和類似應用中,對具有 AI 處理能力的相機產(chǎn)品的需求正在增長。此類邊緣設備上的 AI 處理能力可以解決與純云計算系統(tǒng)相關的一些問題,例如延遲、云通信、處理成本和隱私問題。具有AI處理能力的智能相機的市場需求包括小尺寸、低成本、低功耗和易于安裝。然而,傳統(tǒng)的 CMOS 圖像傳感器僅輸出捕獲圖像的原始數(shù)據(jù)。因此,在開發(fā)具有AI處理能力的智能相機時,需要使用包含圖像信號處理器(ISP)、卷積神經(jīng)網(wǎng)絡(CNN)處理、DRAM等能力的IC。

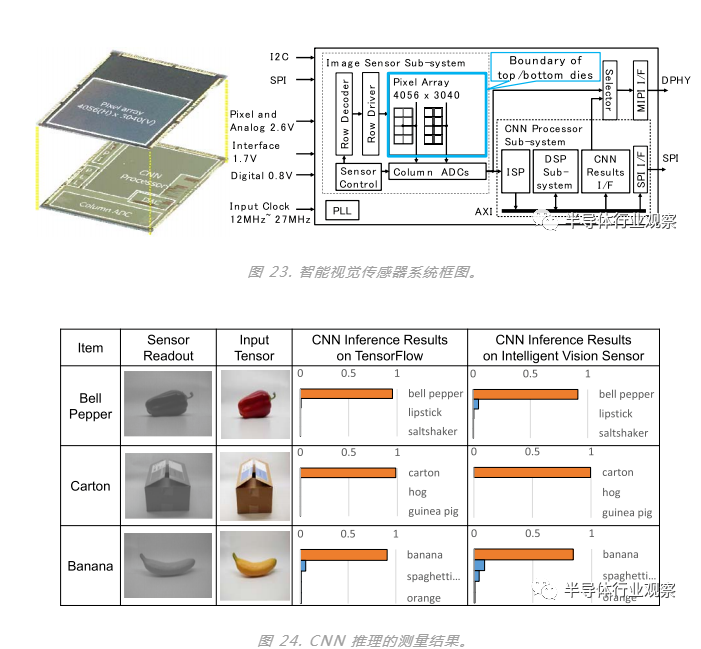

2021 年報道了一種由 1230 萬像素和一個專用于 CNN 計算的 DSP 組成的堆疊 CMOS 圖像傳感器。如圖 23 所示,該傳感器包含一個集成解決方案,該解決方案具有完整的圖像捕獲傳輸?shù)?CNN 推理處理器,并且可以以 120 fps 的速度處理,包括使用 4.97 TOPS/W DSP 的圖像捕獲和片上 CNN 處理。處理模塊有一個用于 CNN 輸入預處理的 ISP、一個為 CNN 處理優(yōu)化的 DSP 子系統(tǒng),以及一個用于存儲 CNN 權(quán)重和運行時內(nèi)存的 8-MB L2 SRAM。圖 24 顯示了使用 MobileNet v1 的 CNN 推理結(jié)果的一些示例。DSP 子系統(tǒng)展示了與 TensorFlow 類似的推理結(jié)果。智能視覺傳感器能夠在傳感器上運行完整的 CNN 推理過程,可以通過 MIPI 接口將捕獲的圖像作為原始數(shù)據(jù)和 CNN 推理結(jié)果輸出在同一幀中。該傳感器還支持僅從 SPI 接口輸出 CNN 推理結(jié)果,以啟用小型相機,降低系統(tǒng)功耗和成本。傳感器上的 CNN 推理處理器允許用戶將他們喜歡的 AI 模型編程到嵌入式存儲器中,并根據(jù)系統(tǒng)使用位置的要求或條件對其進行重新編程。例如,安裝在設施入口處時,可用于統(tǒng)計進入設施的訪客人數(shù);安裝在商店貨架上,可用于檢測缺貨情況;當在天花板上時,它可以用于熱圖(heat mapping)商店訪客。智能視覺傳感器有望使用靈活的 AI 模型為各種應用提供低成本的邊緣 AI 系統(tǒng)。

VI. 結(jié)論

本文回顧了具有堆疊器件結(jié)構(gòu)的圖像傳感器架構(gòu)的最新成果。通過采用傳感器像素和 CMOS 電路優(yōu)化工藝技術實現(xiàn)的高度并行 ADC,堆疊器件結(jié)構(gòu)極大地提高了圖像傳感器性能,特別是在高幀速率和高像素分辨率下。在最近的工作中,已經(jīng)使用像素并行堆疊電路和/或更智能的處理單元提出了一些建議,并取得了一些成果。這些新挑戰(zhàn)需要更高的可擴展性、針對每個功能的工藝技術的更多優(yōu)化以及更高的面積效率。光電探測器、像素前端電路、模擬混合信號和數(shù)字處理器以及存儲器可以更有效地集成,如圖 25 所示,未來圖像傳感器架構(gòu)通過器件堆疊技術擴展功能將獲得進一步的發(fā)展。

圖 25.堆疊式 CMOS 圖像傳感器的演進與未來展望。

本文來自IEEE,作者Yusuki Oike,版權(quán)也歸他們所有,本翻譯僅供讀者參考。