在操作系統(tǒng)中,BootLoader在內(nèi)核運行之前先啟動,可以初始化硬件設(shè)備、建立內(nèi)存空間映射圖,從而按照設(shè)定啟動軟硬件環(huán)境,使之工作在預(yù)期狀態(tài)。

其實FPGA也是如此,在上電之后,需要有邏輯去FLASH讀取數(shù)據(jù),然后配置FPGA,使得可以正常運行我們設(shè)計的代碼。

FPGA FLASH的固化,可以使用AS模式,也可以采用JTAG以bridge的方式去固化。但是,提倡經(jīng)濟低碳的我們,為了環(huán)保與體積,非得使用一個JTAG的方式,既可以實現(xiàn)在線下載與Debug,也可以通過橋接完成FLASH的固化。

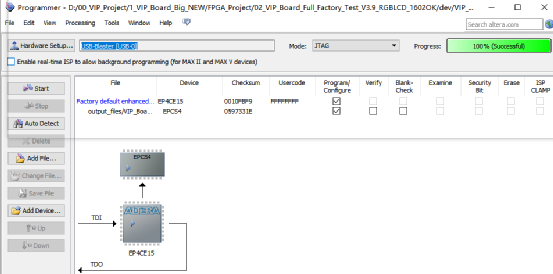

不管是Altera還是Xilinx,都支持通過JTAG橋接方式對FLASH的燒錄,以Altera為例,采用Quartus將sof轉(zhuǎn)成jic后,直接用JTAG燒錄FLASH。由于FLASH固化在上電測試或者最終產(chǎn)品化的時候采用,因此雖然麻煩點,但考慮到經(jīng)濟效益,也可以忍。其GUI界面如下:

那么,骨骼精奇的易靈思,也是這樣的嗎?如果這樣就沒有下文了。。。

1.1.易靈思FPGA通過JTAG固化Flash的方法

易靈思的工具鏈神奇的將這一步到位的操作,分成了獨特的2步,請見下文分解。

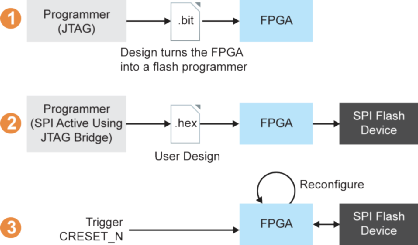

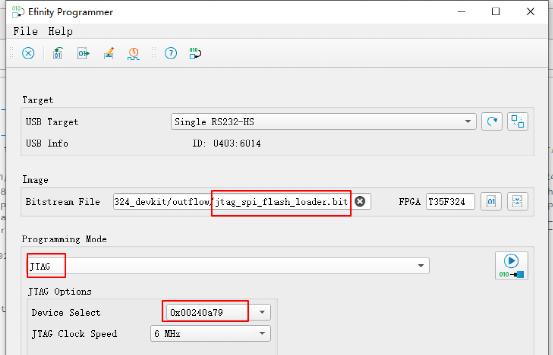

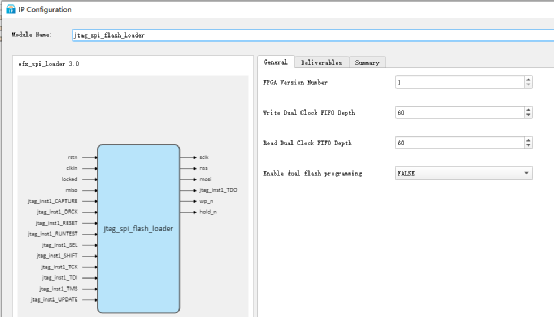

1)首先,通過JTAG下載一個FLASH橋接的固件(bit文件),如下圖所示:

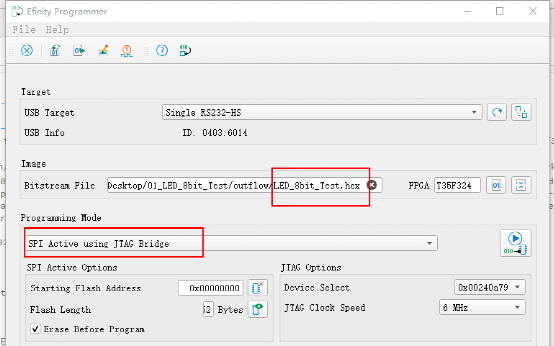

2)接著,選擇當前設(shè)計的hex文件,并且選擇使用JTAG橋接下載flash,點擊開始將數(shù)據(jù)送給1)中spi_flash_loader的固件,然后它接收數(shù)據(jù)后寫入到片外FLASH中。

備注:這里軟件默認會自動完成擦除以及寫入新的固件。

3)CRESET_N復(fù)位或者重新上電后,F(xiàn)PGA會重新從FLASH讀取數(shù)據(jù)并且完成新的配置,最后FPGA按照最新的設(shè)計進行工作。

那么,問題來了,跟Quartus II相比,這里多了spi_flash_loader的bit,這個bit官方并沒有直接提供給我們,初來乍到的小伙伴也就懵逼了。

然而現(xiàn)狀就是:易靈思目前需要針對不同的FPGA硬件,需要自己制作FPGA的SPI_Flash_Loader啟動文件,具體流程如下:

1.2.易靈思FPGA 制作FLASH橋接文件

整體流程:配置spi_flash_loader的IP,生成的example,然后修改相關(guān)引腳配置,具體如下:

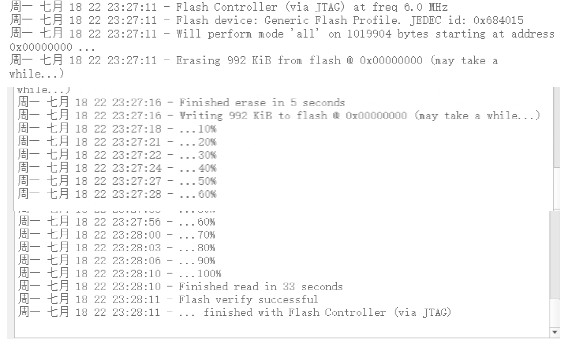

1)打開Efinity軟件,選中JTAG SPI FLASH Loader,如下圖

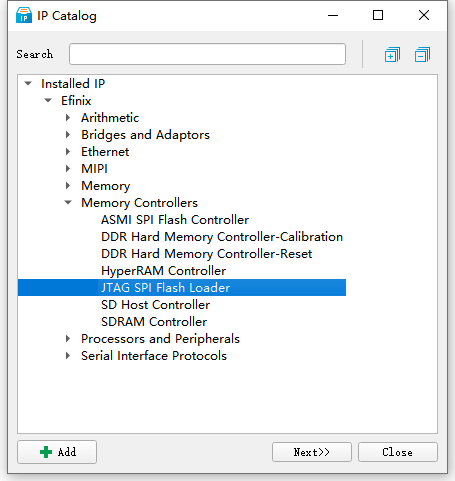

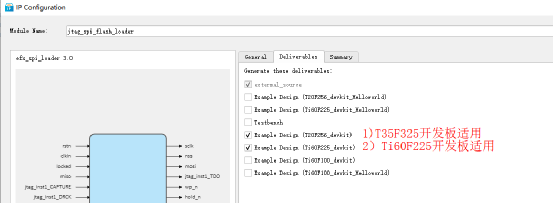

2)輸入IP名稱jtag_spi_flash_loader,參數(shù)默認保持不變

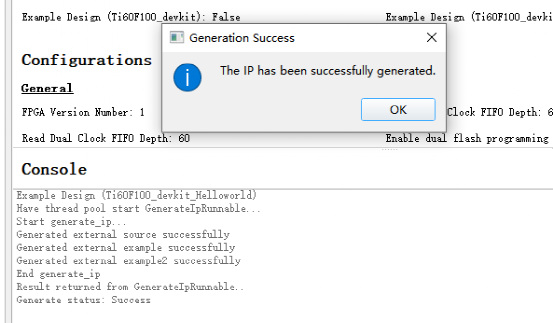

3)選擇需要生成的Demo,不同系列FPGA不一樣,Generate

這里特別注意,前面1)中非得打開一個(任意的)工程,否則無法給你生成這個IP

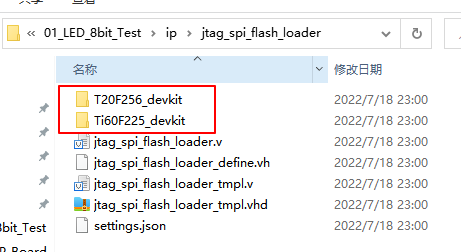

4)回到當前工程的文件目錄,在ip文件夾下會找到j(luò)tag_spi_flash_loader的example,如下所示:

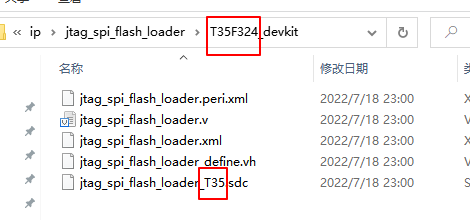

5)這里以T35為例,我們修改一下相關(guān)文件名,如下:

6)然后用Efinify軟件打開工程文件:jtag_spi_flash_loader.xml

7)刪除*T20.sdc,替換為上圖的*T35.sdc

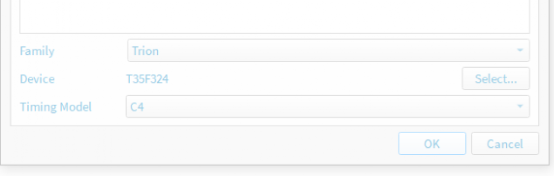

8)File→Edit Project,在Device中將FPGA型號修改為T35F324

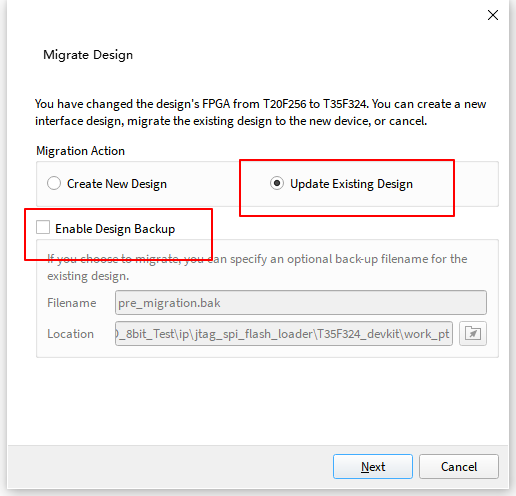

9)默認選擇Update Existing Design,干掉Backup

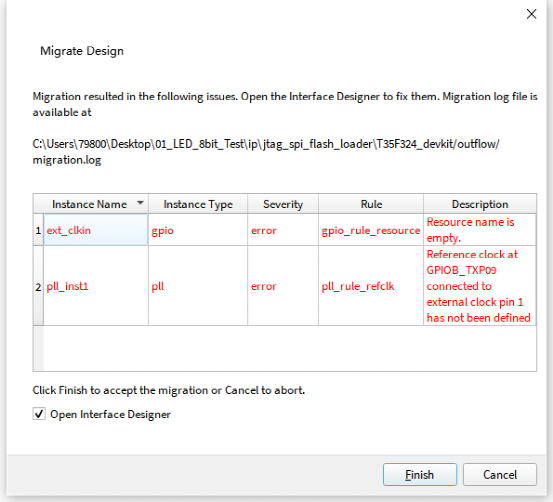

確認后完成并報錯,時鐘不可避免地需要重新配置,如下圖:

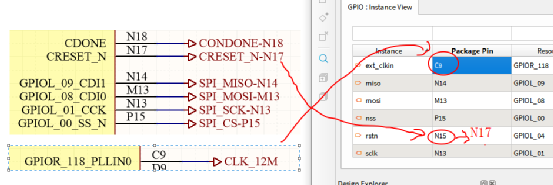

10)點擊Finish打開Interafce,我們首先進行時鐘rstn引腳的修改,如下:

備注:這里FLASH IO剛好和T20是一樣的,但是CRESET_N不一樣。

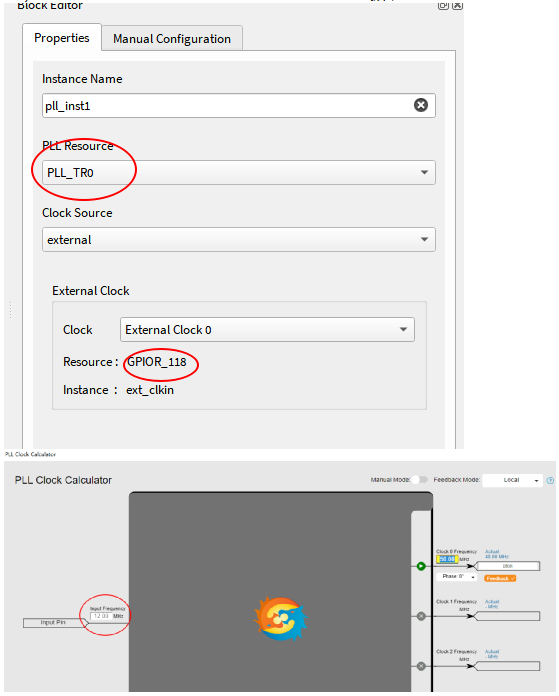

11)由于我設(shè)計的T35F324開發(fā)板使用的是12MHz的晶振,因此對PLL的輸入及位置修改如下:

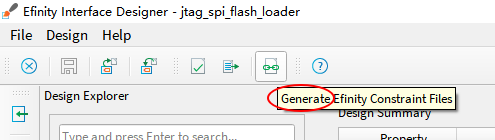

12)Check Design,0W0E后,然后生成約束文件

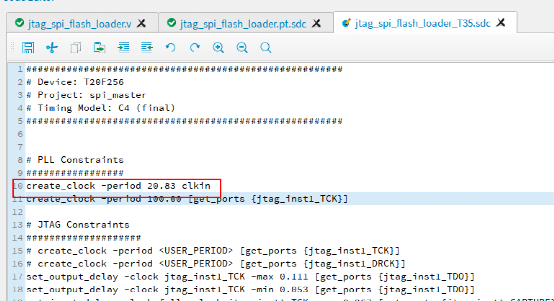

13)回到Efinity界面,采用template中的sdc模板(主要是時鐘變了,12M PLL輸入只能出來48M,出不來50M(這PLL有點弱))

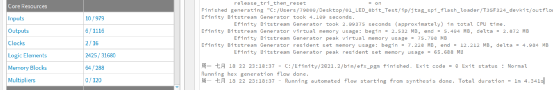

14)Dashboard中點擊啟動編譯流程,軟件將自動跑完新的bit。

至此,基于我設(shè)計的T35F324開發(fā)板(12M時鐘)的JTAG SPI_FLASH_Loader鏡像,制作完成。如果你用了同一個系列的FPGA,基本上只需要在Interface修改引腳及時鐘就可以完成新硬件的FLASH Loader的制作。

1.3.所以為啥不能得更好呢??

我不得不繼續(xù)深入探討一個問題:為什么Altera FPGA不用那么麻煩?

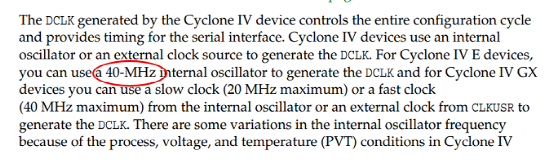

既然FPGA上電后自己會從FLASH中引導(dǎo)程序,那么說明FPGA內(nèi)部一定有時鐘源。查詢Altera的相關(guān)手冊,得知Cyclone IV系列FPGA內(nèi)部有40MHz的時鐘源:

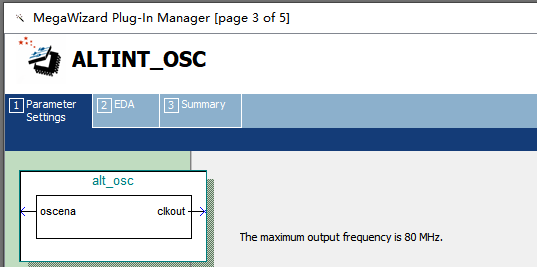

同時在Quartus II也把這部分功能開放給用戶用了,可在IP列表中找到,如下:

備注:這里又說了最大80MHz,且不去深究了。

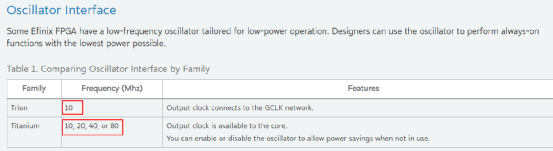

于是我又去研究了Efinity的手冊,我也找到了肯定的答案,如下所示T與Ti系列FPGA的內(nèi)部時鐘源:

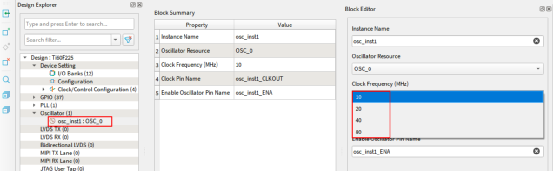

另外,T35軟件沒有開放內(nèi)部osc給用戶,Ti60開放內(nèi)部osc了,如下(Interface中):

那么我們必須要檢討,你既然有內(nèi)部時鐘,同時確定了型號工具相關(guān)的IO分配,那為啥這部分功能就不能做到工具鏈里面去呢?有完美強迫癥的我再也無法入睡。。。

問了FAE,也沒能給出更好的答案,這讓初學(xué)者內(nèi)心受到了N點的傷害。只能說,我又看到了進步空間。,呼吁原廠,在未來軟件版本的release中,盡快將jtag spi_flash_loader的功能,包含到軟件中去。

我們向往更好的明天。。。

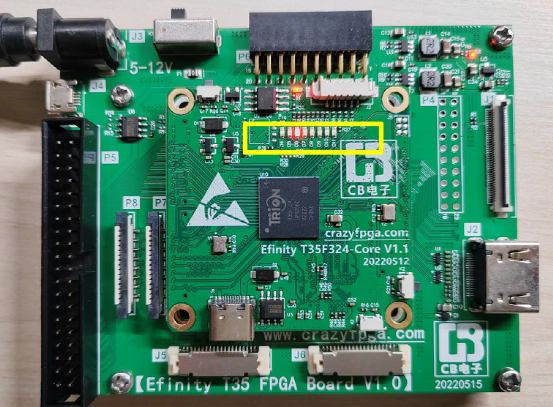

最后,給個圖,在我自研的T35F324開發(fā)板上,下載前面jtag spi_flash_loader.bit后,再下載流水燈的hex文件,8個LED歡快地跑了起來。

如果有些地方我理解的不對,也歡迎在評論區(qū)使勁的懟我,謝謝!!

更多細節(jié),請轉(zhuǎn)crazyfpga.taobao.com(“CB電子”淘寶店鋪)了解。

對易靈思FPGA感興趣的朋友,歡迎進FPGA討論組交流,我們共同進步,等待“世界末日”過去……

由于開發(fā)板并非針對學(xué)生市場,而是偏向于公司/行業(yè)用戶,加之前期開發(fā)投入的巨大,以及人力物力暴漲,因此開發(fā)板價格并不會那么親民,請大家慎重考慮。另外,從平臺轉(zhuǎn)過來的采購的朋友,在本帖發(fā)布一個月內(nèi),可享受88折體驗價(口號:104)。

由于群規(guī)模在短時間內(nèi)超過了200人,無法再掃碼入群,請有興趣的朋友添加客服木頭同學(xué)的微信,再邀請入群。

原文鏈接:https://mp.weixin.qq.com/s/T2Wd8lESXGXKODR_e1oSgQ

電子技術(shù)應(yīng)用專欄作家

更多信息可以來這里獲取==>>電子技術(shù)應(yīng)用-AET<<