隨著物聯(lián)網(wǎng)應(yīng)用的采用勢頭越來越猛,嵌入式開發(fā)社區(qū)面臨的壓力也越來越大,他們需要平衡每個設(shè)計的可用計算資源、延遲、成本和尺寸。由于其實時性,對云連接的關(guān)注也被視為某些發(fā)展的挑戰(zhàn),從而導(dǎo)致混合“霧”計算方法。配置本地網(wǎng)關(guān)以向霧方法提供本地云方面可能需要相當(dāng)高的計算需求和算法處理。許多負(fù)責(zé)開發(fā)網(wǎng)關(guān)設(shè)備的設(shè)計人員面臨的挑戰(zhàn)是了解其計算要求的多樣性。一些應(yīng)用,尤其是工業(yè)物聯(lián)網(wǎng)部署中的應(yīng)用,可能涉及相當(dāng)復(fù)雜的電機(jī)控制或視覺處理任務(wù)。對于這些要求,不僅需要高水平的計算能力,還需要實時確定性行為。雖然高端 CPU 通常是首選設(shè)備,但還有許多其他設(shè)備正在引起開發(fā)人員的注意。其中之一是現(xiàn)場可編程門陣列 (FPGA),由于其硬確定性能力,它正在迅速發(fā)展。

那些不熟悉使用 FPGA 的人面臨著許多關(guān)于這些設(shè)備的復(fù)雜性、成本和功耗特性的神話。許多開發(fā)人員認(rèn)為 FPGA 可能只適用于高度專業(yè)化、高成本的軍事系統(tǒng),但目前的情況與這種情況相去甚遠(yuǎn)。在當(dāng)今的云連接世界中,F(xiàn)PGA 的最大應(yīng)用是數(shù)據(jù)中心應(yīng)用,除了加速搜索功能外,它們還用于使用神經(jīng)網(wǎng)絡(luò)深度學(xué)習(xí)技術(shù)進(jìn)行圖像識別搜索。

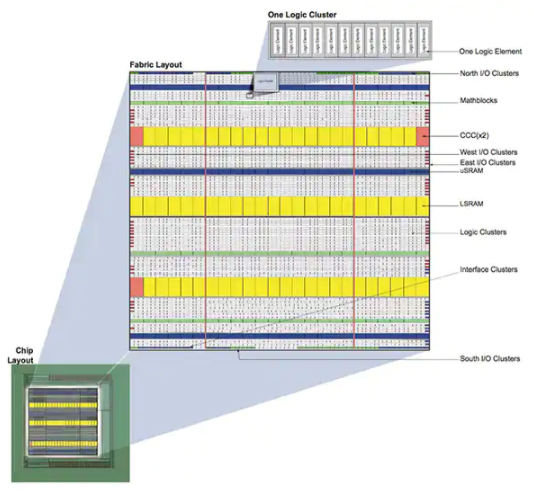

毫無疑問,精通構(gòu)建基于微控制器或微處理器的系統(tǒng)的嵌入式開發(fā)人員在考慮使用 FPGA 時會被前面的學(xué)習(xí)曲線嚇倒。對大多數(shù)人來說,顯著的區(qū)別將是從基于軟件的思維過程轉(zhuǎn)向硬件“門”方法。FPGA 被認(rèn)為是最接近設(shè)計定制 IC 的最接近的東西,它可以完全按照您的要求進(jìn)行設(shè)計,F(xiàn)PGA 本質(zhì)上是通用門和單元的空白畫布,是使用硬件描述語言 (HDL) 編程或連接在一起的結(jié)構(gòu)(圖1)。學(xué)習(xí)數(shù)字邏輯的電子工程師很快就會對 FPGA 背后的基本概念感到賓至如歸,而其他人可能會發(fā)現(xiàn)有關(guān)該主題的在線進(jìn)修課程很有用。Simon Monk 對 FPGA 進(jìn)行編程。

圖 1:FPGA 器件的功能框圖。

隨著 FPGA 在各種應(yīng)用中的使用勢頭越來越猛,有關(guān)它們的信息的可用性也越來越高。這主要是由領(lǐng)先的 FPGA 供應(yīng)商推動的,他們投入巨資提供免費的開源軟件工具,以幫助定義和加速設(shè)計流程。在 FPGA 架構(gòu)中集成 MCU 以創(chuàng)建 FPGA 片上系統(tǒng) (SoC) 設(shè)備進(jìn)一步有助于管理 FPGA 并將其集成到最終應(yīng)用中。極大地簡化了學(xué)習(xí)和開發(fā)過程,有助于在更廣泛的應(yīng)用中使用 FPGA,并促進(jìn)開放社區(qū)論壇的發(fā)展。在創(chuàng)客社區(qū)內(nèi)采用 FPGA 也有助于激發(fā)對其功能的興趣,并為 Mojo 和 Papilio 等許多眾籌 FPGA 評估板項目做出了貢獻(xiàn)。FPGA 制造商還努力通過創(chuàng)建在更廣泛的開源社區(qū)中得到很好支持的開發(fā)套件和評估板來使設(shè)計更易于訪問。所有這些舉措共同創(chuàng)造了豐富的技術(shù)信息和支持資源,有助于鼓勵設(shè)計人員考慮他們的第一個 FPGA 設(shè)計。

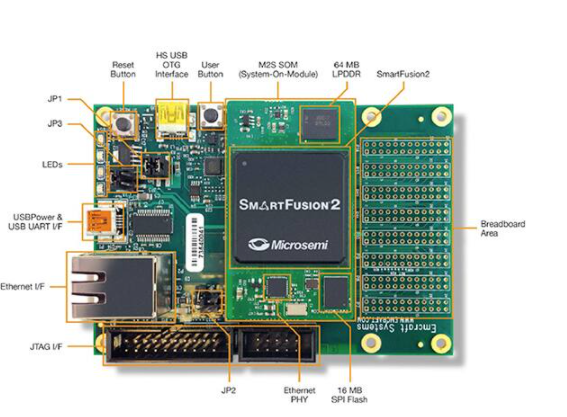

這種評估板的一個例子是Microsemi 的 SmartFusion2 入門套件,如圖 2 所示。

圖 2:SmartFusion2 入門套件。

該入門套件包含一個系統(tǒng)級模塊 (SOM),其中包含帶有相關(guān)存儲器和時鐘的 Microsemi SmartFusion2 FPGA SoC 器件,以及一個承載原型設(shè)計區(qū)域、電源轉(zhuǎn)換器和電源管理 IC 的 SmartFusion2 基板,該入門套件提供了一個完整的平臺開始您的第一個設(shè)計。

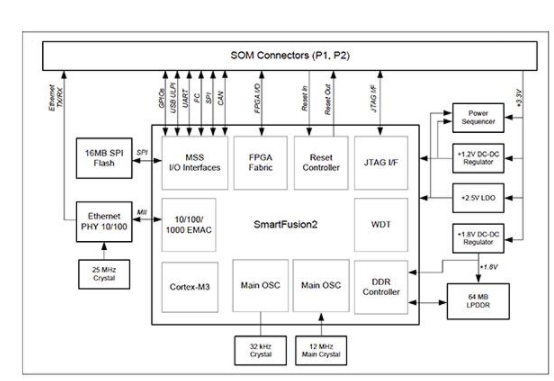

FPGA SoC 器件具有 32 位 ARM? Cortex?-M3 微控制器內(nèi)核,在 FPGA 架構(gòu)中實現(xiàn)為微控制器子系統(tǒng) (MSS)。它支持 64 MB DDR 內(nèi)存和 16 MB 閃存,并且能夠運行高達(dá) 142 MHz。圖 3 顯示了 SmartFusion2 SOM 的功能框圖。

圖 3:SmartFusion2 系統(tǒng)級模塊的功能框圖。

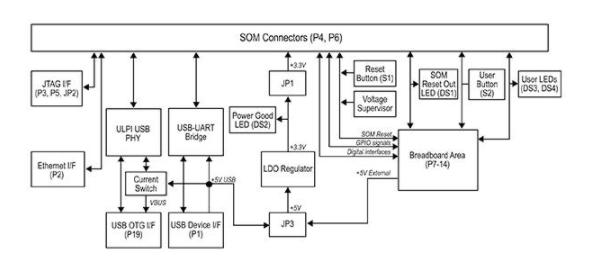

SOM 還包括一個 JTAG 接口、一個看門狗定時器、一個以太網(wǎng)接口以及大量 GPIO 和串行(I 2 C、CAN、SPI 和 UART)接口。基板連接和用戶 I/O 功能的全部范圍如圖 4 所示。FPGA 架構(gòu)的大小取決于模型,范圍從 6060 到 56520 個邏輯元件。SoC 代碼運行 uClinux 內(nèi)核,通過提供對所有 Linux 工具(包括 SSH、FTP 和 Telnet 等網(wǎng)絡(luò)實用程序)的訪問,進(jìn)一步幫助開發(fā)過程。

圖 4:SmartFusion2 基板功能框圖。

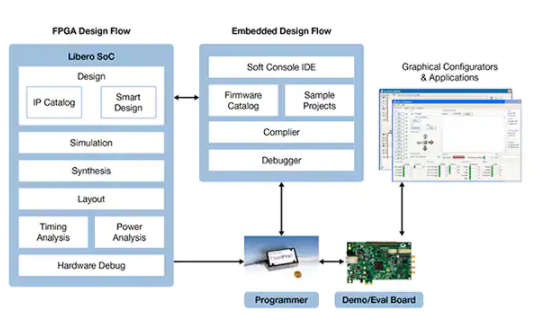

在對 FPGA SoC 進(jìn)行編程時,Microsemi 的設(shè)計流程工具Libero可從 Microsemi 網(wǎng)站免費下載。套件中還包括作為 Libero 項目設(shè)置的完整 FPGA SoC 和電路板。Libero 將 FPGA 設(shè)計的設(shè)計流程與嵌入式應(yīng)用程序開發(fā)集成在一起,如圖 5 所示。

圖 5:Libero 將傳統(tǒng)的 FPGA 設(shè)計流程與微控制器固件開發(fā)集成在一起。

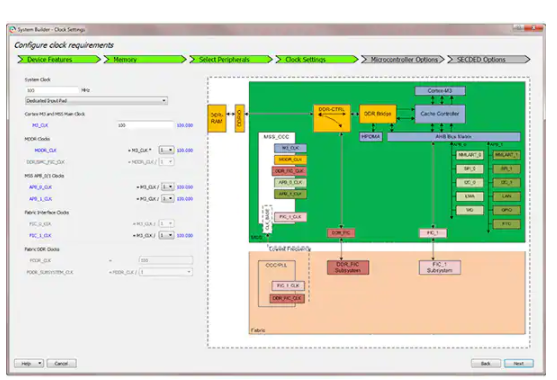

Libero 快速入門指南很好地介紹了使用 Libero 和整個設(shè)計流程。Libero 的一個關(guān)鍵部分是 System Builder 向?qū)В▓D 6),它通過提出一系列問題來幫助開發(fā)人員進(jìn)行架構(gòu)設(shè)計過程,這些問題有助于塑造基本系統(tǒng)要求、配置選項,并在需要時向架構(gòu)添加額外的外圍設(shè)備。

圖 6:Libero System Builder 向?qū)?- MSS 中時鐘功能的示例設(shè)置。

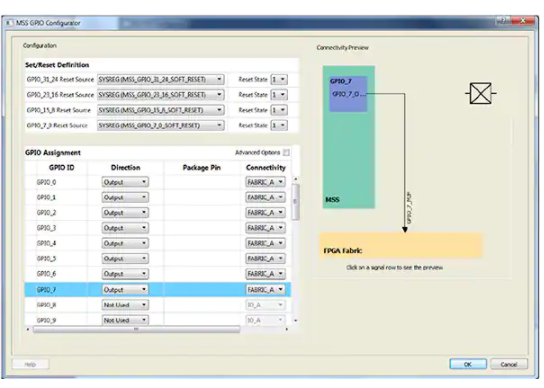

與傳統(tǒng)的開發(fā)實踐保持一致,“Hello World”第一程序的現(xiàn)代解釋是通過閃爍的 LED 設(shè)計項目實現(xiàn)的。在本教程中完整記錄,該文檔指導(dǎo)工程師完成設(shè)計流程以實現(xiàn)此基本設(shè)計功能。圖 7 是本教程的屏幕截圖,突出顯示了將輸出信號分配給指定的 GPIO 引腳,該引腳在基板上連接了一個 LED。

圖 7:閃爍 LED 示例中的 GPIO 引腳分配。

結(jié)論

FPGA 在原始計算能力、設(shè)計靈活性和每瓦性能方面可為開發(fā)人員提供很多幫助。以前被視為程序復(fù)雜、耗電大且價格昂貴的設(shè)備,隨著越來越多的商業(yè)應(yīng)用利用其廣泛的功能,它們在最近已經(jīng)成熟了很多。眾所周知,在工程師創(chuàng)建復(fù)雜的神經(jīng)網(wǎng)絡(luò)設(shè)計之前,有一個合理的學(xué)習(xí)曲線。但是,由于本文中描述的開發(fā)工具的可用性,邁出第一步變得容易得多。

更多信息可以來這里獲取==>>電子技術(shù)應(yīng)用-AET<<