1前言

本應(yīng)用筆記介紹如何管理 STM32 產(chǎn)品中的內(nèi)存保護(hù)單元(MPU)。MPU 是用于存儲器保護(hù)的可選組件。STM32 微控制器(MCU)中嵌入 MPU 之后變得更穩(wěn)健可靠。在使用 MPU 之前,必須對其進(jìn)行編程并加以啟用。如果 MPU 沒有啟用,則存儲系統(tǒng)的行為不會變化。

2概述

MPU 可以使嵌入式系統(tǒng)更加穩(wěn)健和安全:? 禁止用戶應(yīng)用程序破壞關(guān)鍵任務(wù)(例如操作系統(tǒng)核心)使用的數(shù)據(jù)? 將 SRAM 存儲區(qū)域定義為非可執(zhí)行(禁止執(zhí)行 XN),以防止代碼注入攻擊? 修改存儲訪問屬性MPU可最多保護(hù)16個內(nèi)存區(qū)域。在 Armv6、Armv7 架構(gòu)(Cortex-M0+、M3、M4、M7)下,這些區(qū)域可以依次擁有 8 個子區(qū)域(前提是區(qū)域至少有 256 字節(jié)))。

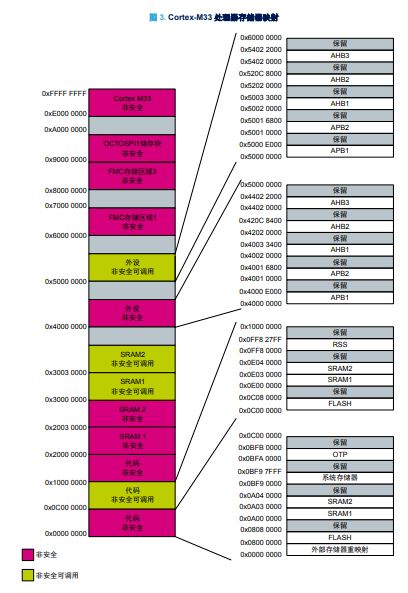

在 STM32 中,受保護(hù)區(qū)域的確切數(shù)量可能因內(nèi)核和器件而有所不同,請參閱 Cortex-M33 MPU 寄存器獲取詳細(xì)信息。子區(qū)域的大小都是相等的,可以根據(jù)子區(qū)域號進(jìn)行啟用或禁用。因?yàn)樽钚^(qū)域大小是由緩存行長度(32 字節(jié))驅(qū)動的,所以 8 個 32 字節(jié)的子區(qū)域?qū)?yīng)一個 256 字節(jié)的區(qū)域。區(qū)域的編號為 0 至 15。

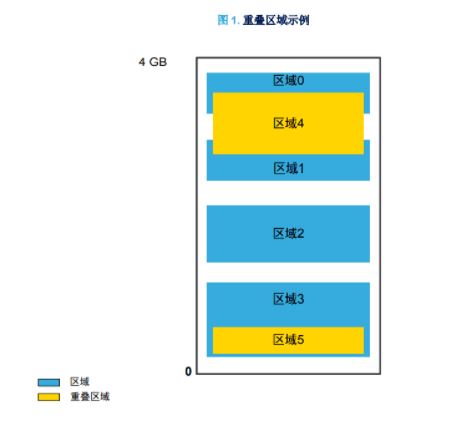

此外,還有一處默認(rèn)區(qū)域,其 id 為-1。所有編號 0-15 的存儲區(qū)域的優(yōu)先級高于默認(rèn)區(qū)域。這些區(qū)域可以重疊,也可以嵌套。區(qū)域 0-15 的優(yōu)先級由低到高,這也決定了區(qū)域重疊的方式。優(yōu)先級是固定的,不可更改。在 Armv8 架構(gòu)(Cortex-M33)中,使用起始地址和終止地址來定義區(qū)域,使開發(fā)人員能夠以靈活、簡單的方式組織這些區(qū)域。

此外,正是區(qū)域大小的可靈活配置得到提升,故Cortex-M33就沒有子區(qū)域的概念了。下圖顯示的示例包含六個區(qū)域。該示例顯示區(qū)域 4 與區(qū)域 0 和 1 重疊。區(qū)域 5 完全包含在區(qū)域 3 內(nèi)。因?yàn)閮?yōu)先級是遞增的,所以重疊區(qū)域(橙色)優(yōu)先。因此,如果區(qū)域 0 是可寫的,而區(qū)域 4 不可寫,那么位于區(qū)域 0 和區(qū)域 4 重疊部分的地址為不可寫。

Conclusion:

在 Armv8 架構(gòu)(Cortex-M33)中,現(xiàn)在不允許區(qū)域重疊。由于 MPU 區(qū)域的定義更加靈活,因此沒有必要重疊MPU 區(qū)域。

MPU 是統(tǒng)一的,意味著沒有單獨(dú)的區(qū)域用于數(shù)據(jù)和指令。

MPU 還可以用于定義其他存儲器屬性(如可緩存性),可以導(dǎo)出到系統(tǒng)級緩存單元或存儲存控制器。Arm 架構(gòu)中的存儲器屬性設(shè)置可以支持兩種級別的緩存:內(nèi)部緩存和外部緩存。STM32F7 和 STM32H7 系列僅支持一種級別的緩存(L1-緩存)。

緩存控制由緩存控制寄存器實(shí)現(xiàn)全局控制,但 MPU 可以指定緩存策略以及區(qū)域是否可緩存。

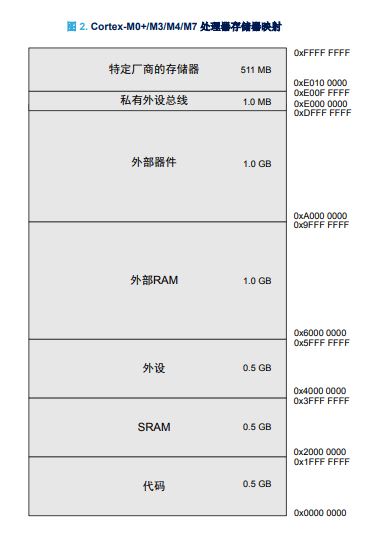

2.1存儲器模型

在 STM32 產(chǎn)品中,處理器具有固定的默認(rèn)存儲器映射,可提供最多 4 Gb 的可尋址存儲器。

3Cortex-M0+/M3/M4/M7

存儲器類型、寄存器和屬性

存儲器映射和 MPU 編程將存儲器映射分為多個區(qū)域。每個區(qū)域都有已定義的存儲器類型和存儲器屬性。存儲器類型和屬性決定該區(qū)域的訪問行為。

3.1 存儲器類型

有三種常見的存儲器類型:

? 普通存儲器:允許 CPU 以有效方式安排字節(jié)、半字和字的加載和存儲(編譯器不了解存儲器區(qū)域類型)。對于普通存儲器區(qū)域,CPU 不一定按照程序中列出的順序執(zhí)行加載/存儲操作。

? 器件存儲器:在器件區(qū)域內(nèi),負(fù)載和存儲是嚴(yán)格按照順序進(jìn)行的。這是為了確保以正確的順序設(shè)置寄存器。

? 強(qiáng)排序存儲器:所有操作始終按以編程方式列出的順序執(zhí)行,CPU 會等待加載/存儲指令執(zhí)行(有效的總線訪問)結(jié)束,然后執(zhí)行程序流中的下一條指令。這可能導(dǎo)致性能損失。

3.2 存儲器屬性

區(qū)域的屬性與大小寄存器(MPU_RASR)是設(shè)置所有存儲器屬性的地方。該表顯示了 MPU_RASR 寄存器中對于區(qū)域的屬性和大小的簡要描述。

前一個表格中的參數(shù)詳情如下:

? XN 標(biāo)志位控制代碼的執(zhí)行。為了在區(qū)域內(nèi)執(zhí)行指令,特權(quán)級別必須有讀訪問權(quán)限,而 XN 必須為 0。否則,會產(chǎn)生 MemManage 報錯。

? 數(shù)據(jù)訪問權(quán)限(AP)字段定義存儲區(qū)域的 AP。

下表對訪問權(quán)限進(jìn)行了說明:

? S 字段面向可共享的存儲區(qū)域:存儲系統(tǒng)在一個有多個總線主控的系統(tǒng)(例如,一個處理器帶一個 DMA 控制器)中提供總線主控之間的數(shù)據(jù)同步。強(qiáng)排序的存儲器始終可共享。如果多個總線主控可以訪問一個不可共享的存儲區(qū)域,軟件必須確保總線主控之間的數(shù)據(jù)一致性。STM32F7 系列和 STM32H7 系列不支持硬件一致性。S 字段相當(dāng)于不可緩存的存儲器。

? TEX、C 和 B 位用于定義區(qū)域的緩存屬性,以及(在某種程度上)可共享性。按下表對其進(jìn)行編碼。

在 STM32 微控制器中加入 MPU 使其穩(wěn)健、可靠,而且在某些情況下更安全 - 防止應(yīng)用程序任務(wù)訪問或破壞其他任務(wù)使用的堆棧和數(shù)據(jù)存儲器。該應(yīng)用筆記描述了不同的存儲器屬性、類型和 MPU 寄存器。其中還提供了 MPU(使用 STM32Cube HAL)設(shè)置示例,以說明如何配置 STM32 MCU 中的 MPU。如需詳細(xì)了解 MPU 寄存器,請參閱 Cortex 內(nèi)核編程手冊。

更多信息可以來這里獲取==>>電子技術(shù)應(yīng)用-AET<<