由于數(shù)字應(yīng)用和數(shù)據(jù)處理的迅速興起,計(jì)算能力需求呈爆炸式增長(zhǎng)。隨著越來(lái)越多地使用人工智能來(lái)應(yīng)對(duì)我們這個(gè)時(shí)代的主要挑戰(zhàn),例如氣候變化或糧食短缺,從現(xiàn)在開(kāi)始,計(jì)算需求預(yù)計(jì)每六個(gè)月就會(huì)翻一番。為了以可持續(xù)的方式處理呈指數(shù)級(jí)增長(zhǎng)的數(shù)據(jù)量,我們需要改進(jìn)的高性能半導(dǎo)體技術(shù)。為了實(shí)現(xiàn)這一目標(biāo),我們需要同時(shí)應(yīng)對(duì)五個(gè)挑戰(zhàn)。雖然世界上沒(méi)有一家公司可以單獨(dú)完成這一目標(biāo),但整個(gè)半導(dǎo)體生態(tài)系統(tǒng)的共同創(chuàng)新和協(xié)作將使摩爾定律得以延續(xù):這是 imec 未來(lái) 15 至 20 年雄心勃勃的路線圖的關(guān)鍵信息。

一次五面墻

縮放墻:純光刻支持的縮放正在放緩。由于微芯片和晶體管的單個(gè)結(jié)構(gòu)正在接近原子的大小,量子效應(yīng)開(kāi)始干擾微芯片的運(yùn)行,這變得越來(lái)越困難。

內(nèi)存墻:系統(tǒng)性能面臨內(nèi)核和內(nèi)存之間的數(shù)據(jù)路徑限制。事實(shí)上:內(nèi)存帶寬跟不上處理器性能。我們每秒有更多的觸發(fā)器而不是每秒千兆字節(jié)。

功率墻:將功率引入芯片并從芯片封裝中提取熱量變得越來(lái)越具有挑戰(zhàn)性,因此我們必須開(kāi)發(fā)改進(jìn)的功率傳輸和冷卻概念。

可持續(xù)性墻:半導(dǎo)體設(shè)備的制造導(dǎo)致環(huán)境足跡不斷增加,包括溫室氣體和水、自然資源和電力消耗。

成本墻:顯然,芯片制造成本可能會(huì)隨著復(fù)雜性的增加以及設(shè)計(jì)和工藝開(kāi)發(fā)成本的增加而激增。

拆墻

乍一看,戈登摩爾的預(yù)言看起來(lái)并不那么美好,他首先指出密集集成電路 (IC) 中的晶體管數(shù)量大約每?jī)赡攴环H绻覀冾B固地堅(jiān)持 Dennard 縮放和傳統(tǒng)的 Von Neumann 計(jì)算架構(gòu),這種預(yù)測(cè)尤其正確。

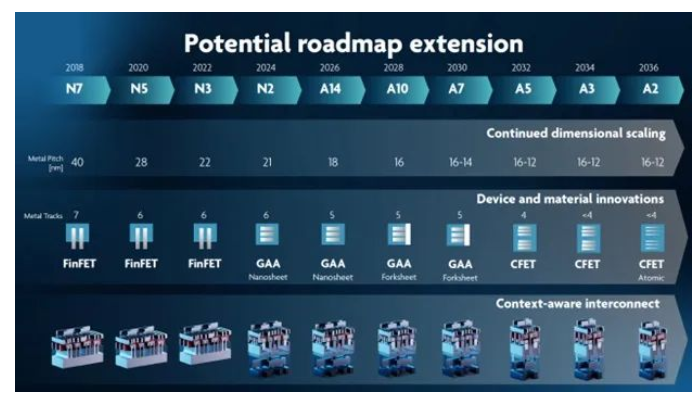

在其擴(kuò)展路線圖中,imec 為芯片技術(shù)的未來(lái)提出了一條替代路徑,在架構(gòu)、材料、晶體管的新基本結(jié)構(gòu)以及……范式轉(zhuǎn)變方面進(jìn)行了根本性的改變。到 2036 年,imec 路線圖將使我們從 7 nm 到 0.2 nm 或 2 ?ngstr?m,保持兩到兩年半的介紹速度。

首先,光刻技術(shù)的不斷進(jìn)步將是進(jìn)一步縮小尺寸的關(guān)鍵:傳統(tǒng)的光刻技術(shù)使用光,而如今,光的波長(zhǎng)大于圖案所需的精度。這就是引入極紫外 (EUV) 光刻的原因。它現(xiàn)在出現(xiàn)在越來(lái)越多的用于批量生產(chǎn)的功能性生產(chǎn)帶上。EUV 將把我們從5納米時(shí)代帶到2納米時(shí)代。為了變得更小,我們需要 EUV 的更新版本,High NA-EUV,以及更大的鏡頭。它們的直徑為 1 米,精度為 20 皮米。對(duì)于High NA EUV,ASML 正在開(kāi)發(fā)的第一個(gè)原型將于 2023 年面世。預(yù)計(jì)在 2025 年或 2026 年的某個(gè)時(shí)候投入大批量生產(chǎn)。為了降低在制造業(yè)中引入的風(fēng)險(xiǎn),imec 與阿斯麥正在緊密合作。

同時(shí)我們還需要晶體管架構(gòu)的創(chuàng)新。如今,幾乎所有芯片制造商都使用FinFET晶體管制造微芯片。然而,進(jìn)入 3nm 代時(shí),F(xiàn)inFET 受到量子干擾,導(dǎo)致微芯片運(yùn)行中斷。

接下來(lái)是環(huán)柵 (GAA)或納米片晶體管,由納米片堆疊而成,它將提供改進(jìn)的性能和改善的短溝道效應(yīng)。從 2 nm 開(kāi)始,這種架構(gòu)將是必不可少的。三星、英特爾和臺(tái)積電等主要芯片制造商已經(jīng)宣布,他們將在其 3 納米和/或 2 納米節(jié)點(diǎn)中引入 GAA 晶體管。forksheet 晶體管是 imec 的發(fā)明,甚至比 nanosheet 晶體管更密集,將 gate-all-around 概念擴(kuò)展到 1 nm 一代。forksheet 架構(gòu)在負(fù)溝道和正溝道之間引入了屏障,使溝道更加靠近。該架構(gòu)有望使單元尺寸縮小 20%。

通過(guò)將負(fù)溝道和正溝道相互疊加,可以實(shí)現(xiàn)進(jìn)一步的縮放,稱(chēng)為互補(bǔ) FET (CFET) 晶體管,是 GAA 的復(fù)雜垂直繼承者。它顯著提高了密度,但以增加工藝復(fù)雜性為代價(jià),尤其是接觸晶體管的源極和漏極。

隨著時(shí)間的推移,CFET 晶體管將采用原子厚度的新型超薄二維單層材料,如二硫化鎢 (WS2) 或鉬。該器件路線圖與光刻路線圖相結(jié)合,將帶我們進(jìn)入埃格斯特倫時(shí)代。

這些亞 2 納米晶體管的系統(tǒng)級(jí)還面臨著另外兩個(gè)挑戰(zhàn)。內(nèi)存帶寬跟不上 CPU 性能。處理器的運(yùn)行速度不能超過(guò)從內(nèi)存中獲取數(shù)據(jù)和指令的速度。要推倒這堵“內(nèi)存墻”,內(nèi)存必須離芯片更近。拆除內(nèi)存墻的一種有趣方法是 3D 片上系統(tǒng) (3D SOC) 集成,它超越了當(dāng)今流行的小芯片方法。按照這種異構(gòu)集成方法,系統(tǒng)被劃分為獨(dú)立的芯片,這些芯片在三維中同時(shí)設(shè)計(jì)和互連。例如,它將允許在核心邏輯設(shè)備上為 level-1-Cash 堆疊一個(gè) SRAM 內(nèi)存層,從而實(shí)現(xiàn)內(nèi)存與邏輯的快速交互。

關(guān)于與系統(tǒng)相關(guān)的挑戰(zhàn),為芯片提供足夠的功率并散發(fā)熱量變得更加困難。然而,一個(gè)解決方案就在眼前:配電現(xiàn)在從晶圓頂部穿過(guò)十多個(gè)金屬層到達(dá)晶體管。Imec 目前正在研究晶圓背面的解決方案。我們會(huì)將電源軌沉入晶圓,并使用更寬、電阻更小的材料中的納米硅通孔將它們連接到背面。這種方法將電力傳輸網(wǎng)絡(luò)與信號(hào)網(wǎng)絡(luò)分離,提高整體電力傳輸性能,減少路由擁塞,并最終允許進(jìn)一步標(biāo)準(zhǔn)單元高度縮放。

最后,半導(dǎo)體制造是有代價(jià)的。它需要大量的能源和水,并產(chǎn)生危險(xiǎn)廢物。但整個(gè)供應(yīng)鏈需要致力于解決這個(gè)問(wèn)題,而生態(tài)系統(tǒng)方法將是必不可少的。去年,imec 啟動(dòng)了可持續(xù)半導(dǎo)體技術(shù)和系統(tǒng) (SSTS) 研究計(jì)劃,該計(jì)劃匯集了半導(dǎo)體價(jià)值鏈的利益相關(guān)者——從亞馬遜、蘋(píng)果和微軟等大型系統(tǒng)公司到供應(yīng)商,包括 ASM、ASML、KURITA、SCREEN、和東京電子。目標(biāo)是減少整個(gè)行業(yè)的碳足跡。該計(jì)劃評(píng)估新技術(shù)對(duì)環(huán)境的影響,確定影響大的問(wèn)題,并在技術(shù)開(kāi)發(fā)的早期定義更環(huán)保的半導(dǎo)體制造解決方案。

模式轉(zhuǎn)變

從長(zhǎng)遠(yuǎn)來(lái)看,馮諾依曼架構(gòu)需要徹底改革。馮·諾依曼教授將數(shù)字計(jì)算機(jī)視為一個(gè)具有輸入、中央處理器和輸出的系統(tǒng)。但我們需要向特定領(lǐng)域和應(yīng)用程序相關(guān)的架構(gòu)發(fā)展,大規(guī)模并行化可與人腦的工作方式相媲美。這意味著 CPU 將扮演更小的角色,有利于為特定工作負(fù)載定制電路。

這種范式轉(zhuǎn)變,加上前方的障礙,標(biāo)志著半導(dǎo)體行業(yè)有趣時(shí)代的開(kāi)始。我們需要在整個(gè)半導(dǎo)體生態(tài)系統(tǒng)中進(jìn)行共同創(chuàng)新和協(xié)作:代工廠、IDM、無(wú)晶圓廠、fab-lite、設(shè)備和材料供應(yīng)商。不僅僅是為了滿(mǎn)足摩爾定律,而是因?yàn)榘雽?dǎo)體是高性能深度技術(shù)應(yīng)用的核心,可以在應(yīng)對(duì)氣候變化、可持續(xù)交通、空氣污染和食物短缺等我們這個(gè)時(shí)代的挑戰(zhàn)方面取得有影響力的進(jìn)展. 賭注很高。

更多信息可以來(lái)這里獲取==>>電子技術(shù)應(yīng)用-AET<<