納芯微全新推出GaN相關(guān)產(chǎn)品,包含GaN驅(qū)動(dòng)NSD2621與集成化的Power Stage產(chǎn)品NSG65N15K,均可廣泛適用于快充、儲(chǔ)能、服務(wù)器電源等多種GaN應(yīng)用場(chǎng)景。

其中,NSD2621是一顆高壓半橋柵極驅(qū)動(dòng)芯片,專(zhuān)門(mén)用于驅(qū)動(dòng)E?mode(增強(qiáng)型)GaN 開(kāi)關(guān)管;NSG65N15K是一顆集成化的Power Stage產(chǎn)品,內(nèi)部集成了高壓半橋驅(qū)動(dòng)器和兩顆650V耐壓的GaN開(kāi)關(guān)管。

NSD2621產(chǎn)品特性:

01. SW引腳耐壓±700V

02. 峰值驅(qū)動(dòng)電流2A/-4A

03. 驅(qū)動(dòng)輸出集成內(nèi)部穩(wěn)壓器,驅(qū)動(dòng)電壓5V/5.5V/6V可選

04. 傳輸延時(shí)典型值30ns,上下管驅(qū)動(dòng)傳輸延時(shí)匹配低于10ns

05. 內(nèi)部可調(diào)死區(qū)時(shí)間20ns~100ns

06. SW允許共模瞬變高達(dá)150V/ns

07. 獨(dú)立的SGND和PGND引腳

08. 集成欠壓保護(hù)和過(guò)溫保護(hù)

09. 工作溫度范圍-40°C~125°C

10. QFN15 4*4mm封裝

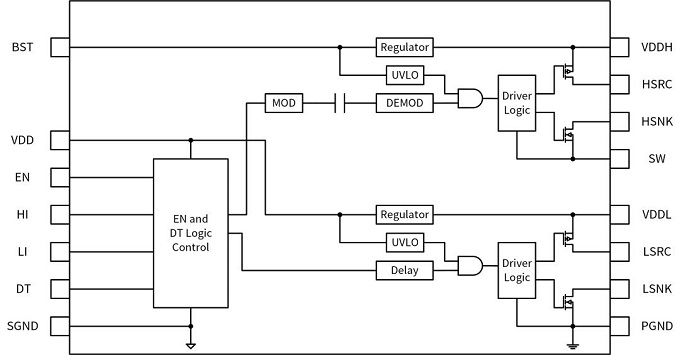

NSD2621功能框圖

1. NSD2621將隔離技術(shù)應(yīng)用于高壓半橋驅(qū)動(dòng),解決了GaN應(yīng)用橋臂中點(diǎn)SW引腳的共模瞬變和負(fù)壓尖峰問(wèn)題。

在GaN應(yīng)用中,為了減小開(kāi)關(guān)損耗,其開(kāi)關(guān)速度遠(yuǎn)高于傳統(tǒng)的Si MOSFET, 橋臂中點(diǎn)的dv/dt達(dá)到了50V/ns甚至更高,這對(duì)驅(qū)動(dòng)芯片SW引腳的共模瞬變抗擾度提出了極高的要求。同時(shí),高速開(kāi)關(guān)導(dǎo)致的di/dt與寄生電感會(huì)在SW引腳產(chǎn)生瞬態(tài)負(fù)壓尖峰,導(dǎo)致驅(qū)動(dòng)芯片發(fā)生閂鎖甚至損壞。

NSD2621的上管驅(qū)動(dòng)采用隔離技術(shù)進(jìn)行設(shè)計(jì),共模瞬變抗擾度高達(dá)150V/ns,并且可以耐受700V的負(fù)壓,有效提升了系統(tǒng)的可靠性。

2. NSD2621內(nèi)部集成穩(wěn)壓器,有利于保持柵極驅(qū)動(dòng)信號(hào)幅值穩(wěn)定,保護(hù)GaN開(kāi)關(guān)管柵級(jí)免受過(guò)壓應(yīng)力的影響。

與傳統(tǒng)的Si MOSFET器件不同,E-mode GaN器件的柵源電壓要求極為嚴(yán)格,一般耐壓最大值不超過(guò)7V。在開(kāi)關(guān)電源中由于系統(tǒng)噪聲的影響,驅(qū)動(dòng)芯片VDD或者BST引腳容易引入高頻干擾,會(huì)引起柵極驅(qū)動(dòng)電壓的過(guò)沖,從而導(dǎo)致GaN開(kāi)關(guān)管損壞。

NSD2621上下管的驅(qū)動(dòng)輸出都集成了內(nèi)部穩(wěn)壓器LDO,可以有效抑制VDD或BST引入的高頻干擾,避免損壞GaN開(kāi)關(guān)管。此外NSD2621可以靈活地選擇6V/5.5V/5V不同驅(qū)動(dòng)電壓版本,適用于各類(lèi)品牌的GaN開(kāi)關(guān)管器件。

3. NSD2621超短傳輸延時(shí)有利于減小GaN死區(qū)損耗,并且內(nèi)置可調(diào)死區(qū)時(shí)間功能,可有效避免發(fā)生橋臂直通。

GaN器件可以反向?qū)ǎ浞聪驅(qū)ㄌ匦源媪似胀∕OSFET體二極管的續(xù)流作用,但在負(fù)載電流較大時(shí)其較高的反向?qū)▔航禃?huì)造成較大損耗,降低了系統(tǒng)效率。為了減小GaN反向?qū)〒p耗,應(yīng)設(shè)置盡可能小的死區(qū)時(shí)間。死區(qū)時(shí)間的設(shè)置除了與電源的拓?fù)浣Y(jié)構(gòu)、控制方式有關(guān),還受到驅(qū)動(dòng)芯片傳輸延時(shí)的限制。

傳統(tǒng)的高壓半橋驅(qū)動(dòng)芯片的上管驅(qū)動(dòng)需要采用電平移位設(shè)計(jì),為減小功耗多采用脈沖鎖存式電平轉(zhuǎn)換器,造成傳輸延時(shí)較長(zhǎng),無(wú)法滿(mǎn)足GaN 應(yīng)用的需求。NSD2621上管驅(qū)動(dòng)采用納芯微擅長(zhǎng)的隔離技術(shù)進(jìn)行設(shè)計(jì),傳輸延時(shí)典型值僅30ns,并且上下管驅(qū)動(dòng)的傳輸延時(shí)匹配在10ns以?xún)?nèi),能夠?qū)崿F(xiàn)對(duì)GaN開(kāi)關(guān)管設(shè)置幾十納秒以?xún)?nèi)的死區(qū)時(shí)間。同時(shí),NSD2621內(nèi)置20ns~100ns可調(diào)的硬件死區(qū)時(shí)間,可以有效避免發(fā)生橋臂直通的情況。

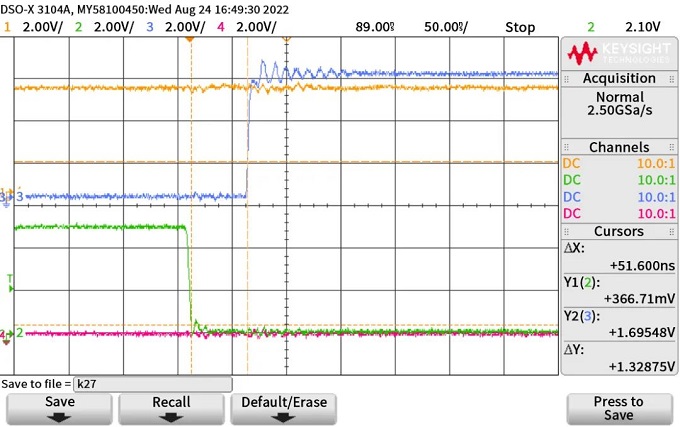

NSD2621內(nèi)置死區(qū)時(shí)間測(cè)試波形

如上圖所示,CH1為上管驅(qū)動(dòng)輸入 ,CH2為下管驅(qū)動(dòng)輸入,CH3為上管驅(qū)動(dòng)輸出,CH4為下管驅(qū)動(dòng)輸出。一開(kāi)始當(dāng)上管和下管驅(qū)動(dòng)輸入都為高電平時(shí),為避免橋臂直通,上下管驅(qū)動(dòng)輸出都為低電平;當(dāng)下管驅(qū)動(dòng)輸入變?yōu)榈碗娖剑?jīng)過(guò)30ns的傳輸延時(shí)和內(nèi)置20ns的死區(qū)時(shí)間后,上管驅(qū)動(dòng)輸出變?yōu)楦唠娖健?/p>

NSG65N15K產(chǎn)品特性

為進(jìn)一步發(fā)揮GaN高頻、高速的特性?xún)?yōu)勢(shì),納芯微同時(shí)推出了集成化的Power Stage產(chǎn)品NSG65N15K,內(nèi)部集成了半橋驅(qū)動(dòng)器NSD2621和兩顆耐壓650V、導(dǎo)阻電阻150mΩ的GaN開(kāi)關(guān)管,工作電流可達(dá)20A。NSG65N15K內(nèi)部還集成了自舉二極管,并且內(nèi)置可調(diào)死區(qū)時(shí)間、欠壓保護(hù)、過(guò)溫保護(hù)功能,可以用于圖騰柱PFC、ACF和LLC等半橋或全橋拓?fù)洹?/p>

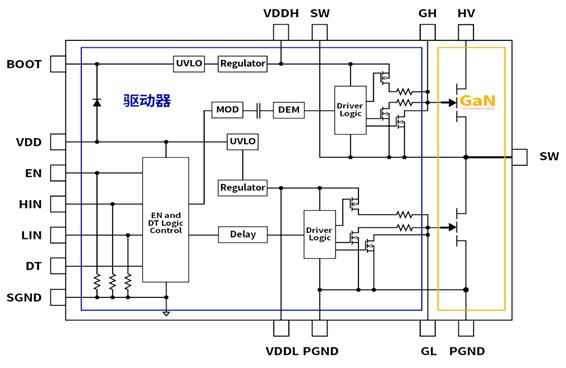

NSG65N15K功能框圖

1. NSG65N15K用一顆器件取代驅(qū)動(dòng)器和兩顆開(kāi)關(guān)管組成的半橋,有效減少元件數(shù)量和布板面積。

NSG65N15K是9*9mm的QFN封裝,相比傳統(tǒng)分立方案的兩顆5*6mm DFN封裝的GaN開(kāi)關(guān)管加上一顆4*4mm QFN封裝的高壓半橋驅(qū)動(dòng),加上外圍元件,總布板面積可以減小40%以上,從而有效提高電源的功率密度。同時(shí),NSG65N15K的走線更方便PCB布局,有利于實(shí)現(xiàn)簡(jiǎn)潔快速的方案設(shè)計(jì)。

2. NSG65N15K的合封設(shè)計(jì)有助于減小驅(qū)動(dòng)和開(kāi)關(guān)管之間的寄生電感,簡(jiǎn)化系統(tǒng)設(shè)計(jì)并提高可靠性。

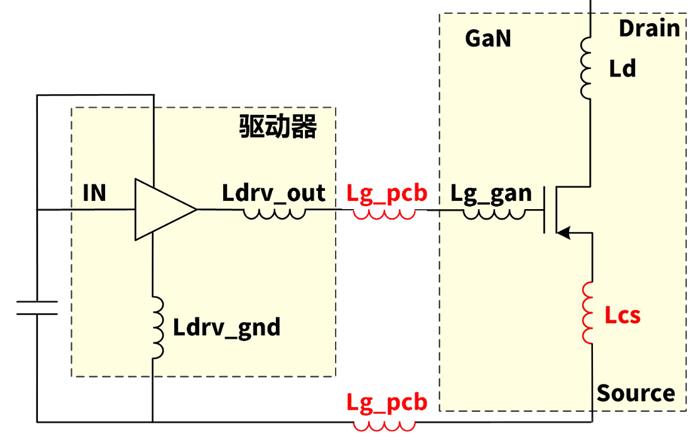

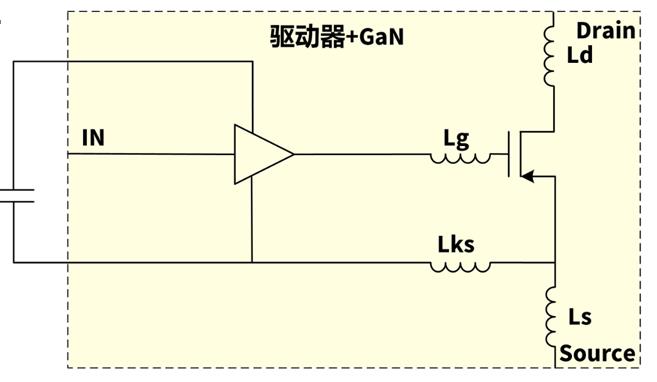

如下圖所示,傳統(tǒng)的分立器件方案,會(huì)引入由于PCB走線造成的柵極環(huán)路電感Lg_pcb和由于GaN內(nèi)部打線造成的共源極電感Lcs。

傳統(tǒng)分立方案引入寄生電感

其中,柵極環(huán)路電感Lg_pcb會(huì)在柵極電壓開(kāi)通或關(guān)斷過(guò)程產(chǎn)生振鈴,如果振鈴超出GaN的柵源電壓范圍,容易造成柵極擊穿;并且在上管開(kāi)通過(guò)程中,高dv/dt產(chǎn)生的米勒電流會(huì)在下管的Lg_pcb上產(chǎn)生正向壓降,有可能造成GaN的柵極電壓大于開(kāi)啟電壓,從而誤導(dǎo)通。而共源極電感Lcs造成的影響,主要是會(huì)限制GaN電流的di/dt,增加額外的開(kāi)關(guān)損耗;此外,在GaN開(kāi)通過(guò)程電流增大,由于di/dt會(huì)在Lcs上產(chǎn)生正向壓降,降低了GaN的實(shí)際柵極電壓,增大了開(kāi)通損耗。

NSG65N15K減小雜散電感的影響

如上圖所示,NSG65N15K通過(guò)將驅(qū)動(dòng)器和GaN合封在一起,消除了共源極電感Lcs,并且將柵極回路電感Lg也降到最小,避免了雜散電感的影響,可以有效地提高系統(tǒng)效率與可靠性。