嵌入式FPGA IP正在發(fā)現(xiàn)更廣闊的用武之地

2023-11-30

作者:Achronix Semiconductor中國區(qū)總經(jīng)理,郭道正

來源:Achronix半導體公司

在日前落幕的“中國集成電路設計業(yè)2023年會暨廣州集成電路產(chǎn)業(yè)創(chuàng)新發(fā)展高峰論壇(ICCAD 2023)”上,Achronix的Speedcore?嵌入式FPGA硅知識產(chǎn)權(quán)(eFPGA IP)受到了廣泛關注,預約會議、專程前往或者駐足詢問的芯片設計業(yè)人士的數(shù)量超過了往屆,表明了越來越多的國內(nèi)開發(fā)者正在考慮為其ASIC或SoC設計添加高性能eFPGA邏輯陣列。

眾多潛在用戶的需求,反映了當前各行各業(yè)都在加速導入智能化技術,并利用eFPGA來在其ASIC或SoC中添加硬件數(shù)據(jù)處理加速功能,并為不斷演進的算法或者標準保留可編程性。Speedcore eFPGA IP包括了查找表、存儲器、數(shù)字信號處理器(DSP)和機器學習處理器(MLP)等構(gòu)建模塊。它們都采用了模組化的結(jié)構(gòu)設計,以支持客戶根據(jù)其客制化終端系統(tǒng)的需求,來量身定制相應的資源組合。

Achronix的Speedcore IP以GDSII格式提供,同時提供相應的文檔,以支持設計師將Speedcore eFPGA實例集成到其特有的ASIC之中。Achronix還提供配套的ACE設計工具,用于編譯針對Speedcore eFPGA的設計。目前,Speedcore eFPGA IP已被全球數(shù)十家領先的科技企業(yè)采用,總的出貨量超過了1500萬。

簡要功能介紹

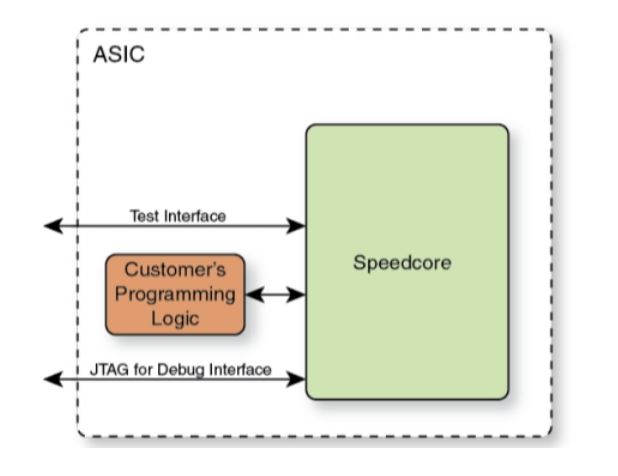

由于Speedcore eFPGA是一款嵌入式IP,因此它被設計為整個ASIC的一個單元組件,被ASIC的其他完全定制的單元模組所包圍(見下圖)。Speedcore eFPGA包括以下功能:

·可編程內(nèi)核邏輯陣列,具有客戶自定義的功能

·內(nèi)核I/O環(huán)

·FPGA配置單元(FCU)

·配置存儲器(CMEM)

·用于調(diào)試和編程的接口

·用于測試的接口(DFT)

核心資源介紹

通過選擇下列每種資源的數(shù)量,就可以定義一個定制Speedcore eFPGA IP的功能:

·邏輯 - 6輸入查找表(LUT),加上集成的快速加法器

·邏輯RAM - 兩種選擇:

·用于LRAM2k的每個存儲器單元的容量最多可達2Kb,其中包括與MLP緊耦合的存儲器

·用于LRAM4k的每個存儲器單元的容量最多可達4Kb

·Block RAM - 兩種選擇:

·用于BRAM20k的每個存儲器單元的容量最多可達20Kb

·用于BRAM72k的每個存儲器單元的容量最多可達72Kb,包括與MLP緊耦合的存儲器

·DSP64 - 每個單元模塊有一個18 x 27乘法器、64位累加器和27位預加法器

·MLP - 機器學習處理器(MLP)模塊,包含乘法器、加法器、累加器和緊耦合存儲器(包括BRAM72k和LRAM2k)

交付與應用價值

由于Achronix采用了根據(jù)客戶需求來定制GDSII的商業(yè)模式,每個Speedcore eFPGA實例的資源模塊的數(shù)量和組合都是基于客戶需求來搭配提供。Achronix的Speedcore eFPGA IP可用于臺積電(TSMC)的16FF+、16FFC、12FFC、7nm、5nm和3nm工藝技術節(jié)點,也可以移植到其他工藝節(jié)點上。

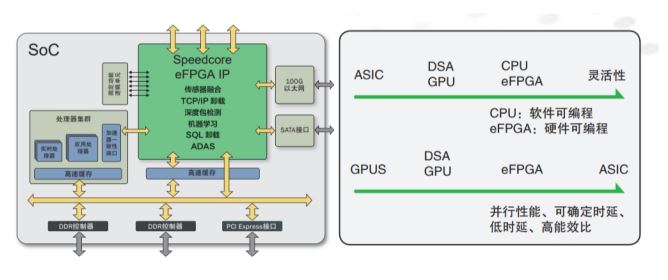

在ASIC或者SoC中嵌入Speedcore eFPGA將帶來諸多好處,與一款獨立的FPGA芯片相比,Speedcore eFPGA IP提供了以下優(yōu)點:

·降低功耗多達75%

·節(jié)省90%的成本

·延遲縮短到1/100,同時帶寬提高了10倍。

因此,Speedcore eFPGA具有極高的應用價值。

開發(fā)與編程

Achronix是唯一一家可以同時大批量生產(chǎn)并交付eFPGA IP和獨立FPGA芯片的公司,而且它們都采用同一套ACE開發(fā)工具來支持。設計人員可以100%確信Speedcore eFPGA IP將會正常工作,因為它在Achronix的Speedster系列獨立FPGA 芯片中已得到了全面的驗證,并且經(jīng)過了大量的流片驗證。

由于Speedcore eFPGA IP采用的是與Achronix的獨立FPGA芯片和搭載Achronix Speedster7t FPGA芯片的VectorPath加速卡相同的工具,開發(fā)人員可以先在這些獨立FPGA芯片或者加速卡上完成設計,然后再移植到Speedcore eFPGA上。客戶可以選擇以下所列配置接口中的一項或多項組合來進行編程:

·JTAG

·并行CPU(x1、x8、x16、x32、x128數(shù)據(jù)寬度模式)

·串行閃存(1個或4個閃存器件)

·128位AXI總線

總結(jié)與展望

Achronix的Speedcore eFPGA IP保持了高端FPGA的性能,最高運行頻率可達750MHz,典型的運行頻率也可以達到300MHz-500MHz,可以為ASIC或者SoC提供高性能硬件加速,是諸多智能化應用和邊緣計算的理想選擇,因而被領先科技企業(yè)選擇用于通信基礎設備、網(wǎng)絡加速、智能駕駛和金融科技等多種應用中。

從我們在ICCAD 2023上與客戶的交流來看,一些領先的國內(nèi)系統(tǒng)公司和芯片設計企業(yè)已經(jīng)認識到eFPGA的優(yōu)點與價值,并進一步在探討與Achronix進行基于eFPGA的chiplet等新的合作模式。因此,我們可以展望在未來幾年中,集成了Speedcore等eFPGA的ASIC或者SoC將是智能化和高速網(wǎng)聯(lián)等領域內(nèi)芯片設計企業(yè)的一條重要的創(chuàng)新之道。

更多精彩內(nèi)容歡迎點擊==>>電子技術應用-AET<<