8月14日消息,美國(guó)半導(dǎo)體初創(chuàng)公司Akeana宣布推出一系列RISC-V CPU內(nèi)核IP,以期與Arm進(jìn)行全面的競(jìng)爭(zhēng)。

據(jù)介紹,Akeana的RISC-V CPU覆蓋了從微控制器到數(shù)據(jù)中心的整個(gè)性能需求范圍,并且期其多個(gè)系列的RISC-V內(nèi)核、內(nèi)存管理單元、中斷控制器和互連都來(lái)自單一的System Verilog數(shù)據(jù)庫(kù),包括用于AI加速器的矩陣引擎和矢量引擎。

“我們正在通過(guò)我們認(rèn)為是唯一具有匹敵Arm Neoverse內(nèi)核的RISC-V處理器從‘隱身’中走出來(lái),”Akeana首席執(zhí)行官Rabin Sugumar表示:“我們確實(shí)認(rèn)為這是一個(gè)行業(yè)突破,我們認(rèn)為以前沒(méi)有用單一數(shù)據(jù)庫(kù)的這一系列核心做過(guò)。”

在過(guò)去三年中,Akeana公司從經(jīng)驗(yàn)豐富的芯片投資者M(jìn)ayfield和Kleiner Perkins那里籌集了1億美元,擁有150名員工,一半在美國(guó),一半在亞洲。

“我們是一家純粹的知識(shí)產(chǎn)權(quán)公司,”Sugumar說(shuō)。“這些創(chuàng)新是一套非常廣泛的知識(shí)產(chǎn)權(quán),具有低運(yùn)營(yíng)支出,因此我們能夠在低運(yùn)營(yíng)支出下維持開(kāi)發(fā),從而在較小的市場(chǎng)份額下取得成功。”

“對(duì)于Arm或MIPS內(nèi)核來(lái)說(shuō),開(kāi)發(fā)商需要為每個(gè)核心都有一個(gè)單獨(dú)的團(tuán)隊(duì),所以需要有很多的團(tuán)隊(duì)。而我們所有的內(nèi)核都來(lái)自一個(gè)高度可配置的數(shù)據(jù)庫(kù),從小型微控制器到Arm Neoverse V2級(jí)別的內(nèi)核,都有關(guān)于如何做到這一點(diǎn)的創(chuàng)新想法。如果出現(xiàn)錯(cuò)誤或時(shí)間問(wèn)題,我們會(huì)一次修復(fù)。”

不過(guò),編譯器是獨(dú)立的,不是由數(shù)據(jù)庫(kù)生成的,這與Tensilica或Codasip所采用的方法不同。但是 gcc-03 開(kāi)源編譯器已經(jīng)足夠好了,Sugumar 說(shuō)。

“因此,我們可以用一個(gè)小團(tuán)隊(duì)覆蓋Arm CPU所能夠覆蓋的整個(gè)范圍,”他說(shuō)。這種可配置性是使其運(yùn)營(yíng)支出低的原因,但客戶不想要可配置的數(shù)據(jù)庫(kù),他們不知道該如何處理它。

目前,Akeana已經(jīng)推出了三個(gè)系列的RISC-V內(nèi)核,并且單個(gè)內(nèi)核可以針對(duì)特定應(yīng)用進(jìn)行定制。具體來(lái)說(shuō)包括:

Akeana 100 系列:一系列高度可配置的處理器,具有 32 位 RISC-V 單線程內(nèi)核,支持從嵌入式微控制器到邊緣網(wǎng)關(guān)和個(gè)人計(jì)算設(shè)備的應(yīng)用。

Akeana 1000 系列處理器系列包括 64 位 RISC-V 內(nèi)核和 MMU,可支持豐富的操作系統(tǒng),同時(shí)保持低功耗并需要較小的芯片面積。這些處理器支持有序或無(wú)序流水線、多線程、向量擴(kuò)展、虛擬機(jī)管理程序擴(kuò)展和其他擴(kuò)展,這些擴(kuò)展是最近和即將推出的 RISC-V 配置文件的一部分,以及可選的 AI 計(jì)算擴(kuò)展,每個(gè)周期執(zhí)行四個(gè)線程。

Akeana 5000 系列為筆記本電腦、數(shù)據(jù)中心和云基礎(chǔ)設(shè)施提供更高性能的 64 位 12 級(jí)無(wú)序處理器內(nèi)核,配備 512 位矢量引擎和每周期 4 個(gè)線程。這些處理器與 Akeana 1000 系列兼容,但單線程性能比 Arm Cortex-X 系列高得多。

Sugumar說(shuō),這三個(gè)系列共有10個(gè)核心,可以在幾周內(nèi)進(jìn)行修改,并將其包含在其他核心的數(shù)據(jù)庫(kù)中。

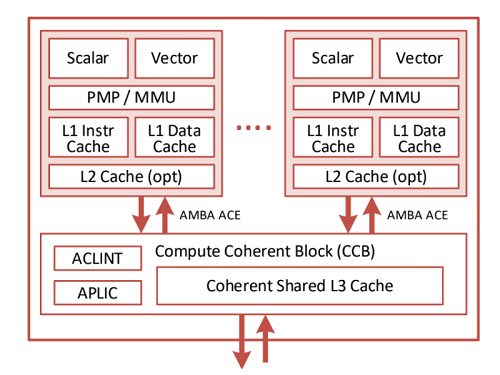

此外還有處理器系統(tǒng) IP:創(chuàng)建處理器 SoC 所需的 IP 塊集合,包括相干集群緩存、I/O MMU 和中斷控制器 IP。Akeana還提供可擴(kuò)展Mesh和Coherence Hub IP(與AMBA CHI兼容),為數(shù)據(jù)中心和其他用例構(gòu)建大型相干計(jì)算子系統(tǒng)。

AI Matrix 計(jì)算引擎卸載了 Matrix Multiply 運(yùn)算以實(shí)現(xiàn) AI 加速。大小可配置,支持各種數(shù)據(jù)類型,并且可以像核心一樣連接到連貫的集群緩存塊,以實(shí)現(xiàn)最佳數(shù)據(jù)共享。

“我們有低端核心,但高端核心是優(yōu)勢(shì)所在,差異化很重要,”Akeana銷售與開(kāi)發(fā)副總裁Bruno Putman表示:“目前,真正高端核心(相當(dāng)于Arm Neoverse V2)的RISC-V CPU市場(chǎng)還不存在,但如果可以與Arm Neoverse N1和N2競(jìng)爭(zhēng)也更有趣。”

重點(diǎn)是具有 CHI 和網(wǎng)狀互連的內(nèi)核集群,用于片上系統(tǒng) (SoC) 設(shè)計(jì),以提供性能,而不是小芯片。“現(xiàn)在我們正在做 IP,所以如果客戶來(lái)找我們并想要小芯片,我們會(huì)考慮這一點(diǎn),但這并沒(méi)有出現(xiàn),但我們確實(shí)已經(jīng)為小芯片協(xié)議集成了 UCIe協(xié)議,”Sugumar 說(shuō)。

目前,該公司為使用 Akeana 版本的 Qemu 模擬器的客戶提供三種 IP 選擇。還有Cadence Palladium 仿真器,可以在 FPGA 上測(cè)試相關(guān)內(nèi)核。

Sugumar說(shuō):“我們預(yù)計(jì)今年晚些時(shí)候或明年將進(jìn)行流片,用于可穿戴設(shè)備的小型Android集群,需要性能核心和多核網(wǎng)絡(luò)集群的網(wǎng)絡(luò)應(yīng)用,以及AI,其中具有矢量擴(kuò)展的按順序核心充當(dāng)AI引擎。”此外,該公司還開(kāi)始開(kāi)發(fā)可以通過(guò)汽車認(rèn)證的IP。