MathWorks 和 Altera 利用 AI 推動 5G 和 6G 無線系統(tǒng)的更快發(fā)展

2025-03-09

來源:MathWorks

中國 北京,2025 年 3 月 5 日 —— 全球領(lǐng)先的數(shù)學(xué)計(jì)算軟件開發(fā)商 MathWorks 今天宣布,與英特爾旗下公司 Altera?將通力協(xié)作,通過支持無線系統(tǒng)工程師使用基于 AI 的自編碼器來壓縮信道狀態(tài)信息(CSI)數(shù)據(jù)并顯著降低前傳流量和帶寬要求,共同加速 Altera FPGA 的無線開發(fā)。從事 5G 和 6G 無線通信系統(tǒng)的工程師現(xiàn)可以在降低成本的同時(shí),確保用戶數(shù)據(jù)的完整性,并維持無線通信系統(tǒng)的可靠性和性能標(biāo)準(zhǔn)。

Altera 垂直市場副總裁兼總經(jīng)理 Mike Fitton 表示:“MathWorks 和 Altera 的協(xié)作使各個(gè)組織能夠在廣泛的 5G 和 6G 無線通信應(yīng)用中利用 AI 的強(qiáng)大功能,這些應(yīng)用涵蓋 5G RAN 和高級駕駛輔助系統(tǒng)(ADAS)等。通過使用我們的 FPGA AI 套件和 MathWorks 軟件,開發(fā)人員可以簡化從算法設(shè)計(jì)到硬件實(shí)現(xiàn)的工作流,確保他們基于 AI 的無線系統(tǒng)滿足現(xiàn)代應(yīng)用的嚴(yán)格要求。”

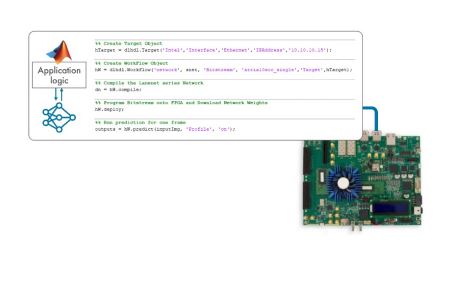

MathWorks 提供全面的工具套件,可以增強(qiáng) AI 和無線開發(fā),特別適用于 Altera FPGA。Deep Learning HDL Toolbox? 專門針對工程師在 FPGA 硬件上實(shí)現(xiàn)深度學(xué)習(xí)網(wǎng)絡(luò)的需求進(jìn)行了開發(fā)。此創(chuàng)新工具箱可利用 HDL Coder? 的功能,使用戶能夠自定義、構(gòu)建和部署高效、高性能的深度學(xué)習(xí)處理器 IP 核。這一進(jìn)步通過支持標(biāo)準(zhǔn)網(wǎng)絡(luò)和層,顯著增強(qiáng)了無線應(yīng)用的性能和靈活性。

MathWorks 首席產(chǎn)品經(jīng)理 Houman Zarrinkoub 表示:“基于 AI 的壓縮是電信行業(yè)的一項(xiàng)強(qiáng)大技術(shù)。MathWorks 軟件為 AI 和無線發(fā)展奠定了堅(jiān)實(shí)的基礎(chǔ)。通過將我們的工具與 Altera 的 FPGA 技術(shù)相集成,無線工程師可以高效地創(chuàng)建高性能 AI 應(yīng)用以及高級 5G 和 6G 無線系統(tǒng)。”

FPGA AI 套件使用 OpenVINO 工具包,利用常見的行業(yè)框架中預(yù)訓(xùn)練的 AI 模型,在 Altera FPGA 上提供按鈕式自定義 AI 推斷加速器 IP 生成。它進(jìn)一步幫助 FPGA 開發(fā)人員使用同類最佳 Quartus? Prime 軟件 FPGA 流程,將 AI 推斷加速器 IP 無縫集成到 FPGA 設(shè)計(jì)中。Deep Learning Toolbox 和 OpenVINO 工具包的結(jié)合使用,為開發(fā)人員優(yōu)化 Altera FPGA 上的 AI 推斷開辟了一條簡化路徑。

更多精彩內(nèi)容歡迎點(diǎn)擊==>>電子技術(shù)應(yīng)用-AET<<