1 概述

Σ-Δ調(diào)制是目前國際上的A/D轉(zhuǎn)換器設(shè)計中很受歡迎的一種技術(shù),與傳統(tǒng)的Nyquist頻率采樣的A/D轉(zhuǎn)換器工作原理有所不同,采用的是過采樣和低位量化結(jié)合的方法。其中,過采樣技術(shù)在模/數(shù)混合電路中的應(yīng)用,能夠避免傳統(tǒng)A/D或D/A轉(zhuǎn)換方法實現(xiàn)中遇到的諸多困難,尤其是在對低頻信號要求高分辨率的應(yīng)用領(lǐng)域,傳統(tǒng)轉(zhuǎn)換方法需要較高精度的模擬結(jié)構(gòu)(模擬電阻、電容等),從而使整個A/D轉(zhuǎn)換器的成本很高。Σ-ΔADC能夠避免使用高精度模擬電路,將噪聲推向高頻,具有分辨率高,量化結(jié)構(gòu)簡單等優(yōu)點。由于電磁環(huán)境日益惡化,對接收機的動態(tài)范圍要求越來越高,跳頻、擴頻等寬帶信號的應(yīng)用又要求使用寬帶測量設(shè)備,這些都對ADC的分辨率和速度提出了更高的要求。

調(diào)制器(Modulator)屬于Σ-ΔADC電路中的模擬電路部分,它的結(jié)構(gòu)選擇和電路參數(shù)設(shè)計都極大地影響著整個ADC的信噪比(SNR)等性能指標(biāo)。在Σ-Δ調(diào)制器中,使用了過采樣、噪聲成形等關(guān)鍵技術(shù)。這些技術(shù)還使它另外具有一系列固有的優(yōu)點,如易于與數(shù)字信號處理系統(tǒng)單片集成,無須采樣保持電路,對輸入端抗混迭濾波器要求很低等。下

面先討論過采樣與MASH噪聲成形的主要單元分析,最后針對DAC失真誤差,設(shè)計并仿真了一種數(shù)字誤差校正技術(shù)。

2 基本原理與技術(shù)

2.1 Σ-ΔADC基本原理及調(diào)制器的組成

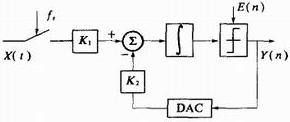

Σ-ΔADC由兩部分組成:調(diào)制器和數(shù)字抽取濾波器。其中調(diào)制器的工作原理是采用遠(yuǎn)遠(yuǎn)大于Nyquist頻率的時鐘對輸入模擬信號進(jìn)行”過采樣”,采樣頻率與Nyquist頻率之比定義為過采樣率M,是調(diào)制器的重要結(jié)構(gòu)參數(shù)之一。由于采樣頻率很高,則無需傳統(tǒng)的PCMADC中的保持電路。采樣后的信號與前一時刻的采樣信號相比較,對其差值做出低位量化,輸出低位碼流,并根據(jù)量化器的輸出決定返回+Δ或-Δ反饋信號。調(diào)制器的基本結(jié)構(gòu)如圖1所示,主要由采樣環(huán)節(jié)、積分器、量化器以及D/A反饋組成,其中fs表示采樣時鐘頻率,K1,K2分別表示輸入信號和反饋信號的增益系數(shù)。

圖1 Σ-Δ調(diào)制器基本結(jié)構(gòu)

習(xí)慣上,定義調(diào)制器中含有的積分器個數(shù)為調(diào)制器的階數(shù)L,量化器的個數(shù)為級數(shù)。對調(diào)制器的線性模型做離散域的z變換分析,并將量化誤差模型化為噪聲信號,可以推導(dǎo)出輸出信號Y對輸入信號X與量化誤差E的傳遞函數(shù),在有效信號頻率內(nèi),輸入信號保持不變而噪聲信號被差分衰減,即

Y(z)=z-LX(z)+(1-z-1)LE(z) (1)

通常,對調(diào)制器性能評測的重要參數(shù)之一是信噪比SNR,即信號功率與噪聲功率之比

(2)

(2)

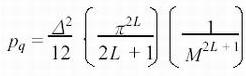

這里ps為有效信號的功率,對正弦信號來說,ps= ,A為幅度;pq是信號頻帶內(nèi)總的量化噪聲功率,由E(z)的傳遞函數(shù)在有效信號頻帶內(nèi)積分得到

,A為幅度;pq是信號頻帶內(nèi)總的量化噪聲功率,由E(z)的傳遞函數(shù)在有效信號頻帶內(nèi)積分得到

(3)

(3)

從上式可以看出,分別提高M(jìn)或L都能帶來SNR的提高。但當(dāng)信號頻率達(dá)到幾十MHz以上的高頻范圍后,M的提高勢必會受到現(xiàn)有工藝,以及功耗等制約。目前,更多的研究改善SNR的方法是針對L的提高。

從調(diào)制器內(nèi)在穩(wěn)定性考慮,針對高階調(diào)制器(L≥3),又有兩種結(jié)構(gòu)上的取向,即單級single-loop結(jié)構(gòu)和多級級聯(lián)的MASH結(jié)構(gòu)。

2.2 過采樣及MASH(多級噪聲成形)技術(shù)

本文中使用記號fN來表示Nyquist調(diào)制器工作時的采樣率,而它與基帶信號最高頻率fB的關(guān)系工程上一般為fN≈2.2fB~2.5fB。所謂過采樣,就是指采樣速度fs遠(yuǎn)大于fN。這里稱M=fs/fN為“過采樣比”。在Σ-ΔADC的設(shè)計中,M遠(yuǎn)大于1,且取為2的整數(shù)次冪(如32、64等)。過采樣帶來的好處為壓縮基帶內(nèi)量化噪聲,降低對輸入端模擬濾波器的要求等。

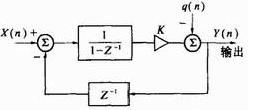

但是,光憑過采樣來壓縮基帶內(nèi)噪聲是低效率的,提高4倍采樣率才相當(dāng)于提高1bit分辨率。為了更有效地衰減基帶內(nèi)量化噪聲,應(yīng)在過采樣條件下進(jìn)一步加入噪聲成形(noise shaping)技術(shù)。最基本的一階噪聲成形器即所謂的一階Σ-Δ調(diào)制器,其原理此處不再討論。這里只指出,它可被轉(zhuǎn)化為如圖2所示的離散時間等效模型。

圖2 一階Σ-Δ調(diào)制器離散時間等效模型

圖2中的積分器用I(z)=(1-z-1)-1等效描述,而1bit ADC被加性噪聲源q(n)替代。嵌在反饋環(huán)路中的1bit DAC被一個單位時延z-1取代,以避免在離散時間模型中出現(xiàn)無時延反饋環(huán)。q(n)是與輸入信號無關(guān)的白噪聲,用它能夠方便地描述Σ-Δ調(diào)制器在大量信號作用下的平均行為,分析可得其輸入、輸出關(guān)系式為

Y(z)=X(z)+(1-z-1)Q(z) (4)

由上式可知,在信號頻譜X(z)未變的同時,白噪聲Q(z)被(1-z-1)加權(quán)而成為“高通”形狀。此現(xiàn)象正是所謂“噪聲成形”。加權(quán)函數(shù)(1-e-j2πfT)的零點f=0使得基帶內(nèi)噪聲被大大壓縮;而在帶外的高頻端,噪聲卻略有上升。

在實際應(yīng)用中,為更有效地壓低量化噪聲達(dá)到分辨率要求,還得考慮高階噪聲成形。一般地,將L個一階Σ-Δ調(diào)制器組合起來,可以實現(xiàn)(1-z-1)L(L階噪聲成形)。

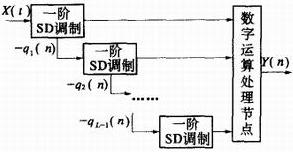

標(biāo)準(zhǔn)的MASH(Multistage Noise Shaping,多級噪聲成形)結(jié)構(gòu)如圖3。它實際上是L個一階Σ-Δ調(diào)制器的串聯(lián),其中前一級調(diào)制器內(nèi)的1bit ADC的量化誤差被送入下一級進(jìn)行再量化,然后將各級的輸出碼流送入運算節(jié)點進(jìn)行處理。最后輸出了經(jīng)(1-z-1)L成形處理后的低分辨率碼流。顯然,這樣的前饋結(jié)構(gòu)不會存在任何穩(wěn)定方面的問題。

圖3 MASH結(jié)構(gòu)框圖

MASH中的數(shù)字處理節(jié)點所做的工作是抵消各級的量化誤差:

第一級:Y1(z)=X(z)+(1-z-1)Q1(z),將-Q1(z)送入第2級,有Y2(z)=-Q1(z)+(1-z-1)Q2(z),再將-Q2(z)送入第3級,有Y3(z)=-Q2(z)+(1-z-1)Q3(z),..直至YL(z)=-QL-1(z)+(1-z-1)QL(z),而運算節(jié)點使得

Y(z)=Y1(z)+(1-z-1)Y2(z)+...+(1-z-1)L-1YL(z)=X(z)+(1-z-1)LQL(z) (5)

這樣,就等效實現(xiàn)了(1-z-1)L噪聲成形。除MASH外,還有許多新穎的采用計算機輔助設(shè)計的Σ-Δ噪聲成形方案,用其可實現(xiàn)更高效的噪聲成形。

3 一種DAC非線性誤差校正方法

在MASHΣ-ΔADC中,與一位(1bit)量化相比,采用多位量化器具有增大信噪比(SNR),增加穩(wěn)定性以及降低運算放大器規(guī)

格等優(yōu)點。然而,內(nèi)部DAC的非線性導(dǎo)致性能瓶頸,通常要求其最少具有與整個ADC同樣好的線性。現(xiàn)在,對于較大過采樣比(OSR>32),采用即時數(shù)字校準(zhǔn)、失配整形可解決此問題。但在寬帶ADC中,OSR較小(通常≤4),失配整形法就變得無效。本文描述了一種數(shù)字即時校準(zhǔn)方法。不同于較早的技術(shù),其對低過采樣比狀態(tài)有效。并且,此方法可以跟隨漂移。

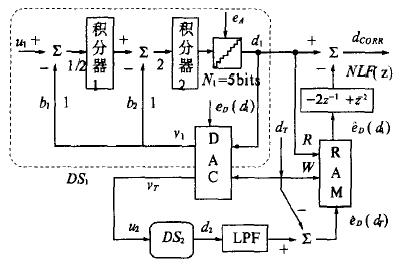

3.1 校正系統(tǒng)

以二階Σ-Δ調(diào)制器(DS1)為例來說明給出的校正技術(shù)。如圖4所示,內(nèi)部DAC有兩個輸出:v1和vT,分別輸入到循環(huán)濾波和校準(zhǔn)ADC(DS2)。由校準(zhǔn)ADC得到^eD,即所有輸出電平的DAC誤差eD的數(shù)字估計,并且其被存儲在RAM中。在轉(zhuǎn)換時,通過FIR濾波器NLF(z)過濾RAM的輸出,從而校正內(nèi)部DAC誤差,并從DS1的數(shù)字輸出d1中減去過濾輸出結(jié)果。獲得^eD的過程和系統(tǒng)的詳細(xì)分析在以下內(nèi)容中給出。

圖4 帶有誤差校正的Σ-Δ調(diào)制器

在圖4所示系統(tǒng)中,假設(shè)單獨DAC輸出為兩個積分器提供反饋信號。系數(shù)b1、b2的不匹配對系統(tǒng)線性沒有影響。值得注意的是,系統(tǒng)沒有對內(nèi)部ADC的非線性誤差進(jìn)行校正。這些誤差被與量化噪聲同樣的噪聲傳輸函數(shù)所抑制,其很少作為問題提出。當(dāng)使用很低的OSR時,這樣是不夠的,就高線性而言,需要增加階數(shù)或使用ADC元件失配整形。

3.2 校正方法

實際DAC輸出電平誤差的即時獲得適應(yīng)于DAC的結(jié)構(gòu)。如果DAC可提供多重輸入和輸出,那么離線校準(zhǔn)能夠被傳輸?shù)胶笈_進(jìn)程。如果那樣,對于DAC的每個可能的輸入,數(shù)字校準(zhǔn)信號dT將提供階梯波形。通過校準(zhǔn)Σ-Δ轉(zhuǎn)換器DS2,每個DAC輸出電平vT被轉(zhuǎn)換成數(shù)字形式d2,然后通過LPF低通濾波而消除DS2的量化誤差。然后,減去dT從而補償電平誤差eD,這樣,得到誤差估計^eD并將其存儲在RAM中,并且對每一輸出d1將再次調(diào)用^eD并校正。在運行過程中,周期性地重復(fù)校準(zhǔn),以追蹤DAC輸出電平中產(chǎn)生的漂移。

在低過采樣率(OSR)和低階循環(huán)濾波器情況下,從DAC的輸出v1到DS1的輸出d1的傳輸函數(shù)不能由NLF(z)=-1正確地近似。為了得到精確的誤差校準(zhǔn),如圖4所示,RAM的輸出需要被實際的NLF(z)(此處為-2z-1+z-2)過濾。

在一些DAC的實現(xiàn)中,使用了N個等價單位元件(電流源、電容、電阻等)。如果在DAC中執(zhí)行N+1個元件,可使用上述算法,利用DS2逐個順序地測量它們的誤差。換句話說,輸出信號d1與校準(zhǔn)信號dT一樣可被使用。利用n個單位元件通過調(diào)用d1值從而產(chǎn)生v1,剩余的N-n個單位元件被用來產(chǎn)生vT。如果DAC增益和偏移誤差是可以被接受的,為了使所有單位元件誤差總和可取零,那么vT中的誤差是v1中誤差的負(fù)數(shù)。因此,通過將vT中的模擬采樣分類進(jìn)入通道,使用其中一個通道專用于每個可能輸入(d1)碼和其補碼,DS2可用來以數(shù)字形式產(chǎn)生單獨DAC電平。由于為每一DAC電平復(fù)制存儲元件(反饋電容),DS2的運算可容易地在通道中多重復(fù)用。

由于線性運算,校準(zhǔn)ADC(DS2)自身必須要有高的線性。這需要在DS2中使用1位內(nèi)部量化器。但是,由于DAC非線性信息保持,線性影響(增益和偏移誤差)在DS2中是可以接受的。同樣,實際DAC誤差傳輸函數(shù)(從v1至d1)和其數(shù)字復(fù)制部分NLF(z)之間的匹配誤差對整個轉(zhuǎn)換器的線性僅有較小的影響。

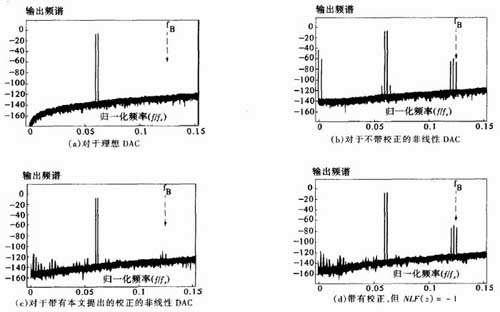

3.3 仿真結(jié)果

數(shù)字校正ADC(如圖4的DS2)的運行仿真條件如下述。假設(shè)5bit(322電平)內(nèi)部ADC和DAC,在DAC中有0.1%線性梯度誤

差。這符合中等誤差0.4%的要求。在所有電路中,所有運放和任意失配電容(有0.1%標(biāo)準(zhǔn)偏差)的有限直流增益設(shè)定為54dB。使用OSR=4。在DS1中加入峰值為0.45V的中頻雙音調(diào)輸入信號u1,采用二階單位Σ-ΔADC實現(xiàn)DS2。為了論證利用校準(zhǔn)可得到的高線性,DS1被接入在220MASH(包含10bitADC作為其第二級)中。這里不考慮在MASH(多級噪聲整形)各級中的失配,它同樣可由數(shù)字方法校正。

采用理想DAC、非理想運放和電容,系統(tǒng)運行計算出的頻譜如圖5(a)所示。圖5(b)給出了使用誤差校準(zhǔn)的非線性DAC得到的頻譜。可以看出,產(chǎn)生了大的諧波,SFDR僅為52dB。當(dāng)使用了本文提出的數(shù)字校正技術(shù)后,頻譜結(jié)果如圖5(c)所示,得到SFDR>100dB。為了得到這樣高的SFDR所需要的充分精確的eD估計,DS2對DAC的每一電平進(jìn)行了218采樣(如果DS2時鐘控制在fs=5MHz,那么后臺校準(zhǔn)完整循環(huán)需要約4秒)。最后,圖5(d)說明了使用NLF(z)=-1后的有害影響,即SFDR由101dB降至60dB。

圖5 MASH的輸出頻譜(215采樣,64倍FFT,fB=fs/8,OSR=4)

5 結(jié)論

本文介紹了Σ-Δ調(diào)制器的基本原理和技術(shù),并針對采用多位內(nèi)部量化器的MASH Σ-ΔADC提出了一種即時數(shù)字校正方法。對于低過采樣比的模數(shù)轉(zhuǎn)換器,采用通常的失配整形技術(shù)效果不佳,但本方法可有效應(yīng)用于此。通過仿真證明,使用本文提出的即時數(shù)字校正法可得到極好的線性。