隨著FPGA技術(shù)的廣泛使用,,越來越需要一臺(tái)能夠測(cè)試驗(yàn)證FPGA芯片中所下載電路邏輯時(shí)序是否正確的儀器。目前,,雖然Agilent,、Tektronix 等大公司生產(chǎn)的高端分析儀" title="邏輯分析儀" target="_blank">邏輯分析儀能夠?qū)崿F(xiàn)FPGA電路的測(cè)試驗(yàn)證功能,,但此類儀器價(jià)格高昂,一般要十萬,、數(shù)十萬人民幣,。所以,研究開發(fā)價(jià)格適中且具有邏輯分析儀和FPGA電路的測(cè)試驗(yàn)證功能的儀器是非常有價(jià)值的,。

本文所介紹的基于虛擬儀器技術(shù)的邏輯驗(yàn)證分析儀,,采用FPGA技術(shù)來實(shí)現(xiàn)儀器硬件部分的主要設(shè)計(jì),應(yīng)用圖形化編程語言LabVIEW來實(shí)現(xiàn)儀器的測(cè)試軟件設(shè)計(jì),。文中闡述了虛擬FPGA邏輯驗(yàn)證分析儀的總體設(shè)計(jì)方案及其工作原理,,并對(duì)儀器的兩個(gè)主要工作環(huán)節(jié)的開發(fā)設(shè)計(jì)作了具體介紹。虛擬FPGA邏輯驗(yàn)證分析儀除了具有FPGA電路的基本測(cè)試驗(yàn)證功能,,還具有邏輯分析儀和產(chǎn)生激勵(lì)信號(hào)的功能,。它是微機(jī)系統(tǒng)及數(shù)字電路設(shè)計(jì)、偵錯(cuò),、軟件開發(fā)和仿真的理想儀器,。

虛擬FPGA邏輯驗(yàn)證分析儀的設(shè)計(jì)

1 虛擬FPGA邏輯驗(yàn)證分析儀的總體設(shè)計(jì)

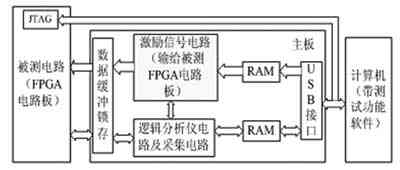

虛擬FPGA邏輯驗(yàn)證分析儀是把計(jì)算機(jī)作為數(shù)據(jù)的顯示控制,顯示器和鼠標(biāo),、鍵盤作為儀器的用戶面板,,其組成框圖如圖1所示。

圖1 虛擬FPGA邏輯驗(yàn)證分析儀組成框圖

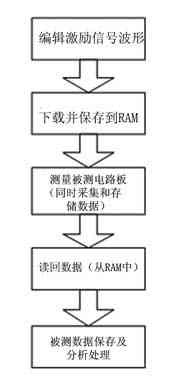

本儀器的基本工作原理是:由計(jì)算機(jī)編輯輸入電路的仿真激勵(lì)信號(hào)給所設(shè)計(jì)的被測(cè)電路,,同時(shí)進(jìn)行采集和存儲(chǔ),,再傳送回計(jì)算機(jī),最后進(jìn)行電路的邏輯時(shí)序分析等,,從而實(shí)現(xiàn)儀器的FPGA電路的基本測(cè)試驗(yàn)證功能以及邏輯分析儀功能和產(chǎn)生激勵(lì)信號(hào)的功能,。儀器的工作步驟如圖2所示。

圖2 虛擬FPGA邏輯驗(yàn)證分析儀工作流程圖

2 虛擬FPGA邏輯驗(yàn)證分析儀的硬件設(shè)計(jì)

虛擬FPGA邏輯驗(yàn)證分析儀的硬件組成包含三個(gè)部分:

?、僦靼?,具有數(shù)據(jù)采集、數(shù)據(jù)存儲(chǔ),、定時(shí)計(jì)數(shù),、主板與計(jì)算機(jī)進(jìn)行數(shù)據(jù)通信等多種功能。由于FPGA(現(xiàn)場(chǎng)可編程門陣列)可實(shí)現(xiàn)無限次地反復(fù)編程,,快速方便實(shí)用,,具有可現(xiàn)場(chǎng)模擬調(diào)試驗(yàn)證等特點(diǎn),所以本系統(tǒng)中比較復(fù)雜的控制器部分,、采樣部分等都采用FPGA實(shí)現(xiàn),;其他的由外圍芯片組成。外圍芯片上主要有RAM及數(shù)據(jù)緩沖和鎖存等數(shù)據(jù)通道部分。

?、贔PGA被測(cè)電路板,。

③通用的個(gè)人計(jì)算機(jī),,具有運(yùn)行圖形化編程軟件的能力,。

3 虛擬FPGA邏輯驗(yàn)證分析儀的軟件設(shè)計(jì)

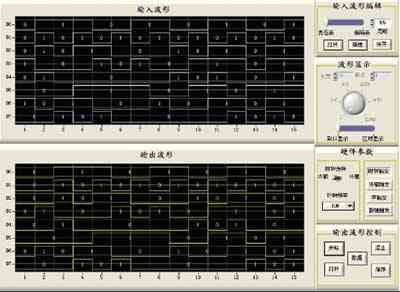

虛擬邏輯驗(yàn)證分析儀的軟件設(shè)計(jì)采用NI公司的圖形化編程語言工具LabVIEW7.0。FPGA測(cè)試驗(yàn)證軟件是一款包含數(shù)字波形打開,、編輯,、保存、瀏覽的高性能軟件,,在硬件的配合下,,可以完成數(shù)字波形的下載,即將編輯生成波形以數(shù)據(jù)形式加載到被測(cè)FPGA電路板的激勵(lì)端口,,并從輸出端口取回測(cè)試數(shù)據(jù)顯示,,以驗(yàn)證用戶下載到被測(cè)FPGA電路板中的可編程邏輯設(shè)計(jì)是否正確。軟件的主界面如圖3所示,。

圖3 軟件主界面

介紹虛擬FPGA邏輯驗(yàn)證分析儀的兩個(gè)工作環(huán)節(jié)

1 編輯激勵(lì)信號(hào)

虛擬FPGA邏輯驗(yàn)證分析儀的激勵(lì)信號(hào)源采用純軟件LabVIEW來實(shí)現(xiàn),,該激勵(lì)信號(hào)源可選擇以真值表方式(按位方式)或編碼表(總線方式)打開、編輯或保存數(shù)字激勵(lì)波形,,并可選擇周期數(shù),。其主要技術(shù)指標(biāo)如下。

?、佥斎敕绞剑赫嬷当?、總線方式編輯輸入;

?、谳敵鐾ǖ溃?3個(gè)輸出激勵(lì)信號(hào)數(shù)據(jù)通道,;

③顯示方式:

A:時(shí)序波形顯示,,可水平位移和水平伸縮;

B:數(shù)據(jù)顯示,,分為二進(jìn)制,、十六進(jìn)制顯示。

2 測(cè)量被測(cè)電路板

在虛擬FPGA邏輯驗(yàn)證分析儀的工作流程中,,測(cè)量被測(cè)電路板這一工作即將編輯好的仿真激勵(lì)信號(hào)輸入給所設(shè)計(jì)的被測(cè)電路板,,同時(shí)進(jìn)行采集和存儲(chǔ)所測(cè)試電路板的數(shù)據(jù)。該步驟中的采集工作主要采用FPGA來實(shí)現(xiàn),,存儲(chǔ)工作用RAM來完成,。通過分析論證,本設(shè)計(jì)采用ALTER公司Cyclone系列的芯片,型號(hào)為EP1C6Q144,。它采用1.5V內(nèi)核電壓,,內(nèi)嵌92160位存儲(chǔ)區(qū)間,可提供兩個(gè)鎖相環(huán)和雙信數(shù)據(jù)傳輸速率(DDR)的接口電路,。設(shè)計(jì)中,,邏輯分析儀電路及采集電路的主要技術(shù)指標(biāo)如下。

?、俨杉瘯r(shí)鐘:外時(shí)鐘和內(nèi)時(shí)鐘,;

②內(nèi)時(shí)鐘頻率:25kHz,、50kHz,、100kHz、250kHz,、500kHz,、1MHz、5MHz,、10MHz,;

③采集存儲(chǔ)點(diǎn)數(shù):1~2048,;

?、苡|發(fā)方式:時(shí)鐘觸發(fā)、外部觸發(fā),、字觸發(fā)和按鍵觸發(fā),。

結(jié)束語

本文所介紹的虛擬FPGA邏輯驗(yàn)證分析儀,采用FPGA技術(shù)來實(shí)現(xiàn)儀器硬件部分的主要設(shè)計(jì),,應(yīng)用圖形化編程語言LabVIEW來實(shí)現(xiàn)儀器的測(cè)試軟件設(shè)計(jì),。事實(shí)證明,該方案設(shè)計(jì)的虛擬FPGA邏輯驗(yàn)證分析儀不但具有FPGA電路的基本測(cè)試驗(yàn)證功能,,還有邏輯分析儀和產(chǎn)生激勵(lì)信號(hào)的功能,。通過實(shí)用證明,該儀器具有功能強(qiáng)大,、穩(wěn)定性好,、可擴(kuò)展性強(qiáng)及操作方便靈活等特點(diǎn),是教學(xué),、實(shí)驗(yàn)和科研的很好的輔助儀器,。