隨著便攜式產(chǎn)品越來越多,產(chǎn)品的功能,性能的提升,它們對電源管理的要求也更高了,這里跟大家探討的是CMOS LDO在便攜式產(chǎn)品中的應(yīng)用。便攜式產(chǎn)品在大多數(shù)情況下是靠電池供電,內(nèi)部(即電池后端)的電源管理有DC/DC和LDO兩種實現(xiàn)方式,各有優(yōu)缺點。正常工作時,DC/DC模塊能提供給系統(tǒng)穩(wěn)定的電壓,并且保持自身轉(zhuǎn)換的高效率,低發(fā)熱。但在一些應(yīng)用條件下,比如工作在輕載狀況下或是給RF供電時,DC/DC的靜態(tài)電流及開關(guān)噪聲就顯得比較大了, CMOS LDO正好可以滿足在這些應(yīng)用條件下的供電要求,CMOS LDO有著極低的靜態(tài)電流,極低的噪聲,較高的PSRR(電源紋波抑制比),以及較低的Dropout Voltage(輸入輸出電壓差)。

CMOS LDO產(chǎn)品的特點

1.CMOS LDO的自身功耗:

CMOS LDO在正常工作時,存在自身的功耗,可以大概表示為:

Pd=(Vin-Vout)×Iout+Vin×Iq,

由這個式子可以看出,重載以及大輸入輸出電壓差都會增大Pd,從而降低LDO的轉(zhuǎn)換效率。然而當(dāng)Iout=0時,Iq決定LDO的功耗,而CMOS LDO的Iq僅有1uA~80uA,使得LDO自身幾乎沒有功耗。

如在TCXO(溫度補償晶振)電源中,其只需要5mA的負(fù)載電流,Vout固定,若能控制Vin的值僅稍大于Vout+Vdrop,(一般地,CMOS LDO的Vdrop在Iout=5mA條件下,其值為5mV~10mV),則LDO的自身功耗Pd在不到1mW,這取決于方案設(shè)計工程師在應(yīng)用電路中的設(shè)計。

現(xiàn)在更多的工程師,將DC/DC與LDO共同設(shè)計進(jìn)電源管理方案中,因為他們發(fā)現(xiàn),開關(guān)型轉(zhuǎn)換器存在一定的噪聲干擾和高靜態(tài)電流等問題,這種情況在處理器供電應(yīng)用中尤為突出。開發(fā)商為了讓處理器在不執(zhí)行指令時保持極低的電能消耗,往往把產(chǎn)品設(shè)置為“深度睡眠模式”和“喚醒工作模式”兩種狀態(tài)。

而如果在“深度睡眠模式”下仍然采用開關(guān)型轉(zhuǎn)換器,其噪聲和靜態(tài)電流性能反而不如LDO優(yōu)越。基于這種情況,已經(jīng)有廠商針對處理器(例如基帶處理器)供電應(yīng)用推出了LDO與開關(guān)型轉(zhuǎn)換器雙模系統(tǒng)。當(dāng)處理器處于“喚醒工作模式”時,系統(tǒng)通過芯片內(nèi)部開關(guān)切換成PWM模式,LDO輸出為高阻態(tài),為處理器提供較高的電壓和較大的電流;而當(dāng)處理器處于“深度睡眠模式”時,系統(tǒng)通過芯片內(nèi)部開關(guān)切換成LDO模式,SW輸出為高阻態(tài),為處理器提供較低電壓和微小電流。

2.CMOS LDO的穩(wěn)定性:

典型LDO應(yīng)用需要增加外部輸入和輸出電容器。LDO穩(wěn)定性與輸出電容的ESR密切相關(guān),選擇穩(wěn)定區(qū)域比較大的LDO有利于系統(tǒng)的設(shè)計,并可以降低系統(tǒng)板的尺寸與成本。利用較低ESR的電容一般可以全面提高電源紋波抑制比、噪聲以及瞬態(tài)性能。

陶瓷電容器由于其價格低而且故障模式是斷路,通常成為首選;相比之下鉭電容器比較昂貴且其故障模式是短路。請注意,輸出電容器的ESR 會影響其穩(wěn)定性,陶瓷電容器具有較低的ESR,大概為10mΩ量級,而鉭電容器ESR在100 mΩ量級。

另外,許多鉭電容器的ESR隨溫度變化很大,會對LDO性能產(chǎn)生不利影響。BCD的CMOS LDO產(chǎn)品采用ESR范圍在10mΩ~100Ω的輸出電容就可以滿足全負(fù)載范圍內(nèi)的穩(wěn)定性。

3.電路簡單及價格低:

LDO的應(yīng)用電路都比較簡單,除了LDO自身以外,只需要2顆電容,個別產(chǎn)品還需要一顆bypass電容。總共只需要3~4顆原件。如此簡單的電路在成本也就相應(yīng)很低了。

|

4.電路所需PCB面積小:

CMOS LDO的Cin和Cout大多小于等于2.2uF,這樣的容值,0603封裝就可以做到了,LDO的封裝一般只是SOT-23或SC-70,整個電路在PCB上的面積只有20mm2~30mm2,極大的節(jié)省了電路板的空間。

|

CMOS LDO產(chǎn)品的應(yīng)用

由于CMOS LDO產(chǎn)品的拓?fù)浣Y(jié)構(gòu)決定了其較低靜態(tài)工作電流的特性,使得其非常適合在電池供電的手持設(shè)備系統(tǒng)中應(yīng)用。下面以PHS手機(jī)為例來說明CMOS LDO的應(yīng)用和選擇。

1.Baseband Chipset Power Supply

Baseband數(shù)字電路部分的工作電壓在1.8V~2.6V之間,當(dāng)手機(jī)鋰電池的電壓降到3.3V~3.2V時,手機(jī)將關(guān)機(jī),這時電池到BB工作電壓的壓差為500mV~600mV,對于CMOS LDO來說,這么大的工作電壓和壓差使LDO正常工作不是問題,低噪音和高PSRR都不是問題,而對BB工作在輕載時LDO的靜態(tài)電流要求要非常小。Baseband模擬電路部分的工作電壓在2.4V~3.0V,與手機(jī)最低工作電壓的差值為200mV~600mV,同時,需要在低頻時(217Hz)有較高的PSRR,用以抑制RF部分對電池的干擾。此外,這顆LDO的會始終處于工作狀態(tài),所以也要求有極低的靜態(tài)電流。

2.RF Power Supply

RF電路需要2.6V~3.0V的工作電壓。在電路中,如低噪音運放(LNA),up/down converter,mixer,PLL,VCO,和IF stage都要求很低噪音和很高PSRR的LDO

3.TCXO Power Supply

溫度補償晶振(TCXO)需要的是一顆極低噪音并帶有enable pin的LDO,盡管TCXO只需要5mA的工作電流,但它同樣要一顆單獨的高PSRR的LDO為其供電,來隔離其他噪聲源,如RF產(chǎn)生的低頻脈沖噪聲。

4.RTC Power Supply

RTC電源會一直處于工作狀態(tài),即使在手機(jī)關(guān)機(jī)以后。因此它需要一顆極低靜態(tài)電流的LDO,同時,這顆LDO要求具有小的反向漏電流的保護(hù)功能。

5.Audio Power Supply

在手機(jī)音頻電源方面,會用到300mA~500mA稍大電流的CMOS LDO,同時,也要求在音頻范圍內(nèi)(20Hz~20kHz)有低噪音和高PSRR的特性,來保證良好的音質(zhì)要求。

CMOS LDO產(chǎn)品的設(shè)計思想

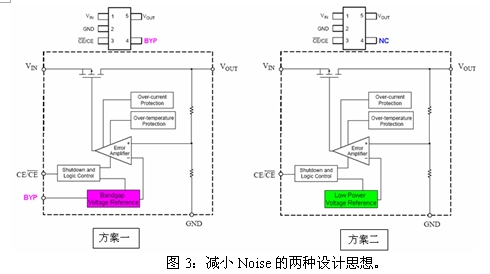

以下著重從Noise方面來闡述CMS LDO的設(shè)計思想。

|

從上面這個框圖可以看出,方案一比方案二要多封裝出來一個Pin,這個Pin一般稱作”Bypass”,對于這個Bypass管腳的作用描述往往是:An external bypass capacitor, connected to this terminal, in conjunction with an internal resistor, creates a low-pass filter to further reduce regulator noise.(Bypass腳外接一個電容,與電路內(nèi)部的電阻組成低通濾波器,用以減小Regulator的輸出噪聲)。因為加了這個Bypass電容(一般10nF),LDO對Enable(使能)響應(yīng)速度會變慢(從us級到ms級)。因此如果LDO的應(yīng)用場合沒有低噪聲的要求或?qū)υ肼曇蟛桓撸话憬ㄗh可不加這個電容。

LDO的輸出噪聲主要來自于Voltage Reference這個模塊,Bypass腳就是外接在Voltage Reference的輸出端。因此將Voltage Reference的噪聲降低,就能降低LDO的輸出噪聲。

方案一中,如不加bypass電容,CMOS LDO的噪聲一般在200~450uVrms(沒有負(fù)載時的電源電流越小,這個噪聲越大),加了這個電容濾波后,LDO的噪聲一般為30~50 uVrms,因此方案一的低噪聲CMOS LDO都是有這個Bypass腳,并且是必須加這個濾波電容才能做到低噪聲。

當(dāng)然也有例外,個別歐美的大廠商采用先進(jìn)的工藝設(shè)計生產(chǎn)的的CMOS LDO把本該外面加的Bypass電容做到了芯片里面,這樣的LDO產(chǎn)品的噪聲約為100 uVrms的水平。

方案一的思路是將噪聲用濾波器過濾掉大部分,而方案二的思路是將噪聲源減少,其核心就是低噪聲的器件工藝。采用方案二的CMOS LDO根本不需要Bypass電容,就能使輸出噪聲降低到30~50 uVrms。

從用戶角度來講,沒有這個Bypass電容,既可以節(jié)省系統(tǒng)成本,又能獲得較高的性能,何樂而不為。因此,對于輸出電流較小的CMOS LDO,無論在高中低端市場的各個層面,僅從性能價格比方面來講,方案二的產(chǎn)品都略勝方案一的產(chǎn)品,方案二的核心是低噪聲低功耗的器件工藝的采用。

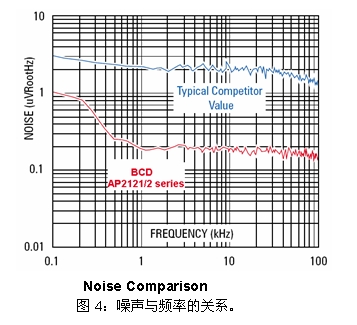

值得注意的是,采用低噪聲低功耗的器件工藝生產(chǎn)的CMOS LDO以其較高的性價比占據(jù)了同類產(chǎn)品市場的70%以上的份額。對于這種形勢,BCD憑借IDM公司工藝產(chǎn)品同步開發(fā)的優(yōu)勢,自行開發(fā)出了這種低噪聲低功耗的器件工藝,并在中國大陸率先達(dá)到了批量大生產(chǎn)的水平,基于這個生產(chǎn)工藝,BCD已推出其驗線的CMOS LDO產(chǎn)品AP2121/2、AP2138/9。并且,BCD還將陸續(xù)推出一系列電源管理IC新品。

|

四、BCD的CMOS LDO產(chǎn)品簡介

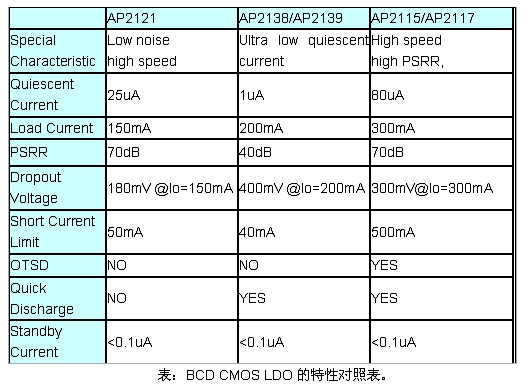

1.AP2121/AP2122

這是采用BCD的低噪聲低功耗CMOS工藝設(shè)計生產(chǎn)的低壓差、低噪聲、高電源紋波抑制比的LDO產(chǎn)品,其特點是最大輸出電流能力的最小值為150mA,300mA限流;靜態(tài)工作電源電流為25uA;在輸出電流150mA時的輸入輸出壓差小于200mV;電源紋波抑制比為70dB@1KHz;不需要外接Bypass電容,其輸出噪聲就小于50uVrms。在這個產(chǎn)品中采用了BCD的專利《用于提高低頻電源抑制比的電路及包含該電路的電路裝置》(中國專利:2004201166551.9.)。這個產(chǎn)品非常適合在手持式電子產(chǎn)品的BASE BAND上面的應(yīng)用。

2、AP2138/AP2139

這是另外一類采用BCD的低噪聲,低功耗CMOS工藝設(shè)計生產(chǎn)的低壓差、低噪聲、LDO產(chǎn)品,其特點是最大輸出電流能力的最小值為200mA,300mA限流;靜態(tài)工作電源電流為1uA;在輸出電流100mA時的輸入輸出壓差小于200mV;電源紋波抑制比為55dB@100Hz;不許外接Bypass電容,其輸出噪聲小于80uVrms。無論是直流性能還是瞬態(tài)響應(yīng)等多方面,AP2138/9都要比市面上的同類產(chǎn)品更勝一籌,非常適合用于MP3和手持式電子產(chǎn)品的RTC上面的應(yīng)用。

3、AP2115/AP2117

這是一款采用上面提到的方案一設(shè)計生產(chǎn)的低壓差、低噪聲、高電源紋波抑制比的LDO產(chǎn)品,其特點是最大輸出電流能力的最小值為300mA,500mA限流;靜態(tài)工作電源電流為80uA;在輸出電流300mA時的輸入輸出壓差僅為300mV;電源紋波抑制比為70dB@1KHz;不外接Bypass電容,其輸出噪聲為180uVrms,當(dāng)外接10nF的Bypass電容后輸出噪聲就小于30uVrms。值得一提的是,該類產(chǎn)品具有與使能端聯(lián)動的快速放電功能,有效地延長了電池的使用壽命,適用于RF、Audio Power Supply等。

|