對于主板設(shè)計師來說,要設(shè)計處理器電壓調(diào)節(jié)模塊(VRM)來滿足計算機處理器永無止境的功率需求實在是個大挑戰(zhàn)。Pentium 4處理器要求VRM提供的電流提高了約3倍。英特爾將其VRM指標(biāo)從8.4版本升級到9.0版本,涵蓋了新的功率要求,以繼續(xù)追隨摩爾(Moore)定律。

在過去的10年間,VRM電流要求一直在增加,正如英特爾所公布的,IccMAX從VRM9.0中的60A發(fā)展成驅(qū)動高端4核處理器的VRM11.0所要求的150A。與此同時,電流切換速率要求也有相當(dāng)大的提高;芯片插座處的dI/dT從450A/μs增加到1200A/μs。這給電路設(shè)計帶來了許多熱性能和電氣性能方而的挑戰(zhàn)。

處理器功耗的增加自然也刺激了那些專注為客戶提供增值服務(wù)的半導(dǎo)體廠商,推動他們開發(fā)各種創(chuàng)新的解決方案。VRM使用的功率MOSFET必須有盡可能低的導(dǎo)通電阻(Rds(on))、盡可能小的電感以及盡可能少的柵極電荷(Qg);這可從如下的功耗方程看出:

![]()

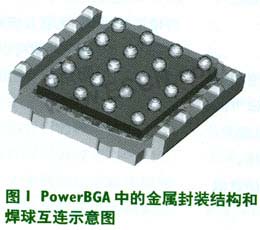

當(dāng)工作頻率增加到1MHz或者更高時,這些電氣參數(shù)尤其重要。當(dāng)然,功率MOSFET必須具有很好的熱性能。隨著MOSFET硅片技術(shù)的進(jìn)步,封裝技術(shù)逐漸成為性能提升的主要障礙。具體講,人們發(fā)現(xiàn)傳統(tǒng)的引線鍵合封裝(如DPAK和SO-8)使用的細(xì)線會使部件的寄生電阻顯著增加。在極端情況下,封裝增加的寄生電阻大小會與硅片本身的相當(dāng)。為此,MOSFET廠商開發(fā)出各種改良的封裝,如飛兆半導(dǎo)體的PowerBGA(見圖1)。這種封裝完全不用引線鍵合技術(shù),而是利用錫球和布有凸起的引線框,直接將硅片粘貼在印刷線路板(PWB)上。由于PowerBGA的銅帽有一小塊散熱片并利用空氣對流,結(jié)點到環(huán)境的熱阻較DPAK封裝降低50%以上,這是因為PowerBGA為強制對流冷卻提供了非常高效的散熱途徑。

VRM設(shè)計師喜歡相對較小的5mm×6mm SO-8封裝。但由于這種封裝是針對低功耗芯片設(shè)計的,因此不具備DPAK的熱性能。量產(chǎn)的MOSFET多是SO-8大小的部件,并帶有可焊接到PWB上的散熱片。這類組件在全球的使用會越來越多,這些封裝的熱性能通常接近DPAK,而且在采用某些互連技術(shù)時,其寄生電阻和電感還可能更小,同時,PWB面積也減小一半。這也是許多電子設(shè)計師喜歡采用這種封裝的原因。這是一個值得注意的進(jìn)步;因為,典型的4相VRM 10產(chǎn)品具有一個高壓側(cè)MOSFET和兩個低壓側(cè)MOSFET,總計12個。隨著主板功能越來越多(如納入音視頻、無線網(wǎng)絡(luò)等功能),可供VRM設(shè)計師使用的PWB空間越來越少,封裝尺寸就成為設(shè)計師考慮的一個非常重要的因素。

雖然,出于成本或第二供貨源考慮,許多設(shè)計最初都堅持采用傳統(tǒng)的IPAK和DPAK封裝,但為了滿足高功率要求,這些新型的封裝技術(shù)已經(jīng)越來越多地成為必要的選擇。現(xiàn)在已有許多5mm×6mm模塑引腳封裝的供應(yīng)商,這就解決了第二供貨源的問題。

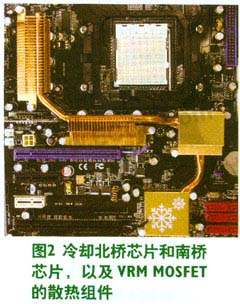

為了應(yīng)對未來的需求,出現(xiàn)了雙面封裝技術(shù),可讓主板設(shè)計師對高性能應(yīng)用的MOSFET進(jìn)行散熱處理,迫使MOSFET廠商成為總體解決方案的供應(yīng)商。過去,臺式電腦在處理器及北橋芯片和南橋芯片上使用散熱片。雖然這在先前的主板設(shè)計中不常見(主要是成本原因),但對MOSFET進(jìn)行散熱已越來越常見。高級主板市場已經(jīng)開始出現(xiàn)將北橋芯片和南橋芯片上的導(dǎo)熱管連接到VRM的MOSFET散熱片上的散熱組件(見圖2)。

在這些散熱處理方案中,有些直接將散熱片貼在DPAK的頂部。這種方案的效果非常差,因為塑料模件的熱導(dǎo)率一般只有1 W/m-K,而銅在典型消費電子溫度環(huán)境下的熱導(dǎo)率接近400W/m-K。我們相信封裝技術(shù)會響應(yīng)這一發(fā)展趨勢,而且MOSFET廠商在改進(jìn)傳統(tǒng)封裝技術(shù)的同時,將會提供品種及功能更多(如雙面冷卻功能)的封裝產(chǎn)品。

隨著MOSFET越來越多地集成到主板的熱系統(tǒng)中,主板設(shè)計師和MOSFET廠商必須更密切地合作。新的封裝產(chǎn)品(可能是專有的或設(shè)有工業(yè)標(biāo)準(zhǔn)的)為PWB設(shè)計師開辟出新的設(shè)計天地,同時也要求MOSFET廠商協(xié)助客戶使用新的產(chǎn)品,以確保客戶充分發(fā)揮封裝的性能。設(shè)計師挑選的MOSFET廠商必須了解針對應(yīng)用的系統(tǒng)層面,清楚MOSFET周圍組件的各種相關(guān)效應(yīng),了解組件上一塊散熱片能產(chǎn)生哪些效果和性能提升,了解表面貼裝工藝及其在應(yīng)用中的可靠性。

PWB面積的減小,以及節(jié)省成本的呼聲越來越高,使得VRM設(shè)計師轉(zhuǎn)而使用更高的開關(guān)頻率。增加同步降壓轉(zhuǎn)換器的開關(guān)速度可允許使用更小的電感和電容。小電感和小電容的成本低,并且PWB占位面積更小。當(dāng)然,天下沒有免費的午餐。提高開關(guān)頻率會因開關(guān)損耗增加而降低轉(zhuǎn)換器的效率。MOSFET、控制器和驅(qū)動電路的需求均有所改變,需要提供這些組件的廠家提出新的解決方案。

英特爾已推出DrMOS技術(shù)規(guī)范,作為建立整體(即集成同步降壓轉(zhuǎn)換器的高壓側(cè)MOSFET、低壓側(cè)MOSFET及驅(qū)動器)封裝解決方案標(biāo)準(zhǔn)的一種手段,該標(biāo)準(zhǔn)包括實現(xiàn)各種DrMOS兼容模塊和控制器間互用性的各種電氣和物理標(biāo)準(zhǔn)。

DrMOS方案采用8 mm×8mm和6mm×6mm四方扁平無引腳(QFN)封裝。將MOSFET和驅(qū)動器封裝在一起,使得供應(yīng)商能夠利用其對器件和封裝技術(shù)的經(jīng)驗來匹配MOSFET和驅(qū)動器,消除PWB的一些外部影響,如走線寬度和長度。由于MOSFET廠商能指定使用何種控制器,從而針對驅(qū)動器和封裝來優(yōu)化MOSFET,提供效率比分立元件更高的組件。而效率高意味著在相同電流下產(chǎn)生的熱量更少,有助于設(shè)計師解決散熱問題。隨著開關(guān)頻率高達(dá)1MHz的應(yīng)用越來越普遍,消除板上的走線及離散信號路徑引起的寄生效應(yīng),就顯得愈加重要。將分立元件的信號路徑(即從驅(qū)動器封裝中出來,經(jīng)過一個焊點,在板上走一段距離,再通過另一個焊點進(jìn)入MOSFET封裝件)縮減為兩塊硅片間單一的一組線鍵合有很多好處。同步降壓轉(zhuǎn)換器設(shè)計師之所以將這種封裝技術(shù)作為解決其設(shè)計難題的方案來研究,就是因為驅(qū)動器和MOSFET之間只有一個封裝電阻需要考慮。

雖然處理器設(shè)計師已經(jīng)大大提升了處理器效率,但這種提升并未降低處理器的功耗。為了應(yīng)對這一挑戰(zhàn),人們一直對MOSFET封裝技術(shù)進(jìn)行創(chuàng)新改進(jìn)。隨著以英特爾DrMOS規(guī)范為首的多芯片封裝技術(shù)越來越普及,封裝技術(shù)涉及的困難將會越來越多,廠商必須與最終客戶協(xié)同配合,創(chuàng)造出整體解決方案。