目前使用的圖像跟蹤系統(tǒng)前端輸入信號(hào)一般都是PAL制式的標(biāo)準(zhǔn)全電視信號(hào),每20 ms一場(chǎng),每40 ms一幀。模擬信號(hào)經(jīng)過(guò)視頻解碼器轉(zhuǎn)換成720×576大小的數(shù)字信號(hào)后,再對(duì)其中的目標(biāo)進(jìn)行分割、識(shí)別和跟蹤,并準(zhǔn)確計(jì)算出目標(biāo)的位置角度偏差,并傳給伺服機(jī)構(gòu)。在某系統(tǒng)中要求能對(duì)3×3像素大小的小目標(biāo)進(jìn)行精確跟蹤,為了達(dá)到跟蹤精度,可以提高圖像輸入的幀頻和提高圖像輸入的分辨率,因此前端采用了DALSA公司的一款基于Camera Link" title="Camera Link">Camera Link接口的數(shù)字?jǐn)z像機(jī),該相機(jī)的幀頻為100 Hz,分辨率高達(dá)1 400×1 024。這樣幀處理時(shí)間就只有10 ms,考慮到系統(tǒng)的實(shí)時(shí)性,我們采用了TI公司的高性能的DSP" title="DSP">DSP芯片TMS320C6414和高性能FPGA" title="FPGA">FPGA芯片EP2S30F672為核心的硬件處理平臺(tái)。

1 系統(tǒng)硬件結(jié)構(gòu)和工作原理

整個(gè)圖像跟蹤模塊的結(jié)構(gòu)圖如圖1中虛線框所示,整個(gè)系統(tǒng)包括以FPGA為核心的圖像采集和預(yù)處理單元,以DSP為核心的圖像處理單元以及由FPGA控制的圖像顯示單元。

由于采集、處理、顯示均要訪問(wèn)存儲(chǔ)器,為了降低成本,用普通的異步SRAM" title="RAM">RAM構(gòu)成。按照功能來(lái)分可分為采集處理用SRAM組和采集顯示用SRAM組,每組分別包括兩片SRAM,其讀寫(xiě)邏輯由FPGA控制,采用乒乓方式進(jìn)行切換。

對(duì)于采集處理部分,第K幀時(shí),SRAM1由FPGA控制寫(xiě)入圖像數(shù)據(jù),同時(shí)SRAM2由DSP讀數(shù)進(jìn)行處理;第K+1幀時(shí)則相反,SRAM2由FPGA控制寫(xiě)入圖像數(shù)據(jù),同時(shí)SRAM1由DSP讀數(shù)進(jìn)行處理。

對(duì)于采集顯示部分,第K幀時(shí),SRAM3由FPGA控制寫(xiě)入圖像數(shù)據(jù),同時(shí)SRAM4由FPGA讀數(shù)進(jìn)行顯示;第K+1幀時(shí)則相反,SRAM4由FPGA控制寫(xiě)入圖像數(shù)據(jù),同時(shí)SRAM3由FPGA讀數(shù)進(jìn)行顯示。

整個(gè)系統(tǒng)工作過(guò)程都是這樣的:其中圖像采集單元經(jīng)由差分轉(zhuǎn)換芯片后變成LVTTL信號(hào),直接連至FPGA,由FPGA控制數(shù)字圖像的采集,進(jìn)行圖像預(yù)處理后,將圖像數(shù)據(jù)存儲(chǔ)在SRAM中,給DSP發(fā)出中斷信號(hào),DSP響應(yīng)中斷后,從SRAM中讀取一幀圖像數(shù)據(jù)后,進(jìn)行圖像分割、目標(biāo)提取、目標(biāo)跟蹤算法,計(jì)算出方位和高度角偏差分量,將結(jié)果通過(guò)FPGA的片內(nèi)的板間通信雙口RAM傳遞給主控模塊,主控模塊再調(diào)整伺服機(jī)構(gòu)保證被跟蹤的目標(biāo)處于視場(chǎng)中心。

主控模塊還可以將系統(tǒng)的一些狀態(tài)變量實(shí)時(shí)的通過(guò)板間通信雙口RAM傳給DSP,DSP根據(jù)這些狀態(tài)生成需要顯示的字符,將這些字符寫(xiě)入到FPGA片內(nèi)字符疊加雙口RAM中。FPGA讀取顯示RAM中的圖像數(shù)據(jù)和片內(nèi)字符疊加雙口RAM內(nèi)的數(shù)據(jù),在原圖上疊加十字絲和波門(mén),以及系統(tǒng)的一些狀態(tài)字符信息,按照PAL制式時(shí)序向DA芯片送視頻數(shù)據(jù),這樣監(jiān)視器就可以輸出標(biāo)準(zhǔn)的PAL制式的圖像。

2 各個(gè)單元設(shè)計(jì)

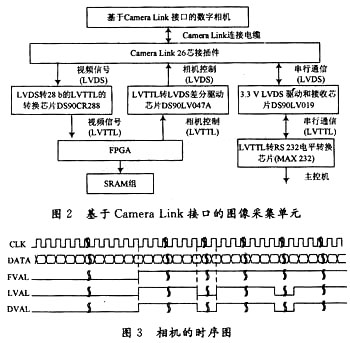

2.1 基于Camera Link接口的圖像采集和預(yù)處理單元

Camera Link是一種基于視頻應(yīng)用發(fā)展而來(lái)的接口,它解決了視頻數(shù)據(jù)輸出和采集之間的速度匹配問(wèn)題。Camera Link數(shù)據(jù)的傳輸率非常高,可達(dá)1 Gb/s,采用了LVDS格式,抗噪性能好。Camera Link的信號(hào)包括三個(gè)部分:串行通信部分、相機(jī)控制部分、視頻信號(hào)部分,基于Camera Link接口的圖像采集單元詳圖見(jiàn)圖2,每個(gè)部分采用專門(mén)的差分轉(zhuǎn)換芯片。串行通信部分則將異步串口轉(zhuǎn)換成標(biāo)準(zhǔn)的RS 232電平,這樣可以由主控機(jī)對(duì)相機(jī)的曝光時(shí)間、對(duì)比度等設(shè)置進(jìn)行調(diào)節(jié)。相機(jī)控制部分包括4對(duì)差分信號(hào),用來(lái)對(duì)相機(jī)進(jìn)行控制,比如相機(jī)的外同步信號(hào)輸入控制,可以由FPGA進(jìn)行控制。視頻部分的28 b LVTTL信號(hào)是關(guān)鍵控制部分,它們直接接在FPGA上,由FPGA來(lái)控制采集的時(shí)序。

這28 b數(shù)據(jù)中包括3個(gè)數(shù)據(jù)端口:A口(8 b)、B口(8 b)、C口(8 b),和4個(gè)視頻控制信號(hào)FVAL(幀有效)、DVAL(數(shù)據(jù)有效)、LVAL(行有效)、SPARE(空,暫時(shí)未用)。至于經(jīng)過(guò)Camera Link芯片轉(zhuǎn)換后的時(shí)鐘信號(hào),則是整個(gè)相機(jī)的同步驅(qū)動(dòng)信號(hào),所有的數(shù)據(jù)和視頻控制信號(hào)都是和該時(shí)鐘信號(hào)同步的,相機(jī)的時(shí)序圖見(jiàn)圖3。

相機(jī)可以配置成8 b或10 b的輸出位寬,40 MHz像素時(shí)鐘或80 MHz像素時(shí)鐘,2×40 MHz或2×80 MHz的數(shù)據(jù)輸出速率。關(guān)于Camera Link的采集數(shù)據(jù)的邏輯代碼,關(guān)鍵之處在于產(chǎn)生存儲(chǔ)器的地址信號(hào)、存儲(chǔ)器寫(xiě)信號(hào)以及在對(duì)應(yīng)的地址處將數(shù)據(jù)穩(wěn)定地寫(xiě)進(jìn)存儲(chǔ)器。我們用像素時(shí)鐘產(chǎn)生列地址計(jì)數(shù)器,行同步信號(hào)產(chǎn)生行地址計(jì)數(shù)器,二者拼接產(chǎn)生存儲(chǔ)器的地址信號(hào)。這樣產(chǎn)生的有效地址雖然不連續(xù),但意義明確,而且有利于顯示部分的隔行隔列顯示。對(duì)于8 b的數(shù)據(jù),可將4個(gè)有效數(shù)據(jù)拼接成32 b后再存儲(chǔ),這樣可以降低FPGA讀寫(xiě)存儲(chǔ)器的速度。

2.2 基于FPGA的圖像預(yù)處理單元

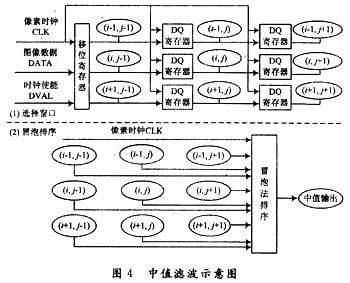

針對(duì)圖像預(yù)處理階段運(yùn)算結(jié)構(gòu)比較簡(jiǎn)單的特點(diǎn),用FPGA進(jìn)行硬件實(shí)現(xiàn)無(wú)疑是理想的選擇,這樣同時(shí)兼顧了速度和靈活性,大大減輕了DSP的負(fù)擔(dān)。這里采用的預(yù)處理算法主要是中值濾波,中值濾波器是一種非線性濾波器,與均值濾波器和類似其他形式的濾波器相比,中值濾波器具有能夠徹底濾除尖波干擾噪聲同時(shí)又能夠較好地保護(hù)目標(biāo)圖像邊緣等優(yōu)點(diǎn)。中值濾波的具體實(shí)現(xiàn)過(guò)程一般為:

(1)選擇一個(gè)n×n的滑動(dòng)窗口(通常為3×3或者5×5),使其沿圖像數(shù)據(jù)的行或者列方向逐像素滑動(dòng)(通常為從左至右,從上到下逐行移動(dòng))。

(2)每次滑動(dòng)后,對(duì)窗口內(nèi)的像素灰度值進(jìn)行排序,用排序所得的中間值代替窗口中心位置像素的灰度值。

用硬件實(shí)現(xiàn)二維中值濾波,很重要的一點(diǎn)是能可靠地存儲(chǔ)實(shí)時(shí)圖像數(shù)據(jù),并且使延時(shí)最短。在存儲(chǔ)n-1行圖像數(shù)據(jù)后便開(kāi)始處理,其中n為窗口大小,在本設(shè)計(jì)中,選用3*3窗口的中值濾波器,即n=3。這樣設(shè)計(jì)的好處是,F(xiàn)PGA可以以串行流水方式實(shí)現(xiàn)該模塊,節(jié)省了許多時(shí)間,為實(shí)時(shí)處理創(chuàng)造了有利條件。

為了盡量節(jié)約資源,充分利用硬件設(shè)計(jì)中的“模塊復(fù)用”原則,需設(shè)計(jì)1個(gè)移位寄存器、1個(gè)dq寄存器、1個(gè)二值比較器,然后在像素時(shí)鐘的驅(qū)動(dòng)下,首先調(diào)用移位寄存和dq寄存器產(chǎn)生窗口數(shù)據(jù),然后對(duì)3×3模板里的數(shù)據(jù)多次調(diào)用dq寄存器和2值比較器進(jìn)行冒泡排序輸出中間值。中值濾波模塊示意圖見(jiàn)圖4。

2.3 基于DSP的圖像處理單元

TMS320C6414芯片是一款高性能定點(diǎn)DSP處理器,其主頻可以高達(dá)720 MHz,片內(nèi)具有豐富的RAM資源,同時(shí)通過(guò)EMIFA和EMIFB口可以擴(kuò)展很多存儲(chǔ)芯片。這里主要擴(kuò)展的是程序FLASH芯片,用于存放固化的程序代碼。

前面已經(jīng)說(shuō)明了FPGA如何控制SRAM讀寫(xiě)邏輯的,DSP的主要工作是響應(yīng)FPGA發(fā)出的中斷信號(hào),讀取圖像數(shù)據(jù)進(jìn)行處理,雖然每一幀讀取的實(shí)際的SRAM不同,但是通過(guò)FPGA的映射后,對(duì)于DSP來(lái)說(shuō),SRAM始終在DSP片外的一端固定地址范圍內(nèi)。DSP響應(yīng)中斷的流程圖見(jiàn)圖5。

以常用的最簡(jiǎn)單的矩心跟蹤算法為例,DSP每次響應(yīng)中斷后,主要進(jìn)行的工作是:首先設(shè)定搜索的波門(mén),將波門(mén)內(nèi)的數(shù)據(jù)通過(guò)DMA方式快速搬移到片內(nèi)存儲(chǔ)器,然后用矩心跟蹤算法進(jìn)行處理,直至搜索出目標(biāo)后,將目標(biāo)的像素的位置偏差計(jì)算出來(lái)并送給主控板。

2.4 基于FPGA的圖像顯示單元

系統(tǒng)要求輸出標(biāo)準(zhǔn)的PAL制式的模擬視頻,由于PAL制式視頻場(chǎng)頻為50 Hz,幀頻為25 Hz,所以對(duì)于前端高分辨率高幀頻的數(shù)字圖像,必須降頻輸出,且分辨率也要降低。選用專用的圖像DA芯片ADV7123,該芯片輸入位寬為10 b,可以轉(zhuǎn)換的數(shù)據(jù)速率可達(dá)240 MHz。因?yàn)闃?biāo)準(zhǔn)的PAL制式視頻一幀只能顯示有效行576行,對(duì)于1 024行的數(shù)據(jù)圖像只能隔行顯示512行,且奇場(chǎng)256行,偶場(chǎng)256行。所以對(duì)于采集的圖像來(lái)說(shuō)行方向上是降低了分辨率,但在列的方向上不降低分辨率。

由前面可知,由于采集顯示采用乒乓結(jié)構(gòu),但是由于顯示是隔行抽點(diǎn)顯示的,且顯示的頻率幀頻為25 Hz,所以在采集部分時(shí),應(yīng)當(dāng)隔行取數(shù)據(jù)存儲(chǔ),且每2幀才更新一次采集的數(shù)據(jù)。不像采集處理部分一樣,每幀都要更新采集的數(shù)據(jù)。

控制ADV7123的時(shí)鐘信號(hào)、復(fù)合同步信號(hào)、復(fù)合消隱信號(hào)均由FPGA產(chǎn)生。與電視相關(guān)的行、場(chǎng)同步和消隱信號(hào)正是PAL制式模擬視頻信號(hào)生成的關(guān)鍵。

FPGA認(rèn)通過(guò)對(duì)數(shù)字相機(jī)下來(lái)的80 MHz時(shí)鐘倍頻后,經(jīng)過(guò)時(shí)鐘計(jì)數(shù)和邏輯組合運(yùn)算獲得所需要的各種同。步時(shí)序信號(hào)。ADV7123的時(shí)鐘信號(hào)根據(jù)80 MHz時(shí)鐘先2倍頻后蔣5分頻而成,即像素時(shí)鐘頻率為32 MHz,周期為31.25 ns。生成的圖像大小為1 400×576像素,即每場(chǎng)圖像有288行,每行有1 400個(gè)像素點(diǎn)。系統(tǒng)采用PAL制式的隔行掃描方式,場(chǎng)周期時(shí)間為20 ms,行周期為64μs,所以每場(chǎng)包含312.5個(gè)行周期,但場(chǎng)消隱的高電平持續(xù)288個(gè)行周期,只要調(diào)整場(chǎng)消隱信號(hào)的起始位置,就很容易使視頻圖像的輸出位于屏幕的正中間。行場(chǎng)同步信號(hào)和消隱信號(hào)的實(shí)現(xiàn)思路基本上一樣:對(duì)時(shí)鐘計(jì)數(shù),計(jì)到某一個(gè)數(shù)值時(shí),使輸出的信號(hào)翻轉(zhuǎn)(由低電平到高電平或者由高電平到低電平),計(jì)數(shù)器的周期和翻轉(zhuǎn)的周期根據(jù)不同的參數(shù)而有所不同。由于這些時(shí)序是在FPGA中編程實(shí)現(xiàn),很容易調(diào)整和修改。

至于字符疊加過(guò)程,DSP按照在圖像上實(shí)際疊加字符的位置和大小將要疊加的字符點(diǎn)陣寫(xiě)入到FPGA片內(nèi)雙口RAM中(顯示字符的地方寫(xiě)二進(jìn)制的1,顯示圖像的地方寫(xiě)二進(jìn)制的0),顯示輸出的每一幀,F(xiàn)PGA讀取字符疊加雙口RAM,根據(jù)其值來(lái)決定是輸出采集的圖像還是輸出疊加字符。這樣通過(guò)DSP和FPGA的配合,可以靈活地疊加任何字符,DSP可以根據(jù)系統(tǒng)的任何狀態(tài)變化來(lái)改變字符疊加RAM中的值,因此保證系統(tǒng)具有良好的人機(jī)交互界面。

3 結(jié)語(yǔ)

以高性能DSP和FPGA為核心,對(duì)Camera Link接口的數(shù)字相機(jī)進(jìn)行圖像采集,采用數(shù)字圖像處理技術(shù),建立了一個(gè)實(shí)時(shí)的圖像跟蹤系統(tǒng)。該系統(tǒng)體積小、重量輕、可靠性高,具有良好的人機(jī)交互界面,已經(jīng)成功地應(yīng)用在實(shí)際項(xiàng)目中。