引言

顯示系統(tǒng)在工業(yè)、農(nóng)業(yè)及日常生活中扮演著越來越重要的角色,因此,對其進行設(shè)計與研究具有十分重要的意義。

CPLD" title="CPLD">CPLD" target="_blank">CPLD(Complex Programmable Logic Device;復(fù)雜可編程邏輯器件)具有編程靈活、集成度高、設(shè)計開發(fā)周期短、適用范圍寬、開發(fā)工具先進等優(yōu)點,用戶可根據(jù)自身需要構(gòu)造數(shù)字集成電路。其基本設(shè)計方法是借助集成開發(fā)軟件平臺,用原理圖、硬件描述語言等方法,生成相應(yīng)的目標(biāo)文件,通過下載電纜將代碼傳送到目標(biāo)芯片中,從而實現(xiàn)數(shù)字系統(tǒng)。CPLD的應(yīng)用目前已深入網(wǎng)絡(luò)、儀器儀表、汽車電子、數(shù)控機床、航天測控設(shè)備等領(lǐng)域,其設(shè)計及應(yīng)用成為電子工程師必備的一項技能。

系統(tǒng)總體設(shè)計方案

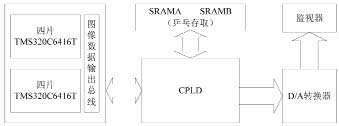

XC95144XL是5ns引腳延遲、系統(tǒng)頻率高達178MHz、144個宏單元、3200個可用邏輯門單元的可編程邏輯器件。本設(shè)計采用XC95144XL作為數(shù)據(jù)傳輸與控制核心模塊,接受來自TMS320C6416T的視頻數(shù)據(jù),并采用兩片IS61WV51216ALL組成緩存,以達到實時輸入輸出數(shù)據(jù)的效果。本部分實現(xiàn)框圖如圖1所示。

|

|

|

圖1 視頻顯示" title="視頻顯示">視頻顯示功能框圖 |

系統(tǒng)硬件設(shè)計

系統(tǒng)硬件設(shè)計主要包括:TMS320C6416T與VGA" title="VGA">VGA顯示系統(tǒng)的接口設(shè)計;2片IS61WV51216ALL SRAM組成的緩存模塊;視頻DAC模塊。

TMS320C6416T與VGA顯示系統(tǒng)的接口設(shè)計

來自4片TMS320C6416T的圖像處理機的EMIFB口連接在一起,并通過CPLD的仲裁,使能哪一塊圖像處理機輸出數(shù)據(jù)至VGA顯示系統(tǒng)。

采用C6416T的EMIFB口輸出處理結(jié)果,當(dāng)1片C6416T要求輸出數(shù)據(jù)時,C6416T要通過GP01向CPLD發(fā)送輸出數(shù)據(jù)請求,CPLD根據(jù)內(nèi)部邏輯確定是否允許C6416T請求。內(nèi)部邏輯準(zhǔn)則如下:

各個DSP的輸出數(shù)據(jù)請求優(yōu)先級別相等,請求信號先到者先被允許,后到者不能中斷正在響應(yīng)的請求。對于同時到來的請求,CPLD響應(yīng)先接收到原始視頻信號的C6416T。

當(dāng)CPLD響應(yīng)一個C6416T的輸出數(shù)據(jù)請求時,CPLD向C6416T的BHOLD#信號發(fā)送響應(yīng)信號(對EMIFB的保持請求輸入信號)。此時,數(shù)據(jù)開始輸出。

2片IS61WV51216ALL SRAM組成的緩存模塊

2片XC95144XL各自連接1片IS61WV51216ALL組成的圖像緩存模塊。

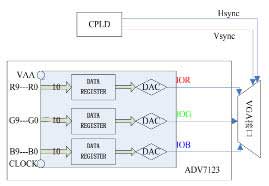

實時顯示控制:由CPLD對各個6416T圖像處理機數(shù)據(jù)輸出接口(EMIFB)總線進行總線仲裁,實現(xiàn)各個6416T圖像處理機的圖像數(shù)據(jù)分時輸出。由于VGA的刷新頻率大于輸入信號的頻率,因此采用兩片SRAM“乒乓存取”工作方式,組成了圖像數(shù)據(jù)緩沖區(qū),每片SRAM存放一幀圖像,由CPLD控制其乒乓讀寫切換以達到實時顯示效果。數(shù)據(jù)緩存電路框圖如圖2所示。

|

|

|

圖2 數(shù)據(jù)緩存電路框圖 |

采用一組SRAM作為顯存,可以簡化系統(tǒng)設(shè)計、降低成本。這時可以考慮利用行時序和幀時序中SRAM總線空閑的時序段,在不關(guān)閉圖像顯示的情況下實現(xiàn)顯存SRAM的數(shù)據(jù)更新。該方法的更新率與數(shù)據(jù)寫速度密切相關(guān),顯存的寫數(shù)據(jù)速度越快,該方法的更新率就越高。

視頻DAC模塊

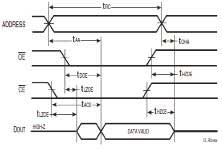

ADV7123是一個三路10位輸入的高速視頻DAC,具有330MHz的最大采樣速度,與多種高精度的顯示系統(tǒng)兼容,包括RS-343A和RS-170,可以廣泛應(yīng)用于如HDTV、數(shù)字視頻系統(tǒng)(1600*1200 @100Hz)、高分辨率的彩色圖片圖像處理、視頻信號再現(xiàn)等,因此能夠滿足多方面應(yīng)用需求。視頻DAC(ADV7123)工作原理如圖3所示。

|

|

|

圖3 ADV7123工作原理 |

CPLD提供Hsync(行)、Vsync(場)同步信號,直接接入15針的VGA顯示接口連接器。在點時鐘脈沖pixel clock的作用下將3路10位的RGB信號送入數(shù)據(jù)寄存器,而后送到3個DAC模塊,復(fù)合消隱信號和復(fù)合同步信號加到紅、綠、藍模擬信號送到輸出端。

系統(tǒng)軟件設(shè)計

系統(tǒng)軟件設(shè)計是本文的重點,主要包括三部分內(nèi)容:SRAM讀寫狀態(tài)機的設(shè)計、CPLD與SRAM的緩沖模塊通信以及VGA時序設(shè)計。

SRAM讀寫狀態(tài)機的設(shè)計

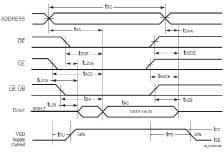

以6416為核心的圖象處理機通過外部存儲器接口向外傳送數(shù)據(jù),連接到后端的顯示系統(tǒng);但SRAM需要嚴(yán)格的通信時序確保數(shù)據(jù)的完整性,此處在CPLD內(nèi)部通過狀態(tài)機構(gòu)造SRAM的讀時序和寫時序,確保了6416能夠和SRAM正常通信,也確保緩沖模塊的正常運行。讀寫SRAM的時序圖如圖4和圖5所示。

|

|

|

圖4 讀周期時序圖 |

|

|

|

圖5 寫周期時序圖 |