摘 要: 結(jié)合軟件無(wú)線電的思想提出了一種寬帶數(shù)字下變頻的設(shè)計(jì)方案,并從硬件上實(shí)現(xiàn)了基于ADSP—TS101S的高性能" title="高性能">高性能中頻處理模塊" title="處理模塊">處理模塊。

關(guān)鍵詞: TS101S 軟件無(wú)線電 寬帶數(shù)字下變頻

寬帶接收是快速發(fā)現(xiàn)、全景監(jiān)控短波頻段信號(hào)的基礎(chǔ),它的出現(xiàn)為接收跳頻、擴(kuò)頻等快速?gòu)?fù)雜的信號(hào)提供了一種很好的解決方案。高性能中頻數(shù)字處理模塊是寬帶信號(hào)接收系統(tǒng)的重要組成部分,如何高效地從寬帶中頻數(shù)據(jù)流中提取出系統(tǒng)感興趣的窄帶信號(hào)是本模塊所要解決的關(guān)鍵技術(shù)難題。

1 系統(tǒng)主要組成部分

1.1 實(shí)現(xiàn)功能

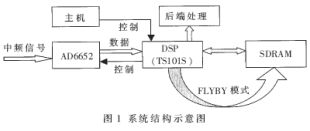

本設(shè)計(jì)采用二級(jí)DDC的方案,第一級(jí)寬帶DDC采用專用DDC芯片技術(shù),以降低系統(tǒng)對(duì)射頻前端和信號(hào)處理的要求,提高接收系統(tǒng)中頻的選擇性能。第二級(jí)DDC則利用DSP技術(shù)和多相" title="多相">多相濾波高效算法實(shí)現(xiàn)了在單片DSP(TS101)中同時(shí)提取四路窄帶中頻數(shù)字信號(hào)的功能。采用大容量數(shù)據(jù)緩沖池,保證了關(guān)鍵報(bào)頭的捕獲。其硬件平臺(tái)如圖1所示。

1.2 工作流程

如圖1所示,模擬中頻信號(hào)輸入到AD6652,主機(jī)控制DSP(TS101S),通過(guò)軟件改變AD6652的下變頻參數(shù),完成A/D" title="A/D">A/D變換與第一級(jí)DDC抽取,之后數(shù)據(jù)通過(guò)與TS101S互接的高速Link口輸入DSP;DSP對(duì)輸入的數(shù)據(jù)進(jìn)行濾波,抽出窄帶信號(hào)輸出到后端進(jìn)行處理。為了避免處理中丟失報(bào)頭,數(shù)據(jù)在輸入到TS101S處理的同時(shí)通過(guò)DMA通道儲(chǔ)存到SDRAM緩存一段時(shí)間以便查找。

(1) TS101S 簡(jiǎn)介

本模塊中ADC采樣頻率為40MHz , 經(jīng)第一級(jí)DDC后輸出到DSP。DSP對(duì)信號(hào)進(jìn)行處理,根據(jù)主機(jī)指定的多個(gè)信號(hào)中心頻率同時(shí)實(shí)現(xiàn)四路軟件DDC。從帶寬為500kHz的信號(hào)中輸出帶寬為125Hz~3kHz的信號(hào),需要DSP具有很高的運(yùn)算能力,故選用 ADSP—TS101S。

TS101S 是AD公司新近推出的高性能浮點(diǎn)DSP,具有極高的處理能力,峰值浮點(diǎn)性能1800MFLOPS,主頻可達(dá)250MHz或300MHz;TigerSHARC靜態(tài)超標(biāo)量結(jié)構(gòu)使DSP每周期能夠執(zhí)行多達(dá)4條指令、24個(gè)16位定點(diǎn)運(yùn)算和6個(gè)浮點(diǎn)運(yùn)算;3條相互獨(dú)立的128位寬的內(nèi)部數(shù)據(jù)總線,每條連接了3個(gè)2Mbit內(nèi)部存儲(chǔ)器塊中的一個(gè),提供4字(word)的數(shù)據(jù)、指令及I/O" title="I/O">I/O訪問(wèn)和14.4Gbps的內(nèi)部存儲(chǔ)器帶寬;此外還有4個(gè)8bit全雙工高速Link口,每個(gè)Link口傳輸率達(dá)到250Mbps,可以方便靈活地進(jìn)行高速數(shù)據(jù)傳輸。

(2) AD6652簡(jiǎn)介

AD6652是ANALOG公司的高速AD&DDC器件,它包含1個(gè)集成雙通道并具有12 位精度的ADC和1個(gè)集成4通道并具有最高帶寬為120kHz(單通道)的DDC。由于該器件內(nèi)部高速采樣保持電路性能優(yōu)良,故適合帶通采樣。

ADC 為差分輸入,最高采樣率為65MSPS,最高模擬輸入信號(hào)頻率為200MHz。DDC 為矩陣輸入,輸入更加靈活,減少了交叉連接產(chǎn)生的寄生信號(hào);同時(shí)可以根據(jù)應(yīng)用的不同在CIC5 濾波后進(jìn)行多相合并,增加帶寬;在后端有數(shù)字AGC 功能,適合于ADC 的寬帶輸入信號(hào)經(jīng)過(guò)DDC變成幾路窄帶信號(hào)后的增益調(diào)整。ADC 的數(shù)據(jù)輸出在內(nèi)部直接連接到接收器的DDC 的輸入矩陣,簡(jiǎn)化了設(shè)計(jì),減少了交叉連接產(chǎn)生的寄生信號(hào),大大改善了中頻數(shù)字處理模塊的性能,具有并行數(shù)據(jù)和Link口兩種輸出方式。

(3) 數(shù)據(jù)緩沖池

TS101S內(nèi)部集成了一個(gè)SDRAM控制器,能夠直接驅(qū)動(dòng)最大容量為256MB的外部SDRAM。本設(shè)計(jì)采用MICRON公司的128M DIMM168內(nèi)存條MT4LSDT1664AG作為數(shù)據(jù)緩沖池。

AD6652到數(shù)據(jù)緩沖池的數(shù)據(jù)傳輸采用TS101S的FLYBY模式:數(shù)據(jù)從外部I/O設(shè)備通過(guò)TS101S的DMA通道直接輸入SDRAM,不涉及核操作,非常經(jīng)濟(jì)。采用FLYBY模式實(shí)現(xiàn)高速緩存示意圖如圖2所示。

(4) 軟件接收機(jī)模塊

AD6652處理后輸出的信號(hào)帶寬為500kHz,在TS101S中進(jìn)行第二級(jí)DDC處理,同時(shí)實(shí)現(xiàn)四路軟件DDC,最終輸出的信號(hào)帶寬為125Hz~3kHz。

本模塊采用多相濾波方式實(shí)現(xiàn)第二級(jí)DDC,每一路DDC分三級(jí)FIR濾波器。

當(dāng)FIR濾波器為r階,則轉(zhuǎn)移函數(shù)為:

利用多采樣率系統(tǒng)中結(jié)構(gòu)的等效變換原理,將濾波器多相分析分量與抽取操作進(jìn)行如圖3 所示的互換,這種互換對(duì)系統(tǒng)特性不做任何改變,卻大大減少了運(yùn)算量。運(yùn)用這種多相分解使濾波器的濾波操作運(yùn)算量減少到原來(lái)的1/M。

(5) 數(shù)據(jù)通訊

中頻處理模塊與主控計(jì)算機(jī)通過(guò)HOST接口通訊,通過(guò)TS101S的高速Link口將抽取的窄帶數(shù)據(jù)送入后端處理。

2 系統(tǒng)硬件電路設(shè)計(jì)

2.1 系統(tǒng)電源設(shè)計(jì)

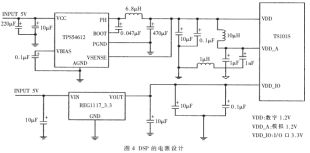

本模塊的電源共四種,分別為1.2V、2.5V、3V、3.3V。其中,為數(shù)字電路供電的有1.2V、3.3V、2.5V三種,為模擬電路供電的有1.2V和3V兩種。為了保證系統(tǒng)正常工作,模擬電路和數(shù)字電路的電源分別提供。

為了保證輸入“潔凈”的電源,在緊貼AD6652和TS101S的電源引腳處用兩個(gè)電容進(jìn)行高頻濾波;地分為數(shù)字地與模擬地,并通過(guò)一個(gè)磁珠單點(diǎn)連接。

TS101S要求核供電不能晚于I/O供電,故對(duì)TS101S核和I/O供電分別由兩個(gè)電源提供。TS101S供電設(shè)計(jì)如圖4所示。

2.2 時(shí)鐘設(shè)計(jì)

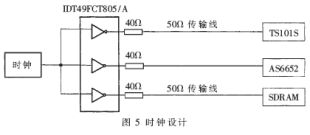

時(shí)鐘設(shè)計(jì)對(duì)于系統(tǒng)是十分重要的。本設(shè)計(jì)中使用同一個(gè)時(shí)鐘源,通過(guò)時(shí)鐘驅(qū)動(dòng)芯片IDT49FCT3805統(tǒng)一供給所有器件。時(shí)鐘線應(yīng)做到基本等長(zhǎng)且盡量短,并通過(guò)阻抗匹配,提供一個(gè)統(tǒng)一的時(shí)鐘基準(zhǔn),如圖5所示。

2.3 系統(tǒng)的復(fù)位設(shè)計(jì)

本系統(tǒng)中需要復(fù)位的有TS101S和AD6652,TS101S對(duì)復(fù)位的要求較高,其復(fù)位設(shè)計(jì)如下:

(1)上電復(fù)位

上電復(fù)位時(shí)序如圖6所示。

DSP要求上電且strap選項(xiàng)穩(wěn)定后,reset引腳必須保持至少2ms的低電平,然后產(chǎn)生高脈沖至少50個(gè)時(shí)鐘周期(最大100個(gè)時(shí)鐘周期),再次為低有效,要求維持至少100個(gè)時(shí)鐘周期。

(2)正常復(fù)位(上電穩(wěn)定后的熱復(fù)位)

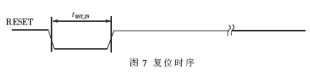

復(fù)位時(shí)序如圖7所示。

DSP的正常復(fù)位要求RESET引腳必須保持至少100個(gè)時(shí)鐘周期,strap選項(xiàng)穩(wěn)定后,RESET引腳必須保持至少2ms的低電平。

(3)對(duì)TS101S兩種復(fù)位的處理

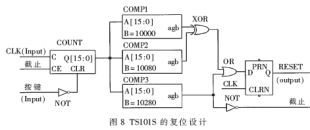

對(duì)上電復(fù)位采用CPLD來(lái)實(shí)現(xiàn),熱復(fù)位用按鍵人工復(fù)位,也在CPLD中一并配置實(shí)現(xiàn)。復(fù)位邏輯電路如圖8所示。

3 硬件設(shè)計(jì)時(shí)需注意的問(wèn)題

(1)高速PCB設(shè)計(jì)時(shí),如果時(shí)鐘信號(hào)不由外部提供,最好只使用一個(gè)時(shí)鐘源,驅(qū)動(dòng)后分配給各所需的部分。注意將時(shí)鐘驅(qū)動(dòng)芯片置于適當(dāng)位置,使輸出時(shí)鐘線基本等長(zhǎng)。時(shí)鐘芯片下應(yīng)大面積鋪地,并避免離信號(hào)線太近。

(2)電源輸入時(shí)應(yīng)加多個(gè)旁路電容,提高系統(tǒng)配電的質(zhì)量,降低共模射頻能量并進(jìn)行電源濾波。TS101S和AD6652接入電源前,需緊貼芯片在電源腳和地腳之間直接接去耦電容;芯片周圍布上電網(wǎng),以減少外界干擾。設(shè)計(jì)中應(yīng)區(qū)分?jǐn)?shù)字和模擬電路并分別供電,數(shù)字地和模擬地之間通過(guò)磁珠單點(diǎn)連接。這樣可以最大限度保障模擬電源不受污染,這是保證系統(tǒng)正常工作的重要條件。

(3)在TS101S電路中,對(duì)所有的輸入信號(hào)必須有明確的處理,不能懸浮或置之不理。

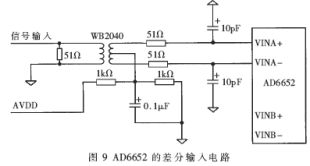

(4)對(duì)A/D 部件的設(shè)計(jì)必須保證其功能和性能的實(shí)現(xiàn)。AD6652可同時(shí)進(jìn)行兩路A/D 轉(zhuǎn)換,每個(gè)A/D通道模擬信號(hào)采用差分輸入,額定模擬輸入電壓的最大范圍的峰-峰值為1V。為了獲得較好的動(dòng)態(tài)性能,2個(gè)差分輸入端的阻抗必須匹配,常采用變壓器匹配的方法。AD6652的差分輸入電路如圖9所示。

(5)DSP指令周期為ns級(jí),因而DSP硬件系統(tǒng)中最易出現(xiàn)的問(wèn)題是高頻干擾,因此在制作DSP硬件系統(tǒng)的印制電路板(PCB)時(shí),應(yīng)特別注意對(duì)地址線和數(shù)據(jù)線等重要信號(hào)線的布線要做到正確合理。布線時(shí)盡量使高頻線短而粗,且遠(yuǎn)離易受干擾的信號(hào)線,如模擬信號(hào)線和時(shí)鐘線等。

經(jīng)過(guò)測(cè)試,該模塊實(shí)現(xiàn)了從寬帶數(shù)據(jù)流中同時(shí)提取四路窄帶中頻數(shù)字信號(hào)的功能。利用TS101S的Link口還可以方便地進(jìn)行模塊擴(kuò)展及板間互聯(lián),以適應(yīng)更復(fù)雜的系統(tǒng)。

參考文獻(xiàn)

1 ADSP-TS101S tigerSharc embedded processor datasheet.Analog Device Inc, 2004

2 ADSP-TS101S TigerSharc hardware reference.Analog Device Inc, 2004

3 12 bit 65MSPS IF to baseband deversity receiver AD6652 datasheet. Anglog Device Inc, 2004

4 楊小牛.軟件無(wú)線電原理與應(yīng)用,北京:電子工業(yè)出版社,2001

5 劉書明, 羅軍輝. TigerSHARC DSP應(yīng)用系統(tǒng)設(shè)計(jì).北京:電子工業(yè)出版社, 2004