0 引言

USB 總線(xiàn)因其具有高速度、即插即用、功耗低等特點(diǎn),深受廣大用戶(hù)的青睞。但USB 規(guī)范本身并未考慮數(shù)據(jù)傳輸時(shí)的安全性問(wèn)題,所以它的安全性能低,不適合用來(lái)傳輸安全性 要求較高的信息。本文在研究USB2.0 規(guī)范以及應(yīng)用密碼學(xué)等安全防護(hù)技術(shù)的基礎(chǔ)上,提出 一個(gè)基于ASIC 的整體解決方案。目的是用硬件描述語(yǔ)言設(shè)計(jì)一個(gè)既符合USB2.0 規(guī)范,同 時(shí)又可以將流經(jīng)該接口芯片的數(shù)據(jù)進(jìn)行自動(dòng)加密的專(zhuān)用集成電路。最后,對(duì)所設(shè)計(jì)的系統(tǒng)在 FPGA 上進(jìn)行驗(yàn)證,給出系統(tǒng)在FPGA 上所耗用的資源以及性能參數(shù),對(duì)得到的數(shù)據(jù)進(jìn)行分 析。

1 相關(guān)知識(shí)

1.1 USB 簡(jiǎn)介

從USB1.0 版本發(fā)布到2.0 版本,中間經(jīng)歷了多次版本更新。從1998 年7 月的Windows98 開(kāi)始,USB 外圍設(shè)備開(kāi)始陸續(xù)出現(xiàn),同時(shí)也成為最受歡迎的接口.它的優(yōu)點(diǎn)為:容易使用、傳輸速度快、低價(jià)位、低能耗、高穩(wěn)定性、操作系統(tǒng)支持、外圍設(shè)備的支持、有彈性.缺點(diǎn)為:缺乏對(duì)數(shù)據(jù)安全性的考慮、缺乏對(duì)舊硬件的支持、點(diǎn)對(duì)點(diǎn)的通信、速度的限制、距離的 限制、硬件的錯(cuò)誤或故障、協(xié)議的復(fù)雜性、版權(quán)費(fèi)。

1.2 AES 簡(jiǎn)介

1.2.1 原理及起源

AES(Advanced Encryption Standard)是由美國(guó)國(guó)家標(biāo)準(zhǔn)與技術(shù)研究所于1997 年提出征集該算法的公告并最終選定了兩個(gè)比利時(shí)研究者Vincent Rijmen 和Joan Daemen 發(fā)明的 Rijndael)算法,并于2001 年正式發(fā)布了AES 標(biāo)準(zhǔn)。

1.2.2 AES 工作流程

Rijndael 算法本質(zhì)上是一種對(duì)稱(chēng)分組密碼體制,采用代替/轉(zhuǎn)換網(wǎng)絡(luò),每輪由三層組成:線(xiàn)性混合層確保多輪之上的高度擴(kuò)散;非線(xiàn)性層由16 個(gè)S 盒并置起到混淆的作用;密鑰加 密層將子密鑰層異或到中間狀態(tài)。Rijndael 是一個(gè)迭代分組密碼,其分組長(zhǎng)度和密鑰長(zhǎng)度都 是可變的,只是為了滿(mǎn)足AES 的要求才限定處理的分組大小為128 位。而密鑰長(zhǎng)度為128 位、192 位或256 位,相應(yīng)的迭代輪數(shù)Nr 為10 輪、12 輪、14 輪。可以抵御強(qiáng)大和實(shí)時(shí)的攻擊。

2 系統(tǒng)解決方案

2.1 系統(tǒng)原理

本文主要目的是要設(shè)計(jì)一個(gè)既符合USB2.0 規(guī)范的數(shù)據(jù)接收和發(fā)送,又可以對(duì)接收到的數(shù)據(jù)進(jìn)行自動(dòng)加密的專(zhuān)用集成電路的設(shè)計(jì),并將所設(shè)計(jì)的系統(tǒng)用FPGA 對(duì)其進(jìn)行功能驗(yàn)證。

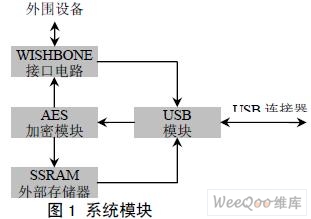

該系統(tǒng)由兩大模塊組成:USB 模塊和AES 加密模塊。 系統(tǒng)結(jié)構(gòu)如圖1 所示:

|

其中,USB 模塊實(shí)現(xiàn)流經(jīng)數(shù)據(jù)依照USB2.0 規(guī)范進(jìn)行接收和發(fā)送。將要發(fā)送的數(shù)據(jù)進(jìn)行裝配、 打包處理,并對(duì)接收到的數(shù)據(jù)包進(jìn)行分解,在存儲(chǔ)器接口與優(yōu)先級(jí)判別模塊的處理之后將數(shù) 據(jù)存入外部存儲(chǔ)器 (SSRAM)或通過(guò)WISHBONE 接口電路與外圍設(shè)備進(jìn)行通訊;AES 加密 模塊負(fù)責(zé)對(duì)接收到的數(shù)據(jù)進(jìn)行加密處理,密鑰封裝在芯片中的存儲(chǔ)器中。

2.1.1 USB 接口模塊原理

該模塊實(shí)現(xiàn)了符合USB2.0 規(guī)范的數(shù)據(jù)處理以及不同的外設(shè)與計(jì)算機(jī)的互連和數(shù)據(jù)通 信。 該模塊的主要功能包括:

(1) 完全支持 USB2.0 規(guī)范,提供全速模式和高速模式,其數(shù)據(jù)率分別為12Mbit/s 和 480Mbit/s。

(2) 支持 WISHBONE 接口電路和該模塊之間采用DMA 方式進(jìn)行數(shù)據(jù)通信。

(3) 模塊的掛起/恢復(fù)功能。 該模塊結(jié)構(gòu)如圖2 所示。其中。PHY 模塊負(fù)責(zé)將數(shù)據(jù)發(fā)送到與USB 連接器相連的計(jì)算 機(jī),或接收來(lái)自計(jì)算機(jī)的數(shù)據(jù);UTMI(數(shù)據(jù)通用收發(fā)宏單元接口)與PL(協(xié)議層)模塊及內(nèi)部 數(shù)據(jù)存儲(chǔ)器、控制寄存器相連負(fù)責(zé)保持通信數(shù)據(jù)的格式符合USB2.0 規(guī)范中的協(xié)議格式; WISHBONE(主接口電路)是內(nèi)部數(shù)據(jù)存儲(chǔ)器、控制寄存器與外部設(shè)備之間的通信橋梁。

2.1.2 AES 模塊原理

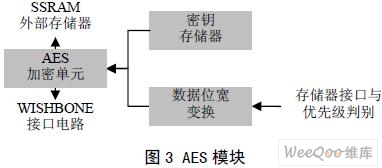

該模塊負(fù)責(zé)將USB 模塊接收并解包的數(shù)據(jù)進(jìn)行加密然后將加密后的數(shù)據(jù)存入外部存儲(chǔ)器或通過(guò)WISHBONE 接口電路送到外圍設(shè)備中。

該模塊結(jié)構(gòu)圖如圖3 所示。它主要包括數(shù)據(jù)位寬變換模塊和AES 加密單元。在USB 模 塊數(shù)據(jù)接收和處理的位寬為8,而AES 加密模塊中,明文和密鑰的位寬為128,所以在USB 模塊將接收來(lái)的數(shù)據(jù)包解包后所獲得的數(shù)據(jù)不能直接加密,需要進(jìn)行位寬調(diào)整后才可以加 密。數(shù)據(jù)位寬變換模塊的功能就是將PL 解包后的8 位數(shù)據(jù)連接成128 位后再送入AES 加密 單元;AES 加密單元將送入的128 位明文與密鑰存儲(chǔ)器中的密鑰進(jìn)行十輪AddRoundkey、 SubBytes、ShiftRows、MixColumns 變換后完成明文加密,并將加密后的數(shù)據(jù)(密文)送入外 部存儲(chǔ)器或通過(guò)WISHBONE 接口電路送到外圍設(shè)備中。

2.2 性能分析

本文采用Stratix 系列的EP1S10F484C5 芯片對(duì)該系統(tǒng)進(jìn)行驗(yàn)證。

2.2.1 USB2.0 模塊的性能分析

下表為USB 模塊綜合后的性能參數(shù):

2.2.2 AES 模塊的性能分析

當(dāng)輸入信息={32 43 f6 a8 88 5a 30 8d 31 31 98 a2 e0 37 07 34},輪數(shù)Nr=10,加 密密鑰={2b 7e 15 16 28 ae d2 a6 ab f7 15 88 09 cf 4f 3c},加密結(jié)果={39 25 84 1d 02 dc 09 fb dc 11 85 97 19 6a 0b 32},經(jīng)檢驗(yàn)該結(jié)果是正確的,完全符合AES 加密算法。

下表為AES 加密算法綜合后的數(shù)據(jù):

2.2.3 整個(gè)系統(tǒng)的性能分析

下表為系統(tǒng)綜合后的性能參數(shù):

由以上綜合結(jié)果分析可以得出,該系統(tǒng)在FPGA 上進(jìn)行驗(yàn)證是完全可行的,而且它的頻 率可以達(dá)到336.02MHz,完全可以實(shí)現(xiàn)USB480Mbits/s 的傳輸速度。

2.3 系統(tǒng)實(shí)施的必要性和可行性分析

該系統(tǒng)的主要目的是設(shè)計(jì)一個(gè)可以對(duì)數(shù)據(jù)進(jìn)行自動(dòng)加密的USB2.0 接口芯片,常規(guī)的USB 接口芯片是不帶加密功能的。而現(xiàn)今USB 的應(yīng)用領(lǐng)域中有很大一部分需要對(duì)所傳輸?shù)臄?shù)據(jù)進(jìn) 行加密。對(duì)安全性要求特別高,所以制作一個(gè)既符合USB2.0 規(guī)范,又可對(duì)數(shù)據(jù)進(jìn)行自動(dòng)加密 處理的專(zhuān)用集成電路在應(yīng)用上將會(huì)有很大的應(yīng)用空間.制作這樣的集成電路很有必要.

FPGA 是一種可重構(gòu)硬件,它既具有硬件的安全性和高速性又有軟件的靈活性和易維護(hù)性,已經(jīng)成為分組密碼算法硬件實(shí)現(xiàn)的熱點(diǎn)研究方向;另外FPGA 研發(fā)的啟動(dòng)開(kāi)銷(xiāo)比ASIC 要小,F(xiàn)PGA 從設(shè)計(jì)到投入市場(chǎng)的周期很短,F(xiàn)PGA 芯片重配置和擴(kuò)充十分方便,它能夠商定 所需的密碼算法,更換的密碼算法可以適時(shí)配置到目標(biāo)設(shè)備中。當(dāng)前,F(xiàn)PGA 芯片的容量不 斷的增大,片內(nèi)還有內(nèi)嵌存儲(chǔ)器,這就使查找表和變換操作可以很容易的實(shí)現(xiàn),因此在百萬(wàn) 門(mén)的FPGA 中實(shí)現(xiàn)本文所提系統(tǒng)是可行的。

3 系統(tǒng)優(yōu)勢(shì)分析

提高USB 數(shù)據(jù)通訊可靠性的措施基本上可以分為兩種:一種經(jīng)過(guò)計(jì)算機(jī)軟件處理,對(duì)數(shù) 據(jù)進(jìn)行加密;另一種方法是在硬件的層面上對(duì)數(shù)據(jù)直接加密。其中軟件處理實(shí)現(xiàn)起來(lái)較簡(jiǎn)單, 但軟件加密處理速度比硬件加密慢許多,如果需要對(duì)大量數(shù)據(jù)進(jìn)行實(shí)時(shí)加密,軟件處理將會(huì) 消耗太多的時(shí)間,不適合數(shù)據(jù)的實(shí)時(shí)加密和通訊。相反,用硬件的方法來(lái)解決,在速度方面 將獲得較理想的實(shí)時(shí)加密通訊的效果。

另外,由于加密算法中都大量使用了復(fù)雜的按位運(yùn)算,而通常這類(lèi)運(yùn)算不適合在通用處 理器上運(yùn)行,因此用軟件來(lái)實(shí)現(xiàn)必然會(huì)帶來(lái)效率低下的問(wèn)題,而加密芯片體系結(jié)構(gòu)是針對(duì)加 密算法的結(jié)構(gòu)特征專(zhuān)門(mén)設(shè)計(jì)的,采用了一些特殊的優(yōu)化技術(shù)(如流水線(xiàn)和查找表等),可以 極大地提高數(shù)據(jù)的流量并減少密鑰的生成時(shí)間;另外軟件只能提供有限的物理安全,尤其在 密鑰的存儲(chǔ)方面。而用硬件實(shí)現(xiàn)加密算法及與之相關(guān)的密鑰生成過(guò)程,并且封裝到芯片中, 因?yàn)樗鼈儾灰妆煌獠抗粽咦x取或更改,會(huì)有較高的物理安全性。因此基于硬件的密碼算法 就受到業(yè)界的普遍關(guān)注,可以完全勝任整個(gè)系統(tǒng)的安全保密工作。

由以上分析可知,該系統(tǒng)采用硬件處理加密和USB 通訊,可以在滿(mǎn)足USB2.0 規(guī)范的數(shù) 據(jù)傳輸?shù)幕A(chǔ)上,極大地提高系統(tǒng)的安全性。

4 結(jié)論

綜上所述, 通過(guò)研究對(duì)USB 通訊安全性的需求,開(kāi)發(fā)一個(gè)具有數(shù)據(jù)實(shí)時(shí)自動(dòng)加密的USB 設(shè)備控制器可以開(kāi)創(chuàng)USB 安全通信的新領(lǐng)域,而且,現(xiàn)在市面上大多數(shù)器件的外圍接口的都 支持USB,如果可以開(kāi)發(fā)一塊保密性高而又不影響原有USB 通訊高速率、簡(jiǎn)單易用的芯片將 會(huì)受到廣大用戶(hù)的青睞.