??? 摘 要: 簡要介紹了CPU通用寄存器" title="通用寄存器">通用寄存器及窗口技術(shù)" title="窗口技術(shù)">窗口技術(shù)的產(chǎn)生和發(fā)展背景,提出了以CALL和RETURN為代表的指令存在的問題,并給出了解決方法,討論了大寄存器集及窗口技術(shù)的缺點(diǎn)和一些相關(guān)應(yīng)用。

??? 關(guān)鍵詞: 寄存器? RISC? MIPS? 重疊寄存器窗口技術(shù)? CPU

?

??? CPU的通用寄存器是數(shù)據(jù)存儲(chǔ)體系的最內(nèi)層。寄存器操作避免了內(nèi)存地址計(jì)算,其訪問時(shí)間遠(yuǎn)小于Cache和主存。RISC MPU都具有較CISC大的寄存器集(Register file),而且都是LOAD/STORE體系結(jié)構(gòu),即所有運(yùn)算的操作數(shù)都只針對(duì)寄存器中的數(shù)據(jù)施行,僅用LOAD/STORE類指令訪問內(nèi)存。從RISC CPU高速處理時(shí)間(單周期執(zhí)行指令)的角度來看,這些主存訪問是非常昂貴的開銷。為了減少LOAD/STORE操作,使CPU與內(nèi)存間的通訊量最小,不同的RISC體系結(jié)構(gòu)采用了不同的寄存器集設(shè)計(jì)。從RISC早期開創(chuàng)性研究開始,就存在著兩種不同的風(fēng)格。

??? (1)Berkeley風(fēng)格:在美國加州大學(xué)伯克利分校RISC I(1981)和RISC II(1983)項(xiàng)目中,CPU采用100個(gè)以上的寄存器,組成相互重疊的多寄存器窗口,用這種硬件結(jié)構(gòu)實(shí)現(xiàn)寄存器的高效率使用。SUN SPARC是這種風(fēng)格體系結(jié)構(gòu)的典型范例。

??? (2)IBM/Stanford風(fēng)格:在IBM 801(1975~1982)和斯坦福大學(xué)MIPS(1981~l983)項(xiàng)目中,體系結(jié)構(gòu)設(shè)計(jì)人員(包括編譯軟件專家)采用非常高級(jí)、復(fù)雜的優(yōu)化編譯算法實(shí)現(xiàn)對(duì)寄存器的最佳分配。目前在這類設(shè)計(jì)中,以MIPS的優(yōu)化編譯軟件及其配套的RISC R3000 CPU芯片最為典型,功能最強(qiáng),發(fā)展最成熟。MIPS是高效精簡指令集計(jì)算機(jī)(RISC)體系結(jié)構(gòu)中最優(yōu)雅的一種,即使是MIPS的競爭對(duì)手也這樣認(rèn)為。這可以從MIPS對(duì)于后來研制的新型體系結(jié)構(gòu),如DEC的Alpha和HP的Precision產(chǎn)生的強(qiáng)烈影響看出來。雖然自身的優(yōu)雅設(shè)計(jì)并不能保證在充滿競爭的市場上長盛不衰,但是MIPS微處理器卻經(jīng)常能在處理器的每個(gè)技術(shù)發(fā)展階段保持速度最快的同時(shí)保持設(shè)計(jì)的簡潔。

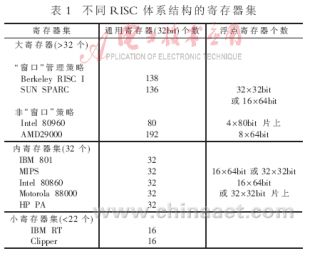

??? 表1列出了不同RISC體系結(jié)構(gòu)的寄存器集的寄存器個(gè)數(shù),包括通用寄存器個(gè)數(shù)及浮點(diǎn)寄存器個(gè)數(shù)。

?????????????????????????

1 寄存器窗口技術(shù)

??? RISC的指令系統(tǒng)比較簡單,CISC中的一條復(fù)雜指令,在RISC中通常要用一段子程序" title="子程序">子程序來實(shí)現(xiàn)。因此,RISC程序中的CALL和RETURN的子程序指令要比CISC程序中多。為了使CALL和RETURN操作盡量少地訪問存儲(chǔ)器,美國加洲大學(xué)伯克利分校的F.Baskett提出重疊寄存器窗口(Overlapping Register Window)技術(shù),并且首先在RISC I上應(yīng)用。重疊寄存器窗口的基本思想基于在處理機(jī)中設(shè)置一個(gè)數(shù)量比較大的寄存器堆,并把它劃分成多個(gè)窗口。在RISC II中,寄存器的數(shù)量增加到138個(gè)。目前,重疊寄存器窗口技術(shù)已經(jīng)成為RISC的一種基本技術(shù)。

??? RISC技術(shù)的主要設(shè)計(jì)技巧為:短周期時(shí)間;單周期執(zhí)行指令;LOAD/STORE結(jié)構(gòu);簡單固定格式的指令系統(tǒng);不用微碼技術(shù);大寄存器堆;哈佛(Harvard)總線結(jié)構(gòu);高效的流水線操作;延遲轉(zhuǎn)移;硬連線控制;重疊寄存器窗口技術(shù);優(yōu)化編譯程序" title="編譯程序">編譯程序;增強(qiáng)存儲(chǔ)管理功能;面向高級(jí)語言。

2 存在的問題

??? 指令執(zhí)行過程中,某些指令占據(jù)與其自身在程序中所占比例不相稱的大量訪存信息量。這一點(diǎn),在CALL和RETURN指令上表現(xiàn)最為明顯。

??? 在執(zhí)行CALL指令時(shí),必須把硬件現(xiàn)場(主要包括程序計(jì)數(shù)器和處理機(jī)狀態(tài)字)和程序本身的軟件現(xiàn)場(主要指在子程序中要使用的通用寄存器等)保存到主存儲(chǔ)器中。另外,還要把執(zhí)行子程序所需要的參數(shù)從主程序傳送過去。在執(zhí)行RETURN指令時(shí),要做相反的工作,最后把運(yùn)算結(jié)果傳送回主程序。因此,執(zhí)行CALL和RETURN指令時(shí),訪問存儲(chǔ)器的信息量非常大。據(jù)統(tǒng)計(jì),在PASCAL語言和C語言中分別有15%和12%的CALL和RETURN指令,而它們?cè)L問存儲(chǔ)器的信息量卻占整個(gè)訪存信息量的44%和45%。

3 問題解決

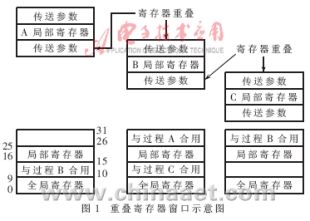

??? 重疊寄存器窗口的基本思想:在處理機(jī)中設(shè)置一個(gè)數(shù)量比較大的寄存器堆,并把它劃分成很多個(gè)窗口。每個(gè)過程使用其中相鄰的三個(gè)窗口和一個(gè)公共窗口,而在這些窗口中有一個(gè)窗口是與前一個(gè)過程共用,還有一個(gè)窗口是與下一個(gè)過程共用的。與前一過程共用的窗口可以用來存放前一過程傳送給本過程的參數(shù),同時(shí)也存放本過程傳送給前一過程的計(jì)算結(jié)果。同樣,與下一過程共用窗口可以用來存放本過程傳送給下一過程的參數(shù)和存放下一過程傳送給本過程的計(jì)算結(jié)果。圖1表現(xiàn)了重疊寄存器窗口的基本思想。

??????????????????????????

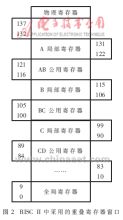

??? 圖2是RISC II中采用的重疊寄存器窗口,共有138個(gè)寄存器,分成17個(gè)窗口。其中,有一個(gè)由10個(gè)寄存器組成的窗口是全局窗口,能被所有過程訪問;另外有8個(gè)窗口,每個(gè)窗口各10個(gè)寄存器,分別作為8個(gè)過程的局部寄存器;還有8個(gè)窗口,每個(gè)窗口各有6個(gè)寄存器,是相鄰兩個(gè)過程公用的,稱為重疊寄存器窗口。每個(gè)過程均可以訪問32個(gè)寄存器,其中,有10個(gè)是所有過程公用的全局寄存器,有10個(gè)是只供本過程使用的局部寄存器,有6個(gè)是與上一過程公用的寄存器,還有6個(gè)是與下一過程公用的寄存器。

?????????????????????????????????? ?????? ?????

?????

??? 只要調(diào)用的深度不超過規(guī)定的層數(shù)(如8層),重疊寄存器窗口技術(shù)可以減少大量的訪存操作。當(dāng)調(diào)用層數(shù)超過規(guī)定層數(shù)時(shí),稱為寄存器溢出,這時(shí),可以在主存中開辟一個(gè)堆棧,把超過規(guī)定層數(shù)的寄存器中的內(nèi)容壓入堆棧中。

??? 在SUN公司的SPARC處理機(jī)以及后來的Super SPARC和Utra SPARC處理機(jī)中,還把最后一個(gè)過程的公用寄存器與第一個(gè)過程的公用寄存器重疊起來,形成一個(gè)循環(huán)圈。在調(diào)用層數(shù)很多時(shí),可以循環(huán)使用。

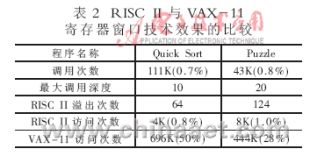

??? F.Baskett等人使用Quick sort和Puzzle兩個(gè)程序?qū)拇嫫鞔翱诩夹g(shù)的有效性進(jìn)行了測試。Quick sort程序的特點(diǎn)是過程調(diào)用的次數(shù)在整個(gè)程序中所占的比例比較大,但調(diào)用的深度不大;而Puzzle程序正好相反。RISC II與VAX-11兩種機(jī)器的比較結(jié)果如表2所示。RISC II的訪存次數(shù)主要是寄存器窗口溢出引起的,而VAX-11訪存次數(shù)是為了保持和恢復(fù)通用寄存器中內(nèi)容而引起的。從表2可以看出,RISC II寄存器溢出的次數(shù)很少,只占千分之一左右,影響也不大。由于采用了寄存器窗口技術(shù),由程序調(diào)用引起的訪問存儲(chǔ)器次數(shù)只占程序總訪存次數(shù)的1%左右。

??????????????????????

4 開銷比較

??? 表3是RISC II處理機(jī)與幾種CISC處理機(jī)的每次過程調(diào)用的開銷比較。從表3可以看出,在執(zhí)行時(shí)間、執(zhí)行指令條數(shù)、訪問存儲(chǔ)器次數(shù)等方面,采用重疊寄存器窗口技術(shù)都十分有效。

????????????????????????

5 大寄存器集及窗口技術(shù)的缺點(diǎn)

??? 大寄存器集及窗口技術(shù)在有效支持高級(jí)語言過程調(diào)用結(jié)構(gòu)的同時(shí),也不可避免地出現(xiàn)了一些缺點(diǎn):

??? (1)窗口策略只是在比較理想的情況下,即嵌套深度在滿足一定限制的時(shí)候才非常有效。

??? (2)對(duì)關(guān)聯(lián)轉(zhuǎn)換(Context Switch)時(shí)需將CPU寄存器存入內(nèi)存的系統(tǒng)來說,大寄存器集的Save/Restore 需較長的時(shí)間才能完成,這直接影響多任務(wù)轉(zhuǎn)換和中斷響應(yīng)時(shí)系統(tǒng)的響應(yīng)速度, 而這對(duì)多用戶系統(tǒng)和實(shí)時(shí)控制是非常關(guān)鍵的。

??? (3)對(duì)于采用流水線的結(jié)構(gòu)處理器來說,指令譯碼是非常關(guān)鍵的一個(gè)功能段。RSIC MPU獲得高處理速度的一個(gè)重要原因就是其極簡單的指令格式、指令集和尋址方式帶來了極快的指令譯碼時(shí)間。但采用大寄存器及窗口結(jié)構(gòu)后就需要在指令譯碼通路中增加電路進(jìn)行寄存器地址的譯碼,如選擇當(dāng)前窗口及窗口移動(dòng)。特別是窗口指針需要計(jì)算,更增加了寄存器地址的譯碼時(shí)間,而且寄存器集越大,寄存器地址譯碼硬件也越復(fù)雜,對(duì)每一個(gè)寄存器的訪問時(shí)間也越長,由此在指令流水線譯碼段內(nèi)引起的時(shí)間延遲對(duì)系統(tǒng)整體性能的影響也越大(如目前采用寄存器窗口的體系結(jié)構(gòu)都很難實(shí)現(xiàn)快速LOAD/STORE指令,需要兩個(gè)或更多的周期)。若像SPARC那樣窗口大小固定,則所需譯碼和加法器電路還較簡單,由此引起的附加延遲也較小,系統(tǒng)性能所受影響也不大(但另一方面窗口較大和窗口個(gè)數(shù)較少,使窗口上溢" title="上溢">上溢次數(shù)和每次上溢后所需保存寄存器的數(shù)目都增加了)。

??? 若像AMD29000那樣采用可變大小的寄存器窗口, 則對(duì)于把窗口上溢次數(shù)和上溢后需要保存寄存器的個(gè)數(shù)減至最少非常有利,但卻必須在指令譯碼通路中采用更復(fù)雜的電路,這最終可能導(dǎo)致指令譯碼時(shí)間成為制約處理器芯片采用更高時(shí)鐘頻率的瓶頸。

??? (4)大寄存器集及窗口結(jié)構(gòu)需占用較大的CPU芯片面積,限制在片上實(shí)現(xiàn)其他關(guān)鍵硬件。

6 當(dāng)前寄存器窗口技術(shù)的一些應(yīng)用

??? 高效的函數(shù)調(diào)用:大多數(shù)RSIC處理器的函數(shù)調(diào)用需要卸出和重新裝入寄存器,開銷很大。IA-64增加了一個(gè)通用寄存器窗來支持高效的函數(shù)調(diào)用。這個(gè)128項(xiàng)的通用寄存器窗口被分為一個(gè)32項(xiàng)的全程存儲(chǔ)器和一個(gè)96項(xiàng)的堆棧存儲(chǔ)器。IA-64允許編譯程序在被調(diào)用的函數(shù)過程入口設(shè)置一條ALLOC指令,創(chuàng)立一個(gè)最多包含96項(xiàng)的新寄存器堆棧;在返回時(shí),恢復(fù)調(diào)用程序的寄存器堆棧幀。對(duì)編譯程序來說,似乎有長度無限的物理寄存器堆棧,從而降低了函數(shù)調(diào)用的開支、提高了效率;如果在調(diào)用和返回時(shí),沒有足夠的寄存器可供使用(堆棧溢出),則處理器將被阻塞,等待卸出和裝入寄存器,直到有足夠的寄存器為止。

參考文獻(xiàn)

[1] 白中英,楊旭東.計(jì)算機(jī)系統(tǒng)結(jié)構(gòu)(第2版).北京:科學(xué)出版社,2004.

[2] 鄭緯民,湯志忠.計(jì)算機(jī)組成原理.北京:清華大學(xué)出版社,2004.

[3] 張晨曦.計(jì)算機(jī)體系結(jié)構(gòu).北京:高等教育出版社,2003.

[4] Dominic Sweetman.MIPS處理器設(shè)計(jì)透視See MIPS Run.北京:北京航空航天大學(xué)出版社,2005.