作者: Albert Yen 混合模式與射頻技術(shù)經(jīng)理 臺(tái)聯(lián)電

Lawrence Williams 商業(yè)開發(fā)總監(jiān) Z.Y. Daniel Wu 模擬/混合信號(hào)IC專家 Ansoft公司

大規(guī)模射頻集成電路,如無線收發(fā)系統(tǒng),往往包含了模擬和數(shù)字部分(如壓控振蕩器(VCO)、鎖相環(huán)(PLL)、混頻器、濾波器、放大器、數(shù)模/模數(shù)轉(zhuǎn)換器(DAC/ADC)等)。這些器件的各種功能特性需要在時(shí)域和頻域內(nèi)進(jìn)行仿真,以得到它們各自的行為特性。

此外,這些系統(tǒng)工作在GHz的頻率段,采用先進(jìn)信號(hào)產(chǎn)生方法(如正交頻分復(fù)用(OFDM)和快速跳頻技術(shù)等)。高頻電路的開關(guān)速度很快,對(duì)有源與無源器件的模型、電路版圖的寄生效應(yīng)、介質(zhì)耦合效應(yīng)、級(jí)間阻抗匹配、IC封裝和電源噪聲等非常敏感。

仿真挑戰(zhàn)

諧波失真、增益壓縮、振蕩器相位噪聲及混頻器噪聲系數(shù)等非線性效應(yīng)經(jīng)常在頻域進(jìn)行仿真和報(bào)告。而開關(guān)行為、電路初始啟動(dòng)狀態(tài)以及收發(fā)系統(tǒng)對(duì)瞬時(shí)事件(如跳頻)的響應(yīng)需要在時(shí)域進(jìn)行仿真。由于經(jīng)常需要包含基于頻域定義的寬帶寄生效應(yīng)建模,而這種建模必須進(jìn)行轉(zhuǎn)換以用于基于時(shí)間的仿真,因此導(dǎo)致時(shí)域分析復(fù)雜化。

很明顯,同時(shí)支持在時(shí)域和頻域內(nèi)進(jìn)行一致的仿真,并能高效和精確地對(duì)基于頻率的模型實(shí)現(xiàn)暫態(tài)分析的技術(shù),對(duì)于現(xiàn)在的RF電路仿真和驗(yàn)證至關(guān)重要。

為了組成一個(gè)完整的收發(fā)器或接收器鏈,由許多無線電單元組合在一起產(chǎn)生的電路包含非常多的器件數(shù)量,這通常超過了傳統(tǒng)EDA工具的極限,從而產(chǎn)生了另外一個(gè)仿真挑戰(zhàn)。

這迫使設(shè)計(jì)師引入人為的、不準(zhǔn)確的設(shè)計(jì)分割,從而犧牲了他們驗(yàn)證的寬度。因此,迫切需要新的技術(shù),它不僅要能在對(duì)敏感的模擬電路模塊仿真時(shí)具有良好的仿真精度和收斂性,同時(shí),由于在系統(tǒng)級(jí)芯片(SoC)設(shè)計(jì)中,電路中經(jīng)常包含了大量的晶體管和寄生元件,新的技術(shù)還必須具備處理這種電路的能力和必要的仿真速度。

解決挑戰(zhàn)

為解決這些仿真挑戰(zhàn),Ansoft公司開發(fā)了Nexxim。利用專用的數(shù)值算法和先進(jìn)的軟件架構(gòu),Nexxim成功地展示了解決大型電路問題的能力,能提供具有一致結(jié)果的時(shí)間和頻率分析,以及與Ansoft公司的寄生行為3D電磁建模的協(xié)同仿真能力。

新的設(shè)計(jì)技術(shù)利用高可靠性的高頻結(jié)構(gòu)仿真器(HFSS)對(duì)部件和版圖電磁寄生效應(yīng)進(jìn)行抽取,結(jié)合了用于高性能電路仿真的Nexxim,為SoC設(shè)計(jì)者們一次流片成功提供了新的手段和機(jī)會(huì)。

復(fù)雜SoC的設(shè)計(jì)需要完善的EDA設(shè)計(jì)流程。Cadence Virtuoso模擬設(shè)計(jì)環(huán)境(ADE)在模擬/RF設(shè)計(jì)業(yè)界得到廣泛使用。現(xiàn)在,可以將Nexxim仿真和HFSS模型抽取工具固有的優(yōu)勢(shì)整合到這個(gè)設(shè)計(jì)流程中。像ADC、AGC和PLL這樣的IC功能現(xiàn)在可以通過Cadence環(huán)境來創(chuàng)建,在單個(gè)芯片中集成,使用Nexxim按SPICE級(jí)別精度對(duì)這些功能模塊驗(yàn)證。

此外,HFSS與Cadence的設(shè)計(jì)流程協(xié)同工作,以提供可擴(kuò)展的片上無源模型、全波互連與介質(zhì)耦合寄生效應(yīng)抽取以及復(fù)雜的封裝模型抽取。

本文描述在建立好的設(shè)計(jì)流程中設(shè)計(jì)與驗(yàn)證射頻及模擬電路的新技術(shù)。本文以正在開發(fā)中的超寬帶(UWB" title="UWB">UWB)多波段正交頻分復(fù)用(MB-OFDM)無線系統(tǒng)項(xiàng)目為實(shí)例,演示新的技術(shù)。

下圖是一個(gè)流程圖,描述了典型的RFIC" title="RFIC">RFIC設(shè)計(jì)流程.

圖1:RFIC設(shè)計(jì)和驗(yàn)證流程

設(shè)計(jì)流程解決方案

設(shè)計(jì)過程從系統(tǒng)設(shè)計(jì)與行為級(jí)建模測(cè)試平臺(tái)開發(fā)開始。常用的建模方法包括使用Matlab、高級(jí)語言(如C語言)或者硬件描述語言(HDL)(如Verilog-A或VHDL-AMS),以及專門的系統(tǒng)仿真工具。

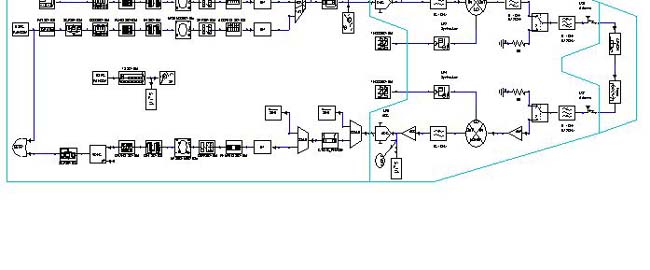

圖2描述了一個(gè)超寬帶IC參考設(shè)計(jì)的行為模塊框圖,這個(gè)IC參考設(shè)計(jì)是由Ansoft公司和領(lǐng)先的RFIC晶元廠臺(tái)聯(lián)電聯(lián)合開發(fā)的。這個(gè)系統(tǒng)包括基帶數(shù)字信號(hào)處理(DSP)、數(shù)據(jù)轉(zhuǎn)換器、無線發(fā)射器和接收器以及無線信道。然后開發(fā)出電路模塊規(guī)范來定義性能指標(biāo)。

圖2:用于早期系統(tǒng)級(jí)折衷研究的UWB無線電全收發(fā)器行為模型

Ansoft公司的Designer工具用來對(duì)這種UMB無線電進(jìn)行行為建模。它提供無線電模塊的非常全面的模型,如混頻器、濾波器、放大器、無線信道模型以及天線和DSP、混合信號(hào)模塊(如快速傅立葉變換FFT)、數(shù)據(jù)轉(zhuǎn)換器、符號(hào)映射器、隨機(jī)碼信號(hào)源和檢波器。

與Matlab模型的協(xié)同仿真和使用標(biāo)準(zhǔn)C編程的用戶定義模塊解決了特定的基帶信號(hào)處理,包括數(shù)據(jù)擾碼、卷積編碼、信號(hào)打孔、符號(hào)映射以及OFDM符號(hào)生成。

設(shè)計(jì)流程的下一步是使用理想化的互連結(jié)構(gòu)和代工設(shè)計(jì)工具包(foundry design kit)中的器件模型進(jìn)行電路設(shè)計(jì)。Nexxim仿真器可以和Cadence的RFIC設(shè)計(jì)流程完全集成在一起。

圖3顯示了它已經(jīng)緊密地與Cadence ADE集成并直接包含在其菜單結(jié)構(gòu)內(nèi)。

圖3:Ansoft Nexxim電路仿真器被完全整合到Cadence的ADE中

Nexxim能夠在一個(gè)仿真器中實(shí)現(xiàn)瞬態(tài)和諧波平衡,這可以從下面的例子中明顯地看出。

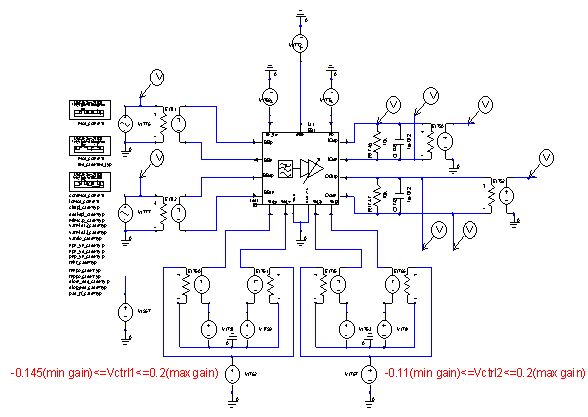

圖4是UWB接收器模擬基帶的原理圖,包括基帶濾波器和用于自動(dòng)增益控制(AGC)的可變?cè)鲆娣糯笃鳌?nbsp;

圖4:UWB接收器模擬基帶包括基帶濾波器和可變?cè)鲆鍭GC放大器

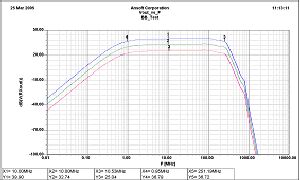

圖5提供了這種電路的典型頻域結(jié)果,包括采用線性網(wǎng)絡(luò)分析的掃頻結(jié)果、使用Nexxim諧波平衡分析的諧波失真結(jié)果以及增益壓縮。

圖5:基帶電路頻域結(jié)果實(shí)例(a) 不同增益狀態(tài)的掃頻響應(yīng);

圖5: 基帶電路頻域結(jié)果實(shí)例(b) 諧波平衡仿真報(bào)告的諧波失真;

圖5: 基帶電路頻域結(jié)果實(shí)例(c) 諧波平衡計(jì)算的增益壓縮圖

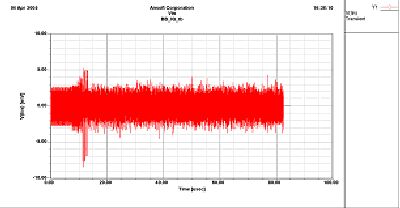

圖7所示為同一電路典型的時(shí)域仿真結(jié)果,包括復(fù)雜OFDM輸入波形以及單個(gè)UWB幀的I/Q通道輸出響應(yīng)。單個(gè)工藝設(shè)計(jì)包(臺(tái)聯(lián)電的0.13um工藝)以及相應(yīng)的設(shè)計(jì)環(huán)境能夠使設(shè)計(jì)者根據(jù)自己的需要選擇想要的仿真算法。

圖6:基帶電路的時(shí)域結(jié)果實(shí)例(a) 使用PWL源的OFDM數(shù)字調(diào)制輸入波形;

圖6:基帶電路的時(shí)域結(jié)果實(shí)例(b) Nexxim預(yù)測(cè)的I與Q輸出

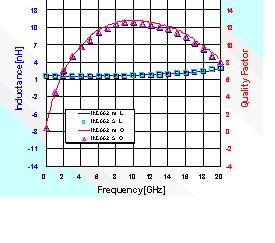

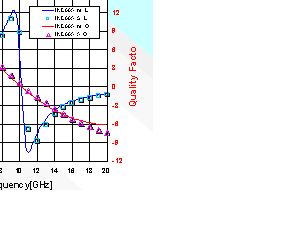

為了改進(jìn)仿真的精確度,對(duì)片上無源元件(如螺旋電感和金屬-氧化物-金屬(MoM)電容)進(jìn)行綜合、參數(shù)抽取并加入電路仿真中。臺(tái)聯(lián)電和Ansoft已經(jīng)實(shí)現(xiàn)了一種電磁設(shè)計(jì)方法(EMDM),這種方法采用全波三維仿真工具來建立片上無源器件的模型,其精度可以追溯到晶元制造工藝。對(duì)于螺旋電感,電感值和品質(zhì)因素(Q)可利用先進(jìn)的全波有限元仿真,通過Ansoft的HFSS來計(jì)算。

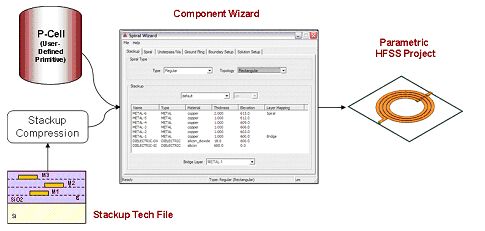

為方便電路設(shè)計(jì)工程師們使用全三維電磁場(chǎng)工具,Ansoft創(chuàng)建了一種針對(duì)臺(tái)聯(lián)電的器件向?qū)?Component Wizard),用于建立與他們的代工設(shè)計(jì)工藝相匹配的參數(shù)化模型。圖8描述了Component Wizard以及臺(tái)聯(lián)電使用的工藝,可以創(chuàng)建易于解決的參數(shù)化HFSS項(xiàng)目。

圖7:組件向?qū)髯x取UMC工藝技術(shù)文檔和P-cell以創(chuàng)建易于解決的參數(shù)化HFSS項(xiàng)目

器件向?qū)褂肅adence版圖P-cell與層堆疊技術(shù)文件,來在HFSS中創(chuàng)建完全參數(shù)化的螺旋電感參數(shù)庫。這個(gè)庫可以作為經(jīng)過驗(yàn)證的EMDM設(shè)計(jì)工具包提供給臺(tái)聯(lián)電客戶。還提供了一種將優(yōu)化設(shè)計(jì)反向標(biāo)注回通用的版圖工具的方法。

圖8比較了HFSS仿真結(jié)果與兩個(gè)環(huán)形螺旋電感的測(cè)量結(jié)果,顯示了電感量和品質(zhì)因素優(yōu)秀的一致性。

圖8:環(huán)形螺旋電感的HFSS仿真與測(cè)量的電感值和Q的比較(a) 150um外部直徑;

圖8:環(huán)形螺旋電感的HFSS仿真與測(cè)量的電感值和Q的比較(b) 300um外部直徑

物理電路版圖設(shè)計(jì)

設(shè)計(jì)過程的下一步是電路版圖生成。對(duì)關(guān)鍵的模擬模塊需要特別加以注意,這些模擬電路模塊通常是通過手動(dòng)布線來確保高度敏感的模擬電路滿足技術(shù)指標(biāo)要求。在版圖設(shè)計(jì)完成后,應(yīng)該利用電磁仿真來得到無源器件模型和互連之間的相互影響。

由于像HFSS這樣的仿真工具和運(yùn)算平臺(tái)的性能不斷提高,因此現(xiàn)在可以在關(guān)鍵的無線電模塊的整個(gè)版圖上使用三維仿真。其優(yōu)勢(shì)是這種精確的方法能夠仿真所有的高頻版圖設(shè)計(jì)效應(yīng),包括片上電感、互連、片上無源器件以及到其它互連結(jié)構(gòu)的耦合和介質(zhì)耦合。并且對(duì)寄生現(xiàn)象和耦合效應(yīng)不做任何假設(shè)和近似。對(duì)于整個(gè)模塊嚴(yán)格的電磁參數(shù)抽取能夠消除關(guān)于該包含哪個(gè)寄生效應(yīng)的所有不確定因素。

圖9描述了整個(gè)VCO模塊版圖的HFSS仿真項(xiàng)目,不包括所有的有源組件和MoM電容。在雙處理器PC上僅僅用9個(gè)多小時(shí)的時(shí)間就解決了這個(gè)142端口HFSS項(xiàng)目,需要2.15GB的內(nèi)存。

圖9:在HFSS中仿真的關(guān)鍵VCO電路版圖幾何尺寸

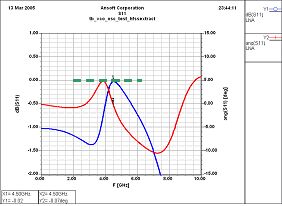

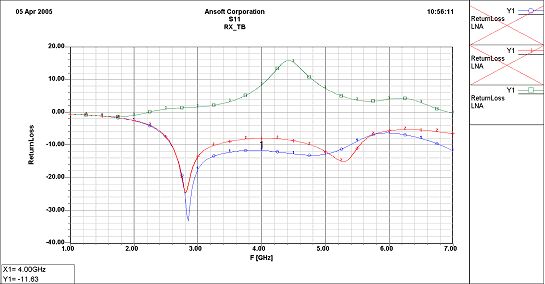

圖10顯示了VCO負(fù)阻振蕩器S11幅度(藍(lán)色)和相位(紅色),圖中表明當(dāng)提取了整個(gè)模塊的寄生效應(yīng),并將其加入到電路仿真中以后,器件無法起振。如果不進(jìn)行電磁場(chǎng)仿真,這樣的問題只有在出帶、制造和測(cè)試之后才能發(fā)現(xiàn)。這一級(jí)別的版圖提取和驗(yàn)證對(duì)于確保一次性流片成功來說非常重要。

圖10:VCO負(fù)阻振蕩器S11幅度(藍(lán)色)和相位(紅色)位圖,S11必須位于綠色虛線之上,器件才能振蕩(a) 沒有進(jìn)行整板仿真時(shí),電路振蕩于4.4GHz;

圖10:VCO負(fù)阻振蕩器S11幅度(藍(lán)色)和相位(紅色)位圖,S11必須位于綠色虛線之上,器件才能振蕩(b) 整板仿真之后包含了寄生效應(yīng),器件無法起振

管理封裝寄生效應(yīng)

在電路仿真中加入封裝寄生效應(yīng)是設(shè)計(jì)過程中的另外一個(gè)關(guān)鍵步驟,在射頻段,即使是很小的引線電感也會(huì)對(duì)電路性能產(chǎn)生顯著的影響。

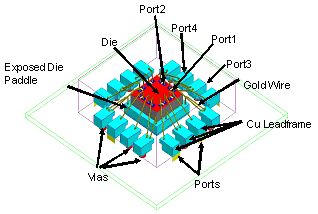

圖11中所示是一個(gè)QFN封裝的HFSS模型,通過仿真我們可以得到所有管腳的S參數(shù)矩陣并進(jìn)一步計(jì)算得到所有引線電感。

圖11:QFN IC封裝模型(a) 在HFSS中建立的仿真模型;

圖11:QFN IC封裝模型(b) 有限元網(wǎng)格剖分

圖12所示為在有和沒有接地及電源引線電感兩種情況下,圖13中的電路的小信號(hào)性能。

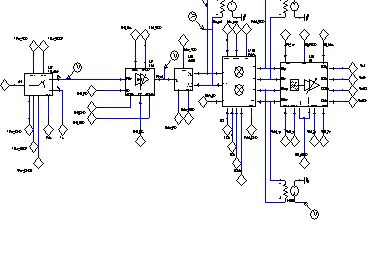

圖13:UWB接收器原理圖包括T/R開關(guān),可變?cè)鲆鍸NA,不平衡變壓器,I/Q解調(diào)器和基帶濾波/AGC

圖14:在考慮和不考慮接地及電源引線電感兩種情況下,圖13中的電路從LNA看進(jìn)去的輸入回波損耗。藍(lán)色曲線是不考慮接地及電源引線電感時(shí)的參考曲線;紅色曲線包括了T/R開關(guān)的接地及電源封裝引線電感;綠色曲線將T/R開關(guān)和LNA的接地及電源封裝引線電感全部包括在內(nèi),電路開始不穩(wěn)定

從這個(gè)圖中可以看出,從LNA看進(jìn)去的穩(wěn)定響應(yīng)(S11<0dB)決定于是否包括地和電源引線電感模型。在相同的仿真中可以觀察到LNA小信號(hào)增益由于地電感降低大約15dB。這個(gè)信息可以引導(dǎo)對(duì)設(shè)計(jì)的及時(shí)調(diào)整,這種調(diào)整反過來可以使電路穩(wěn)定。

驗(yàn)證平臺(tái)

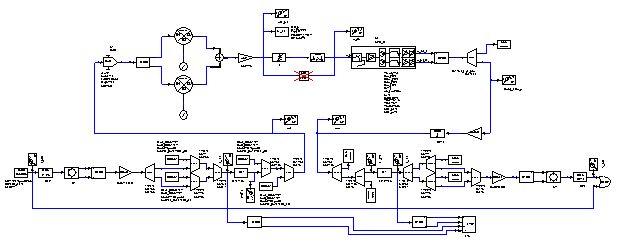

最后,具有多個(gè)功能模塊的晶體管級(jí)電路以及包含所有提取的寄生效應(yīng)的全芯片驗(yàn)證使用一種系統(tǒng)(行為級(jí))測(cè)試平臺(tái)來實(shí)現(xiàn)。圖15描述了全芯片驗(yàn)證系統(tǒng)測(cè)試平臺(tái)。MBOA位和幀的精確時(shí)域波形被自動(dòng)地連接到接收機(jī)電路的輸入。

圖15:在系統(tǒng)測(cè)試平臺(tái)上對(duì)無線收發(fā)系統(tǒng)進(jìn)行晶體管級(jí)全芯片驗(yàn)證

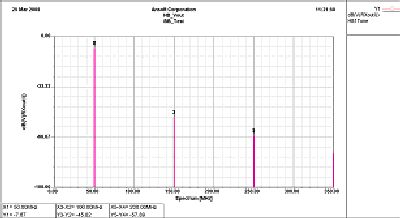

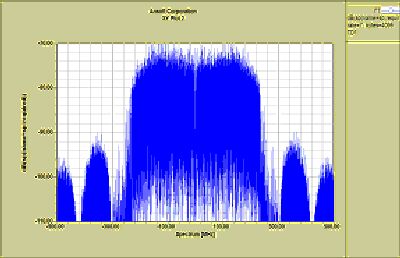

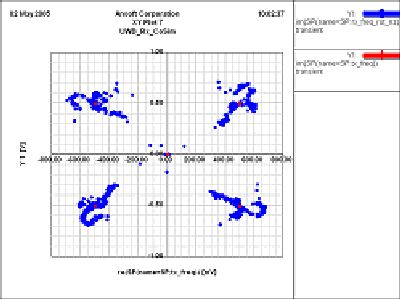

Nexxim使用HFSS提取的寄生效應(yīng)進(jìn)行電路仿真,產(chǎn)生的全芯片分析的有代表性的結(jié)果包括接收器輸入信號(hào)頻譜圖(圖16a)和顯示了接收器上檢測(cè)到的QPSK符號(hào)的星座圖(圖16b)。

圖16:全芯片驗(yàn)證仿真結(jié)果(a) 接收機(jī)輸入端頻譜;

圖16:全芯片驗(yàn)證仿真結(jié)果(b) 接收機(jī)檢測(cè)到的QPSK符號(hào)星座圖

本文小結(jié)

工程師和EDA供應(yīng)商了解成功的RFIC設(shè)計(jì)需要一個(gè)具有四個(gè)主要組件的開發(fā)基礎(chǔ)架構(gòu),它們分別是:

1. 支持時(shí)域和頻域分析以及很大晶體管數(shù)量和在這樣的器件中發(fā)現(xiàn)的諧波部分的電路仿真技術(shù);

2. 經(jīng)過驗(yàn)證的基于電磁的建模過程,這個(gè)過程能提供準(zhǔn)確的、可擴(kuò)展的無源器件以及開/關(guān)芯片互連和封裝寄生參數(shù)描述;

3. 完善建立的設(shè)計(jì)流程,這個(gè)設(shè)計(jì)流程將這個(gè)電路仿真與EM技術(shù)銜接到經(jīng)代工廠驗(yàn)證的器件模型、參數(shù)版圖單元以及物理實(shí)現(xiàn)能力(如DRC與LVS);

4. 系統(tǒng)級(jí)開發(fā)工具用于開始的連接估算與最終的“測(cè)試平臺(tái)”設(shè)計(jì)驗(yàn)證。Ansoft的技術(shù)領(lǐng)先的分析工具能直接進(jìn)入到已建立的IC設(shè)計(jì)和驗(yàn)證流程,以滿足這些嚴(yán)格的要求。