1,、引言

三坐標(biāo)測量機做為一種高精度測量儀器,在機械工業(yè),、汽車工業(yè),、航空航天等領(lǐng)域具有廣泛的應(yīng)用。本套通訊系統(tǒng)采用FPGA[1]為主要通訊芯片,,使用FPGA實現(xiàn)各通訊模塊對數(shù)據(jù)的收發(fā),,配合單片機對數(shù)據(jù)進(jìn)行編碼、解碼,、重封裝,,實現(xiàn)了計算機和控制系統(tǒng)的通訊;由于FPGA程序的并行執(zhí)行結(jié)構(gòu)和高的執(zhí)行速度,,因此大大保證了數(shù)據(jù)傳輸?shù)臏?zhǔn)確性和快速性,。

2、通訊模塊的實現(xiàn)

2.1 計算機與橋接卡的通訊

本系統(tǒng)采用RS232總線實現(xiàn)計算機和橋接卡之間的通訊,。計算機發(fā)送的數(shù)據(jù),,經(jīng)過RS232總線傳輸?shù)綐蚪涌ǎㄟ^MAX3232芯片實現(xiàn)電平轉(zhuǎn)換,。FPGA檢測到起始位后接收數(shù)據(jù),,接收完數(shù)據(jù)后,將其存于UART接收FIFO[2]中,;待接收到結(jié)束位時,,F(xiàn)PGA產(chǎn)生中斷信號,觸發(fā)單片機讀取接收FIFO中的數(shù)據(jù)并對其解碼,,判斷數(shù)據(jù)中的目的地址,,根據(jù)目的地址決定是否處理或發(fā)送到控制板,;橋接卡與計算機通訊時,首先將數(shù)據(jù)進(jìn)行編碼,,然后將數(shù)據(jù)置于發(fā)送FIFO中,,啟動發(fā)送模塊,發(fā)送模塊自動將數(shù)據(jù)發(fā)出,,數(shù)據(jù)經(jīng)MAX3232發(fā)送到總線上等待計算機的接收,。

(1)串口發(fā)送模塊的FPGA實現(xiàn)

串口發(fā)送模塊從發(fā)送FIFO讀出數(shù)據(jù)后,根據(jù)串口通信協(xié)議,,數(shù)據(jù)在向外發(fā)送時,,低位在前,高位在后,,所以將八位的數(shù)據(jù)重新進(jìn)行編輯:前加停止位‘1’,,后加起始位‘0’,變?yōu)槭粩?shù)據(jù)包,,將十位數(shù)據(jù)按照設(shè)置波特率逐位發(fā)送即可,,使用Modelsim進(jìn)行仿真,仿真圖見圖1(data位要發(fā)送的數(shù)據(jù),,tx為發(fā)送線)

(2)串口接收模塊的FPGA實現(xiàn)

總線空閑時當(dāng)檢測到由高到低變化時,表明數(shù)據(jù)開始傳輸,,接收模塊準(zhǔn)備接收數(shù)據(jù),接收數(shù)據(jù)時低位在前,,高位在后,,當(dāng)接收到起始位后,每隔一個數(shù)據(jù)傳輸周期接收一次數(shù)據(jù),,待接收到八位數(shù)據(jù)后將數(shù)據(jù)置于接收FIFO中,使用Modelsim進(jìn)行對發(fā)送模塊仿真見圖2(rxBuf為接收到的數(shù)據(jù),,低位在前,,高位在后):

2.2 橋接卡與控制卡及控制卡之間的通訊

由于橋接卡需要和多個控制卡進(jìn)行信息的交換,且不同的控制卡之間也需要數(shù)據(jù)傳輸,,因此在進(jìn)行總線選擇時,,必須保證各個器件都具有主控的權(quán)利,可以占用總線,,本系統(tǒng)中橋接卡和控制卡及控制卡之間采用I2C[3][4]總線進(jìn)行通訊,。

I2C總線是一種兩線式串行雙向總線,是多主控的總線,,由時鐘線和數(shù)據(jù)線構(gòu)成,,數(shù)據(jù)傳輸時,時鐘信號由主控器件產(chǎn)生,。當(dāng)SCL為高電平時,,SDA出現(xiàn)由高電平到低電平變化,,表明開始傳送數(shù)據(jù);當(dāng)SCL為高電平時,,SDA出現(xiàn)低電平到高電平變化,,表示數(shù)據(jù)傳送結(jié)束;接收方收到數(shù)據(jù)后,,需向發(fā)送方發(fā)出應(yīng)答信號,;為了防止總線上數(shù)據(jù)沖突,總線有仲裁機制,,當(dāng)總線同時被多個發(fā)送方占用時,,首先出現(xiàn)高電平的發(fā)送方被仲裁掉,因此,,最長低電平周期的器件占用總線,,成為主控器件;被仲裁掉的器件,,放棄總線,,改為接收。

使用FPGA實現(xiàn)I2C總線時,,需要建立三個模塊:總線監(jiān)視模塊,,總線發(fā)送模塊,總線接收模塊,。

?、倏偩€監(jiān)視模塊[5]的實現(xiàn)

總線監(jiān)視模塊用來為發(fā)送和接收模塊提供總線狀態(tài),總線分為空閑,、忙,、等待三種狀態(tài)。當(dāng)總線上沒有數(shù)據(jù)傳輸時,,保持高電平,,稱為空閑態(tài);數(shù)據(jù)傳輸期間,,總線為忙的狀態(tài),,如果主控方占用總線后沒有數(shù)據(jù)發(fā)送,則為等待狀態(tài),,如果總線等待時間超過設(shè)定時間,,總線由等待轉(zhuǎn)為空閑態(tài)。發(fā)送,、接收模塊需要得到的信號為起始信號,、結(jié)束信號和狀態(tài)信號,由總線監(jiān)視模塊實現(xiàn)這些信號,。使用Modelsim進(jìn)行仿真,,得到波形如圖3:

?、贗2C發(fā)送模塊[6]的FPGA實現(xiàn)

發(fā)送模塊主要實現(xiàn)對數(shù)據(jù)的發(fā)送;首先發(fā)送地址,,發(fā)送完地址后,,等待應(yīng)答信號,如果沒有響應(yīng),,則放棄總線,;如果出現(xiàn)響應(yīng),I2C發(fā)送模塊輸出RAM地址,,讀取RAM的數(shù)據(jù),依次發(fā)送數(shù)據(jù),,每發(fā)送完一個字節(jié),等待響應(yīng)信號,,發(fā)送模塊根據(jù)RAM中的數(shù)據(jù)長度,,將RAM數(shù)據(jù)讀完。為了防止多個主機同時占用總線,,應(yīng)根據(jù)仲裁機制將總線上的非主控方仲裁掉,,禁止其繼續(xù)占用總線。為了防止總線傳輸中信號延遲,,當(dāng)向總線上發(fā)送下一數(shù)據(jù)時對總線上的狀態(tài)進(jìn)行判斷,,如果正確,再發(fā)送下一位數(shù)據(jù),。否則,,放棄總線。使用Modelsim對I2C發(fā)送模塊進(jìn)行仿真如圖4,。

I2C_outScl:發(fā)送時鐘,;I2C_inScl:檢測時鐘

I2C_outSda:發(fā)送數(shù)據(jù);I2C_inSda:檢測數(shù)據(jù)

desAddr:目的地址,;msgData:發(fā)送數(shù)據(jù)

RAM_Addr:RAM的地址信號,。

③I2C接收模塊[7]的FPGA實現(xiàn)

接收模塊接收到總線監(jiān)視模塊發(fā)送來的起始位信號后,,準(zhǔn)備接收總線上的數(shù)據(jù),接收到的地址后,,判斷接收到的地址和電路板地址是否一致,;當(dāng)兩者一致時,向總線置應(yīng)答信號ACK,繼續(xù)接收下面的數(shù)據(jù),,收到的數(shù)據(jù)置于接收FIFO中,;如果地址不一致,則放棄總線,。使用Modelsim對I2C接收模塊進(jìn)行仿真如圖4,。

I2CbusIsBusy:總線狀態(tài),;I2C_start:起始信號

myAddr:電路板的地址; rxBuf:接收寄存器

rxFIFO_wr:接收FIFO的寫信號

3,、通訊協(xié)議

上位機和橋接板之間采用RS232總線進(jìn)行數(shù)據(jù)傳輸,,橋接卡和控制卡以及各個控制卡之間采用I2C總線進(jìn)行數(shù)據(jù)的傳輸,通訊采用主叫和應(yīng)答方式,數(shù)據(jù)傳輸中使用單片機進(jìn)行解碼[8],。

主叫方發(fā)出指令后,,等待對方響應(yīng),如果主叫方寫指令到被叫方,,則被叫方收到指令執(zhí)行操作后返回確認(rèn)信號,;如果從主叫方讀指令,則被叫方在下一時刻占用總線后發(fā)送數(shù)據(jù)到主叫方,,主叫方在0.5s內(nèi)沒有收到響應(yīng)包,,表明傳輸失敗。若連續(xù)3次沒有響應(yīng),,則與對方通信連接失敗,。

為了實現(xiàn)數(shù)據(jù)的一致性,RS-232和I2C總線采用相同的通信協(xié)議,。

數(shù)據(jù)傳輸時以“包”進(jìn)行封裝,,中間加入長度位和奇偶校驗位。封裝格式:起始字符+長度字符 +序列號+源地址+目的地址包類型+傳輸數(shù)據(jù)+包校驗+結(jié)束字符,;數(shù)據(jù)傳輸均采用ASCII碼,。

包的定義:起始位定義為‘#’,占用一個字節(jié),,接收方接收到‘#’時,,表明數(shù)據(jù)開始傳輸;長度字符定義為除起始字符,、結(jié)束字符和校驗字符的所有原始字符的長度,,占用一個字節(jié);源地址:發(fā)送方地址,,占用一個字節(jié),;目的地址:接收方地址,占用一個字節(jié),,當(dāng)為‘00’時,,定義為廣播地址;包類型:占用一個字節(jié),,表明數(shù)據(jù)的類型,,接收方根據(jù)包類型執(zhí)行對應(yīng)操作;傳輸數(shù)據(jù):控制量的大小,;包校驗:定義為長度字符,,源地址,目的地址,,包類型和數(shù)據(jù)之和,,占用兩個字節(jié);結(jié)束位:定義為‘~’,,當(dāng)接收方接收到結(jié)束字符時,,表明本包傳輸結(jié)束,對數(shù)據(jù)包進(jìn)行處理,長度位和校驗位正確時執(zhí)行指令,,否則,,放棄改數(shù)據(jù)包。

4,、實驗結(jié)果

使用該通訊系統(tǒng)實現(xiàn)和四控制卡之間的通訊控制,,使用串口助手進(jìn)行數(shù)據(jù)收發(fā),在發(fā)送數(shù)據(jù)間隔為5us的情況下對該通訊系統(tǒng)進(jìn)行測試,,在進(jìn)行8小時的測試中,,系統(tǒng)沒有出現(xiàn)數(shù)據(jù)丟失、錯誤,、死機現(xiàn)象,;使用廣播地址進(jìn)行數(shù)據(jù)發(fā)送,返回信號正確,,沒出現(xiàn)死機現(xiàn)象,。

使用該通訊系統(tǒng)對四個電機進(jìn)行控制,電機實際輸出情況如表1:

本實驗數(shù)據(jù)證明了該通訊系統(tǒng)的可用性及數(shù)據(jù)傳輸?shù)臏?zhǔn)確性,。

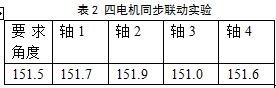

使用該系統(tǒng)采用廣播地址實現(xiàn)四個電機同步聯(lián)動,,各個軸的運動情況如表2:

本實驗數(shù)據(jù)證明了各個電機實現(xiàn)了指定的轉(zhuǎn)動角度;各個軸運動期間,,電機的狀態(tài)經(jīng)過I2C總線[9]及RS-232總線通訊系統(tǒng)成功的發(fā)送到了上位機,,通訊系統(tǒng)沒有出現(xiàn)死機和數(shù)據(jù)丟失,經(jīng)過該實驗,,證明了數(shù)據(jù)傳輸?shù)恼_性,。

4、結(jié)論

本系統(tǒng)采用FPGA進(jìn)行通訊系統(tǒng)的設(shè)計,,提高了數(shù)據(jù)的傳輸率和準(zhǔn)確性,,實現(xiàn)了對控制機構(gòu)及時、快速的控制,,有效防止突發(fā)事件的處理,經(jīng)實驗證明,本系統(tǒng)快速,、準(zhǔn)確的實現(xiàn)了數(shù)據(jù)的傳輸,,可以有效快速的實現(xiàn)對電機的速度、位置控制,、準(zhǔn)確的讀取電機的編碼器信號,。