1 引言

相位檢測(cè)是電力系統(tǒng)自動(dòng)控制和諧波分析與控制的關(guān)鍵技術(shù)。傳統(tǒng)的相位測(cè)量是利用過零電路把輸入的兩路信號(hào)(電壓或電流)轉(zhuǎn)換為方波信號(hào),再利用邏輯電路和單片機(jī)技術(shù)對(duì)信號(hào)某一特殊區(qū)段計(jì)數(shù)和數(shù)學(xué)變換,求得相位差。隨著可編程器件(FPGA,CPLD)的快速發(fā)展,目前采用以MCU+FPGA/CPLD為核心的設(shè)計(jì)理念。這種混合設(shè)汁方案利用CPLD在線修改的特點(diǎn),實(shí)現(xiàn)各種復(fù)雜數(shù)字邏輯設(shè)計(jì),結(jié)合單片機(jī)的控制功能。簡化數(shù)字電路系統(tǒng)設(shè)計(jì),大大縮短系統(tǒng)研制開發(fā)周期。本文采用MCU+CPLD設(shè)計(jì)方法,測(cè)量兩路信號(hào)的相對(duì)寬度,充分利用CPLD速度快,單片機(jī)控制和數(shù)據(jù)處理能力強(qiáng)的優(yōu)勢(shì),完成頻率和相位差的測(cè)量和顯示,大大簡化了硬件電路,并提高了測(cè)量精度和抗干擾能力。

2頻率和相位測(cè)量原理

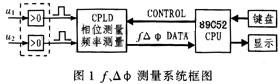

頻率測(cè)量可先測(cè)周期T,然后根據(jù)公式f=1/T算出頻率,這種方法為間接測(cè)量。根據(jù)測(cè)頻的誤差分析,在f較低場(chǎng)合,f越低T越大。計(jì)數(shù)器得數(shù)N也越大,±1誤差對(duì)測(cè)量結(jié)果的影響減小。具體實(shí)現(xiàn)方法是被測(cè)信號(hào)(正弦)經(jīng)整形電路后成為方波,用于控制主門的通斷,在此期間(一個(gè)周期T)外部時(shí)標(biāo)信號(hào)TS通過主門,用計(jì)數(shù)器累計(jì)時(shí)標(biāo)脈沖個(gè)數(shù)。被測(cè)信號(hào)周期T=NTS,其中TS為時(shí)標(biāo)脈沖周期,N為被測(cè)信號(hào)一個(gè)周期之內(nèi)累計(jì)時(shí)的標(biāo)脈沖個(gè)數(shù)。相位差△φ對(duì)應(yīng)的時(shí)間=N1TS,則△φ=(△T/T)×360°。圖1給出f、△φ測(cè)量系統(tǒng)框圖。

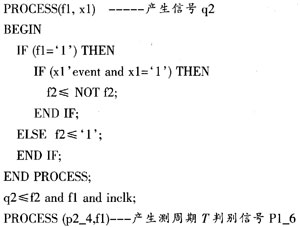

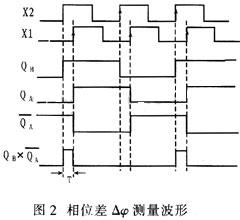

兩個(gè)頻率相同而相位不同的正弦信號(hào)u1=Asinwt和u2=Asinw (t+△T)分別送人比較器整形后得到兩個(gè)方波信號(hào)X1、X2。其中X2送入雙D觸發(fā)器的1CLK端,得到圖2中的QB波形;同理,利用X1可得到QA波形。最后將QB和QA送人與門74LS11,QB×QA相與得到時(shí)間差脈沖△T,△T與相位差對(duì)應(yīng)(△φ=w△T)。

3硬件電路設(shè)計(jì)

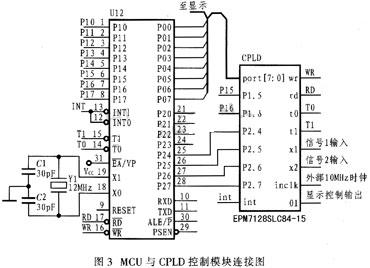

MCU與CPLD控制模塊連接如圖3所示,MCU采用8位單片機(jī)AT89C51,CPLD選用Altera公司MAX7000S系列中的EPM7128SLC84-15,該器件一共有84個(gè)引腳,68個(gè)I/O端口,采用EEPROM技術(shù),內(nèi)含2500個(gè)邏輯門,128個(gè)宏單元。圖3中CPLD模塊的×1、×2為整形后的被測(cè)信號(hào)輸入端,inclk為外部時(shí)標(biāo)信號(hào)輸入端,t0、t1端分別與單片機(jī)的定時(shí)/計(jì)數(shù)器T0,T1相連,采用單片機(jī)內(nèi)部16位定時(shí)/計(jì)數(shù)器,加上CPLD模塊內(nèi)的8位計(jì)數(shù)器,可使計(jì)數(shù)器位數(shù)達(dá)到24位,以此提高分辨率。P25與讀信號(hào)RD、P26與RD分別控制兩個(gè)鎖存器74373的數(shù)據(jù)讀取,此外P24、P15、P16分別控制相位和周期的測(cè)量。P27與寫信號(hào)WR控制寫顯示器,P10、P11、P12、P13、P14用于鍵盤和顯示的控制。單片機(jī)P0端口用于從CPLD讀取8位計(jì)數(shù)器數(shù)據(jù),另外還用于向顯示器寫顯示數(shù)據(jù)。

4軟件設(shè)計(jì)

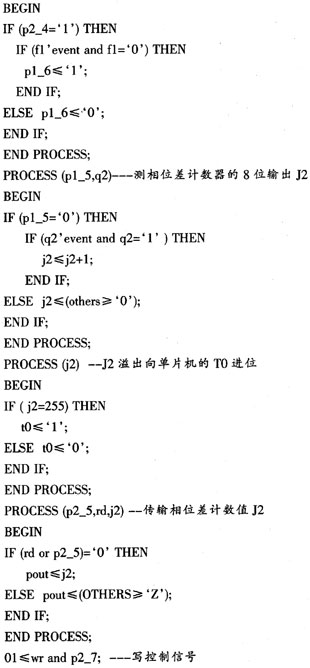

4.1 CPLD控制模塊設(shè)計(jì)

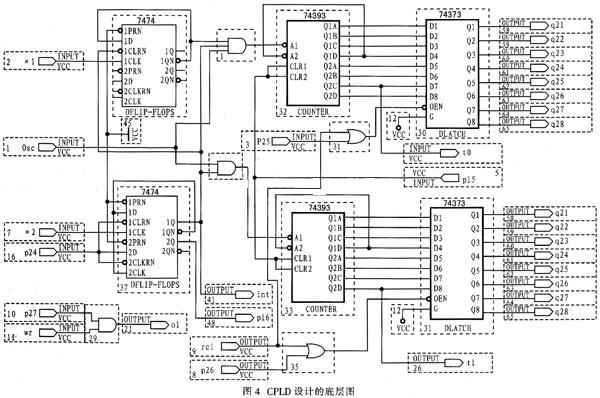

CPLD控制模塊的底層沒計(jì)如圖4所示,CPLD控制程序中的變量P2.4、p1.5、×1、×2、p2_6、rd、p2_7、wr的數(shù)據(jù)類型為IN STD_LOGIC;變量p1_6、t0、t1、o1、pout的數(shù)據(jù)類型為OUT STD_LOGIC;中間變量有f2、f1、j1、j2、q1,q2,其中f2、f1分別與圖2中的波形QA、QB表示的端口一致;j1、j2的數(shù)據(jù)類型std_logic_vector,分別代表圖4中兩個(gè)8位計(jì)數(shù)器74393的輸出;q1,q2分別表示與門7403、7411的輸出。根據(jù)頻率、相位測(cè)量原理,測(cè)量部分將由CPLD完成,測(cè)量結(jié)果經(jīng)單片機(jī)運(yùn)算后存LED上顯示。由CPLD完成的相位測(cè)量部分程序以下給出相關(guān)程序代碼。

4.2 MCU程序設(shè)計(jì)

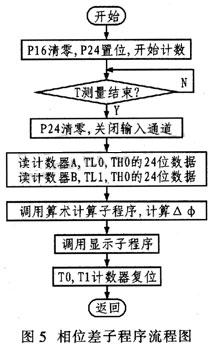

系統(tǒng)控制軟件采用C語言和匯編語言混合編寫,采用模塊化設(shè)計(jì),各個(gè)功能子模塊獨(dú)立。整個(gè)軟件分為主程序、頻率測(cè)量子程序、相位差測(cè)量子程序。圖5為相位差測(cè)量子程序流程圖。

5 CPLD仿真

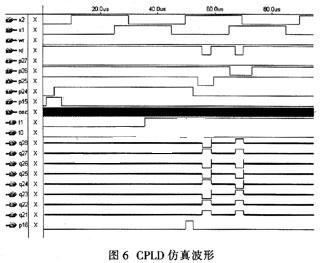

系統(tǒng)CPLD仿真波形如圖6所示,在×1、×2端輸入周期T=40μs、相位差△φ=135°的兩路被測(cè)信號(hào),osc端為5 MHz的輸入時(shí)標(biāo)信號(hào)。本系統(tǒng)設(shè)計(jì)實(shí)現(xiàn)f、△φ測(cè)量,首先要是準(zhǔn)確判斷出被測(cè)信號(hào)的一個(gè)周期的起始與結(jié)束,因此采用單片機(jī)P16、P24來完成周期判斷。

結(jié)合圖4的CPLD設(shè)計(jì)的底層圖和圖6的CPLD仿真波形分析如下:首先P24=0。使下面的雙D觸發(fā)器清零,即1Q=2Q=0,而且P15=1對(duì)兩個(gè)計(jì)數(shù)器74393清零,等待計(jì)數(shù)。P24由0→1后,當(dāng)被測(cè)信號(hào)×2上升沿到來時(shí)1Q翻轉(zhuǎn),1Q=1,打開與門7411和7408,允許時(shí)標(biāo)脈沖計(jì)數(shù),此時(shí)2Q仍為0;當(dāng)被測(cè)信號(hào)×2第二次上升沿到來時(shí)1Q再次翻轉(zhuǎn),1Q=0,同時(shí)2Q也翻轉(zhuǎn),2Q=1。此時(shí)單片機(jī)查詢到P16=1,完成一個(gè)周期的檢測(cè)。然后使P24=0,關(guān)閉與門7411和7408,停止計(jì)數(shù)。

計(jì)數(shù)完畢后,當(dāng)P25為低電平且RD下降沿到來時(shí),單片機(jī)讀取第一個(gè)鎖存器74373的數(shù)據(jù)為[q28…q211]=01001011;當(dāng)P26為低電平且RD下降沿到來時(shí),單片機(jī)讀取第二個(gè)鎖存器74373的數(shù)據(jù)為[q28…q21]=11000111,則△φ=(01001011/11000111)x360°=(75/199)×360°=135°。可見波形仿真驗(yàn)證了系統(tǒng)設(shè)計(jì)的正確性。

6結(jié)語

本文給出了一種采用CPLD器件EPM7128SLC84215實(shí)現(xiàn)相位差智能化測(cè)量儀的方案。整個(gè)系統(tǒng)充分利用單片機(jī)CPLD可編程邏輯器件各自的優(yōu)勢(shì),只需少量的外圍電路,即可有效測(cè)量正弦波、方波、三角波信號(hào)的相位差,硬件電路簡單,精度高,抗干擾能力強(qiáng),性能指標(biāo)良好。