0 引言

當(dāng)前信號(hào)處理的發(fā)展趨勢(shì)是可重構(gòu)、可擴(kuò)展的通用信號(hào)處理系統(tǒng)。即通過(guò)靈活的軟件編程來(lái)適應(yīng)處理問(wèn)題的變化和算法的發(fā)展,通過(guò)簡(jiǎn)單的硬件擴(kuò)展來(lái)適應(yīng)規(guī)模處理的變化,以提高信號(hào)處理系統(tǒng)的可編程能力和升級(jí)能力。而采用具備強(qiáng)大處理能力的ADSP-TS201S芯片可以對(duì)大量的數(shù)據(jù)作實(shí)時(shí)處理。TS201S可在600 MHz的內(nèi)核時(shí)鐘下完成每秒48億次乘累加(MAC)運(yùn)算和每秒36億次浮點(diǎn)運(yùn)算(FLOP),具有比同類處理器高出50%~100%的處理能力。它內(nèi)部集成了24 MB的存儲(chǔ)器,其片內(nèi)大存儲(chǔ)量與高達(dá)33.6 Gb/s的內(nèi)部帶寬是提高性能的關(guān)鍵。TS201S的外部64位數(shù)據(jù)總線和32位地址總線時(shí)鐘最高可達(dá)125 MHz。

本文通過(guò)GA3816、FPGA和DSP構(gòu)建了一個(gè)高速、通用、可擴(kuò)展的多功能信號(hào)處理平臺(tái),該信號(hào)處理平臺(tái)經(jīng)過(guò)動(dòng)態(tài)配置GA3816處理芯片可實(shí)現(xiàn)一些信號(hào)處理領(lǐng)域常用的運(yùn)算,也可以通過(guò)對(duì)DSP、FPGA芯片的編程來(lái)實(shí)現(xiàn)一些其它算法,所以該平臺(tái)能夠廣泛的應(yīng)用于信號(hào)處理等領(lǐng)域。

1 系統(tǒng)設(shè)計(jì)

1.1 系統(tǒng)硬件結(jié)構(gòu)

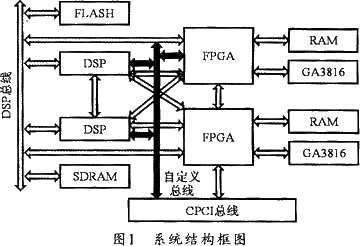

本通用信號(hào)處理平臺(tái)主要由雙TS201、雙stratix系列FPGA和雙GA3816處理器構(gòu)成,同時(shí)使用了一些RAM、FLASH和SDRAM器件來(lái)存儲(chǔ)系統(tǒng)中的數(shù)據(jù)和程序。系統(tǒng)與外部進(jìn)行通信的接口主要采用CPCI總線接口。本設(shè)計(jì)采用DSP結(jié)合FPGA的方式。這種方式最大的優(yōu)點(diǎn)就是結(jié)構(gòu)靈活,有較強(qiáng)的通用性,適合模塊化設(shè)計(jì),并能夠提高效率,同時(shí),其開(kāi)發(fā)周期較短,系統(tǒng)容易維護(hù)和擴(kuò)展,所以,這種結(jié)構(gòu)目前比較流行。圖1是該系統(tǒng)的結(jié)構(gòu)框圖。

1.2 系統(tǒng)功能

此信號(hào)處理板的體系結(jié)構(gòu)可以概括為三個(gè)處理陣列、兩條板級(jí)接口總線和一條板內(nèi)總線。三個(gè)處理陣列指的是GA3816處理陣列、DSP處理陣列和FPGA處理陣列。兩條板級(jí)接口總線是指CP-CI總線和用戶自定義總線。一條板內(nèi)總線是指DSP總線。

用戶自定義總線可由兩個(gè)DSP處理器的兩個(gè)鏈路口和一組由FPGA引出的備份信號(hào)線構(gòu)成,包括時(shí)鐘線、控制線和數(shù)據(jù)線。該總線可以針對(duì)不同應(yīng)用環(huán)境,由用戶自己根據(jù)需要加以定義。DSP和FPGA通過(guò)自定義總線與外部系統(tǒng)進(jìn)行通信,而DSP通過(guò)鏈路口可以與外部系統(tǒng)實(shí)現(xiàn)程序加載以及數(shù)據(jù)互傳,F(xiàn)PGA則通過(guò)備份信號(hào)線實(shí)現(xiàn)與外部系統(tǒng)的數(shù)據(jù)傳輸。

DSP總線主要是為DSP處理陣列提供一條內(nèi)部互聯(lián)和與FPGA處理陣列互聯(lián)的通道。通過(guò)這條總線,DSP1和DSP2可以相互共享存儲(chǔ)空間,并且二者可通過(guò)此總線共享板上的FLASH存儲(chǔ)器和SDRAM,并分別將二者作為自己的程序存儲(chǔ)器和內(nèi)存擴(kuò)展。系統(tǒng)復(fù)位后,DSP通過(guò)FLASH進(jìn)行程序加載。

目前,PCI總線接口的設(shè)計(jì)有兩種方法,一種是利用專用的PCI接口芯片來(lái)設(shè)計(jì)。另一種是利用FPGA可編程器件進(jìn)行設(shè)計(jì)。由于用FPGA比較復(fù)雜,開(kāi)發(fā)難度較大。為此,本系統(tǒng)將PCI控制器軟核嵌入到FPGA中,從而控制本板對(duì)外的CPCI總線。本板則通過(guò)CPCI總線或自定義總線接收待處理的數(shù)據(jù),并在FPGA巾對(duì)將待處理數(shù)據(jù)分配給GA3816處理通道和DSP處理通道。當(dāng)這兩個(gè)處理通道的處理結(jié)果反送到FPGA后,義在FP-GA中進(jìn)行數(shù)據(jù)交換或者通過(guò)CPCI總線作為本板級(jí)處理器的輸出。此外,兩片F(xiàn)PGA中也有大量的硬件資源,可以針對(duì)不同應(yīng)用場(chǎng)合,通過(guò)固件編程使其成為專用處理器,或組成FPGA處理陣列。而兩個(gè)FPGA器件之間的64位雙向信號(hào)線則可以使兩個(gè)FPGA器件之間的數(shù)據(jù)傳輸更為方便和快捷。

系統(tǒng)中的兩個(gè)RAM器件可分別直接和兩個(gè)FPGA器件進(jìn)行通信,并可通過(guò)FPGA分別作為兩個(gè)GA3816處理陣列的片外存儲(chǔ)器,也可作為板上的程序或者數(shù)據(jù)緩存。因?yàn)閷?duì)于一般的運(yùn)算來(lái)說(shuō),GA3816的處理速度要高于TS201的處理速度(對(duì)于1024點(diǎn)的復(fù)數(shù)FFT運(yùn)算來(lái)說(shuō),GA3816的速度為12.8μs,而主頻為300 MHz的TS201則為32.78μs),所以在系統(tǒng)所需實(shí)現(xiàn)的功能中,如果GA3816芯片可以實(shí)現(xiàn)就直接用它來(lái)實(shí)現(xiàn)(如FFT、FIR等),GA3816不能實(shí)現(xiàn)的功能則可根據(jù)需要在TS201和FPGA中編程實(shí)現(xiàn)。在FPGA中對(duì)GA3816芯片進(jìn)行配置可以實(shí)現(xiàn)GA3816的不同處理功能以及運(yùn)算模式,從而滿足不同應(yīng)用場(chǎng)合中GA3816芯片的不同數(shù)據(jù)處理功能。

1.3 時(shí)鐘模塊

ADSP TS201S的系統(tǒng)輸入時(shí)鐘SCLK同時(shí)也是TS201S的外部接口時(shí)鐘,為與外部器件兼容,SCLK不應(yīng)取得太高。一般可取內(nèi)核時(shí)fCCLK為fSCLK與SCLKRAT的積,P-BUS的工作時(shí)鐘fSOCCLK為fCCLK/2,鏈路口時(shí)鐘fLxCLK為fCCLK/CR(CR為L(zhǎng)CTLxREGlSTER的設(shè)置值),若SPD位設(shè)置為100,則取fLxCLK=fCCLK/4。這樣,將時(shí)鐘信號(hào)再經(jīng)過(guò)時(shí)鐘驅(qū)動(dòng)后分別送入兩個(gè)FPGA,再由FPGA的鎖相環(huán)進(jìn)行倍頻或者分頻就可得到DSP、SDRAM、GA3816和RAM所需要的時(shí)鐘信號(hào)。

GA3816和RAM的時(shí)鐘信號(hào)可由FPGA直接提供,DSP和SDRAM的時(shí)鐘信號(hào)則由FPGA提供的時(shí)鐘通過(guò)一個(gè)時(shí)鐘驅(qū)動(dòng)器來(lái)供給。設(shè)計(jì)時(shí)應(yīng)盡可能的使時(shí)鐘線等長(zhǎng)的到達(dá)器件,這樣可以減少時(shí)鐘偏移,從而使DSP和SDRAM之間能夠更好的通信。因?yàn)闀r(shí)鐘信號(hào)是非常敏感的信號(hào),所以要盡量的減少反射和串?dāng)_。在時(shí)鐘信號(hào)線上串接適當(dāng)?shù)钠ヅ潆娮杩梢杂行У臏p少反射,而減少串?dāng)_則需要在時(shí)鐘走線周圍留出額外的空間,或者把時(shí)鐘線單獨(dú)放在兩個(gè)地平面層中間的一層,這樣可以使時(shí)鐘的信號(hào)完整性得到有效的改善。

1.4 電源模塊

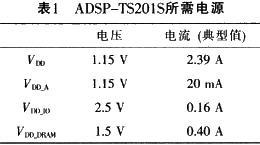

stratix和GA3816的核電源電壓分別為1.5 V和1.8 V,3.3 V為I/O電源,ADSP-TS201S的三種電源如表1所列。本設(shè)計(jì)中所需的四種電壓都是從外部輸入的5 V電源轉(zhuǎn)換而成的,轉(zhuǎn)換芯片選用TI公司的TPS54350器件。

由于電源層無(wú)法單獨(dú)消除線路噪音,所以通常需要借助旁路電容來(lái)進(jìn)行濾波。一般情況下,將1~10μF電容放置在電路板的電源輸入端可濾除板外產(chǎn)生的低頻信號(hào);而將0.01~0.1μF電容放置在電路板的每個(gè)有源器件的電源引腳和接地引腳上,則可濾除電路板上有源器件產(chǎn)生的高頻率的噪聲諧波。但是,任何一種電容的濾波頻率范圍都是有限的,所以通常采用大小電容并聯(lián)的方式來(lái)擴(kuò)展其有效的濾波頻率范圍。

1.5 復(fù)位模塊

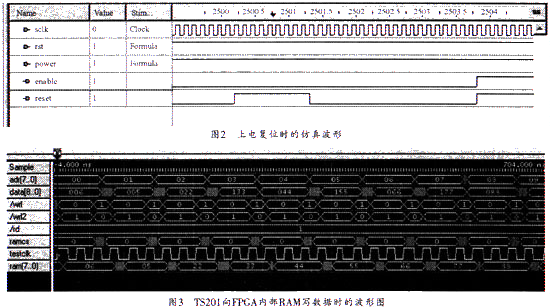

ADSP TS201S的復(fù)位信號(hào)較ADSP TS101S更簡(jiǎn)單,它可以采用較簡(jiǎn)單的上電復(fù)位方式,即要求電源正常后保持RST_IN為低2 ms以上,并在RST_IN有效之前使SCLK運(yùn)行2 ms。上電復(fù)位相對(duì)于正常復(fù)位來(lái)說(shuō)要復(fù)雜一些。在FPGA中實(shí)現(xiàn)TS201的復(fù)位和時(shí)序控制,可使TS201正常工作。圖2為T(mén)S201上電復(fù)位穩(wěn)定后的仿真波形。圖中,sclk為8 MHz時(shí)鐘(由TS201的SCLK時(shí)鐘分頻得到),rst為正常復(fù)位信號(hào),power為上電復(fù)位信號(hào),enable為復(fù)位后系統(tǒng)穩(wěn)定的輸出信號(hào),reset為T(mén)S200的復(fù)位輸出信號(hào)。

2 調(diào)試結(jié)果

圖3為調(diào)試過(guò)程中通過(guò)邏輯分析儀采集到的TS201向FPGA內(nèi)部雙口RAM寫(xiě)數(shù)據(jù)時(shí)的波形圖,采用雙口RAM是由于雷達(dá)信號(hào)總是以幀的方式進(jìn)行處理,在處理第一幀的數(shù)據(jù)時(shí),輸出前一幀的數(shù)據(jù),這樣的數(shù)據(jù)訪問(wèn)方式可避免發(fā)生沖突。為了能夠正確的讀寫(xiě)雙口RAM,這里的DSP訪問(wèn)雙口RAM采用的是慢速協(xié)議,即當(dāng)內(nèi)部RAM的片選信號(hào)和TS201的寫(xiě)信號(hào)都為低時(shí),將TS201內(nèi)部的數(shù)據(jù)正確的寫(xiě)入到FPGA的內(nèi)部雙口RAM里。由于測(cè)試針的數(shù)目有限,所以,圖中只顯示了TS201的低8位地址線和低9位數(shù)據(jù)線,而RAM則只顯示了低8位的數(shù)據(jù)線。

3 結(jié)束語(yǔ)

本文介紹了基于TS201的高速信號(hào)處理系統(tǒng)的硬件設(shè)計(jì)以及實(shí)現(xiàn)方法,著重考慮了系統(tǒng)的高速、實(shí)時(shí)和通用性,同時(shí)充分發(fā)揮了GA3816處理器的優(yōu)勢(shì)。由于結(jié)合了DSP和FPGA的強(qiáng)大可編程和處理能力,因此,該信號(hào)處理系統(tǒng)能夠廣泛的應(yīng)用于語(yǔ)音及圖像處理、通信、雷達(dá)、導(dǎo)航、電子對(duì)抗等信號(hào)處理領(lǐng)域。