1. 引言

作為因特網(wǎng)的樞紐,路由器正在朝速度更快、服務(wù)質(zhì)量更好和更易于綜合化管理的三個方向發(fā)展。現(xiàn)在芯片速度每18個月翻一翻,而因特網(wǎng)的流量是每六個月翻一翻。大家對路由器的研究也重點體現(xiàn)在提高路由器的處理速度上,相續(xù)提出了千兆位交換路由器(GSR,Gigabit Switch Router)和太位交換路由器(TSR,Terabit Switch Router)。

隨著IP的核心地位逐漸被認同,IP over ATM、然后ATM over SDH的方式被IP直接over SDH的方式取代。傳輸速度也很快從OC-12 ( 622Mbps ) 跳到OC-48 ( 2.5Gbps )。POS技術(shù)已經(jīng)廣泛用于骨干網(wǎng)中,而POS接口成為高端路由器必不可少的一部分。

我所研制的T比特路由器,系統(tǒng)總吞吐率可達1.28Tbps,峰值交換能力為2.4Tbps,而每端口可達到10G的轉(zhuǎn)發(fā)速率。為達到10G的轉(zhuǎn)發(fā)速率,本路由器采用了4路2.5GPOS接口。文章在第二節(jié)描述了2.5GPOS接口的硬件體系結(jié)構(gòu)的設(shè)計和性能需求分析,在第三節(jié)詳細闡述了軟件體系結(jié)構(gòu)的設(shè)計與實現(xiàn)。

2. 硬件總體結(jié)構(gòu)設(shè)計

本路由器硬件體系結(jié)構(gòu)由線路接口子系統(tǒng)、轉(zhuǎn)發(fā)處理子系統(tǒng)、光背板交換網(wǎng)絡(luò)子系統(tǒng)和內(nèi)部通信子系統(tǒng)四大部分組成。當(dāng)接口收到數(shù)據(jù)包后,首先判斷該包的目的地址是否為本路由器,是則上交給單板軟件并由內(nèi)部通信子系統(tǒng)交給主控處理;否則填充內(nèi)部包頭,注明包類型,協(xié)議類型,目的機架號,端口號,接口號等信息,由同軸電纜交給轉(zhuǎn)發(fā)處理子系統(tǒng),再由光背板轉(zhuǎn)發(fā)到目的接口。接口把轉(zhuǎn)發(fā)送過來的包和本路由器發(fā)出的包,進行和路處理后再發(fā)送出去。

2.1 性能需求分析

1)根據(jù)以往路由器的經(jīng)驗,通常硬件FPGA 中的高速通道工作在2.5Gbps速率下比較穩(wěn)定。就A口輸入數(shù)據(jù)速率10Gbps來說,4個2.5Gbps的高速通道就可以將數(shù)據(jù)傳到轉(zhuǎn)發(fā)處理模塊。但是,線路接口模塊的功能實現(xiàn)要求:數(shù)據(jù)包在經(jīng)過線路接口輸入處理模塊的處理后要加上128 bit即16個byte的內(nèi)部標簽。考慮極限情況,A口收到的都是40 byte的超短包,那么,B口輸出的數(shù)據(jù)的極限速率為:[10Gbps×(40 byte+16 byte)]/40 byte=14Gbps。所以,我們設(shè)計采用兩路2.5Gbps的高速通道來傳A口接收的10Gbps數(shù)據(jù)中的四分之一即2.5Gbps數(shù)據(jù)到轉(zhuǎn)發(fā)處理模塊。那么,B口的最大輸出速率為2.5Gbps×8=20Gbps,完全滿足B口傳輸帶寬要求。

2)在均勻輸入業(yè)務(wù)模型和平衡輸出模型條件下,假定定長分組業(yè)務(wù)強度λ為0.95,為了控制分組的丟失概率小于10-8,可計算所需要的輸出隊列分組緩沖容量S約為650個分組。統(tǒng)計意義上IP分組的平均長度為508字節(jié)。考慮到內(nèi)部分組標簽附加的24字節(jié),平均需要緩沖的IP分組字節(jié)數(shù)為532字節(jié) 總緩沖容量為650×532×8=2766400(Bits),即近似為2.8MBits的緩沖容量。

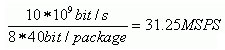

3)本子系統(tǒng)的接口速度要達到10Gbps,如果每個包都是40字節(jié),那么這時極限查表速率為:

對于輸入查表模塊的另一個指標為表項容量。按照極限容量來算,T比特路由器有8個機架,每個機架8個端口,每個端口8個接口,每個接口的IPv4單播組播、IPv6單播組播地址總計有64個。那么極限表項容量為8*8*8*64=32768(32k)條。達到這兩個設(shè)計指標是本模塊設(shè)計的一個難點。最終,我們選擇了一款CAM,有64K條表項,查表速率能夠達到100MSPS。這樣的指標完全可以達到本模塊的要求。

2.2 子系統(tǒng)功能劃分和模塊設(shè)計

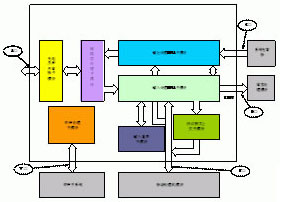

如下圖所示,4 2.5G線路接口子系統(tǒng)可劃分為光電及串并轉(zhuǎn)換模塊、鏈路層處理模塊、輸出FPGA處理模塊、輸入FPGA處理模塊、協(xié)議報文上交緩存模塊、輸入查表模塊和時鐘處理模塊。為描述方便,將本子系統(tǒng)和路由器外部的接口稱為A口,和轉(zhuǎn)發(fā)處理子系統(tǒng)的接口稱為B口,和光背板子系統(tǒng)的接口稱為G口,和單板處理機的接口稱為F口,和時鐘子系統(tǒng)的接口稱為J口。

從路由器外部接收數(shù)據(jù)時,光電及串并轉(zhuǎn)換模塊負責(zé)從A口接收4路2.5Gbit/s串行光信號,轉(zhuǎn)換成16路差分622Mhz電信號;送由鏈路層處理模塊進行鏈路層處理。鏈路層處理模塊從SDH幀提取出ppp報文,然后交給輸入FPGA處理模塊。輸入FPGA處理模塊針對輸入包的類型,對輸入查表模塊存儲的本機IP地址表查表,進行分路處理,若此報文的目的為本路由器則上交主控,否則轉(zhuǎn)發(fā)到B口。輸出FPGA處理模塊負責(zé)接收主控下發(fā)協(xié)議包和從系統(tǒng)光背板轉(zhuǎn)發(fā)G口數(shù)據(jù)包,合路后交給鏈路層處理模塊。鏈路層處理模塊把和路后的ppp報文封裝在SDH幀中,由光電及串并轉(zhuǎn)換模塊轉(zhuǎn)換成光信號發(fā)送出去。時鐘處理模塊為本模塊提供全局時鐘和將本模塊從線路上提取的時鐘輸出到時鐘板。

3. 軟件總體結(jié)構(gòu)設(shè)計與實現(xiàn)

MPC860是基于PowerPC結(jié)構(gòu)的通信控制器。它不僅是集成的微處理器,而且將很多外設(shè)的功能也集成在一起。MPC860具有存儲控制器,其存儲控制器的功能很強,可以支持各種存儲器,包括各種新型的DRAM和Flash,并可以實現(xiàn)與存儲器的無縫接口。

由美國風(fēng)河公司(Wind River)推出的嵌入式強實時操作系統(tǒng)VxWorks因用于火星登陸車而名噪一時。VxWorks是一套具有微內(nèi)核,高性能,可伸縮的操作系統(tǒng),支持廣泛的網(wǎng)絡(luò)通信協(xié)議,并能夠根據(jù)用戶的需求組合,增減。再加上其優(yōu)秀的開發(fā)環(huán)境Tornado,使其成了嵌入式操作系統(tǒng)的首選。選擇MPC860加上嵌入式強實時操作系統(tǒng)VxWorks完全可以買足單板處理的性能需求。

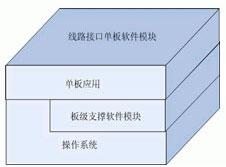

上圖展示了單板軟件總體結(jié)構(gòu)。單板操作系統(tǒng)是采用VxWorks,單板處理器是采用MPC860。路由器有不同種類的線路接口板,每種接口板都需要完成許多相同的功能,可把這些相同的功能放在一個單獨的模塊中實現(xiàn),減少冗余勞動。板級支撐模塊為單板應(yīng)用提供與主控軟件之間的通信、任務(wù)管理、內(nèi)存管理和定時器管理等服務(wù);而單板應(yīng)用為線路接口單板軟件模塊,完成單板轉(zhuǎn)發(fā)處理。

單板軟件主要完成的功能有:對各類型單板硬件的初始化和配置,接收并處理主控下發(fā)的單板控制命令,完成軟硬件程序加載,以太網(wǎng)接口板運行IPv4 ARP協(xié)議,維護并向主控通告ARP信息,協(xié)議數(shù)據(jù)(源/目地址為本路由器的分組)收發(fā),維護路由器接口地址信息,差錯報文處理、記錄報文上報,業(yè)務(wù)性能統(tǒng)計數(shù)據(jù)收集與上報,維護單板與主控板間的通信連接。

按照這些功能,把單板軟件分為初始化模塊,主控命令處理模塊,接口芯片監(jiān)控和業(yè)務(wù)性能統(tǒng)計模塊,消息分發(fā)模塊,包發(fā)送模塊,報接收模塊,自檢模塊,CAM表維護模塊,工具函數(shù)模塊。正常運行時建立四個任務(wù):主控處理任務(wù),統(tǒng)計任務(wù),發(fā)包任務(wù),收包任務(wù)。

其數(shù)據(jù)處理流程如右圖:單板硬件接收到本路由器包,寫入輸入FIFO,收包任務(wù)讀出包,封裝在定義的內(nèi)部數(shù)據(jù)結(jié)構(gòu)中,調(diào)用板級支撐模塊中的發(fā)送函數(shù)發(fā)給主控;主控下發(fā)的包則由消息分發(fā)模塊處理,協(xié)議包交給發(fā)包任務(wù),再寫入輸出FIFO,然后發(fā)送出去,控制包則交主控處理模塊處理,完成向?qū)?yīng)的功能。

由于本接口需要達到10G的速率,各任務(wù)之間必須有穩(wěn)定和高速交互機制。VxWorks操作系統(tǒng)為任務(wù)間通信提供了許多通信方式,包括共享內(nèi)存,信號量,消息隊列和管道,Sockets和遠程調(diào)用等。消息隊列允許長度可變,數(shù)目可變的消息隊列,可以滿足多任務(wù)之間通信。VxWorks的Wind內(nèi)核可采用基于優(yōu)先級的搶占式任務(wù)調(diào)度與輪轉(zhuǎn)調(diào)度相結(jié)合,因此一定要設(shè)置好各任務(wù)的優(yōu)先級,如內(nèi)存任務(wù)的優(yōu)先級就必須高于主控處理任務(wù),主控處理任務(wù)必須高于收發(fā)包的任務(wù)。而對相同優(yōu)先級的任務(wù)必須預(yù)先設(shè)置各任務(wù)的執(zhí)行時間,否則第一個獲得CPU 的任務(wù)就會獨占,阻礙別的人物運行。總之,在軟件設(shè)計中一定要充分了解VxWorks的工作機制,否則不但不能設(shè)計出效益高的程序,反而會阻礙VxWorks的有效運行。

4. 結(jié)束語

高速增長的網(wǎng)絡(luò)和互聯(lián)網(wǎng)通訊量對現(xiàn)有的網(wǎng)絡(luò)基礎(chǔ)結(jié)構(gòu)提出了更高的需求,也刺激了高性能網(wǎng)絡(luò)連接的發(fā)展。本文簡要介紹了吞吐率高達1.28T比特的高性能路由器,并研究了其2.5GPOS接口的實現(xiàn)技術(shù),首先可以深入對POS技術(shù)在實現(xiàn)和應(yīng)用上的研究,其次可以豐富路由器的接口功能,增加路由器接口的靈活性,增強路由器的兼容性,以便更為廣泛的利用網(wǎng)絡(luò)資源,實現(xiàn)網(wǎng)絡(luò)體系和架構(gòu)的演進,為高性能路由器的研制和后續(xù)開發(fā)提供可借鑒的技術(shù)思路。