摘? 要: 介紹了新型數(shù)字視頻接口" title="數(shù)字視頻接口">數(shù)字視頻接口的發(fā)展背景和技術優(yōu)勢,詳細分析了DVI 1.0的通信協(xié)議、T.M.D.S.的鏈路" title="鏈路">鏈路構(gòu)成、信號特性、編碼及解碼算法" title="解碼算法">解碼算法,特別針對實際應用" title="實際應用">實際應用,分析了DVI接口的時鐘構(gòu)成,最后就顯示相關的DDC、EDID、HPD等協(xié)議進行了簡單介紹。

關鍵詞: 數(shù)字視頻接口(DVI)? 最小變換差分信號(T.M.D.S.)? 信號編碼? 鎖相環(huán)

?

1 背景介紹

二十一世紀剛剛顯現(xiàn)第一縷曙光,正當人們享受著以摩爾定律遞增的高速微處理器時,一種新型的視頻接口技術將帶給人們更加絢麗多彩的視覺感受。這就是業(yè)界剛剛發(fā)展起來的DVI(Digital Visual Interface)數(shù)字視頻接口技術。隨著以LCD為代表的數(shù)字平板顯示技術的飛速發(fā)展,DVI必將迅速成為計算機顯示的標準視頻接口。

隨著對綠色顯示觀念的倡導,CRT顯示已由球面發(fā)展到柱面,又從柱面發(fā)展到純平顯示,人們對屏幕刷新率和圖像幾何失真要求愈來愈高,傳統(tǒng)模擬VGA視頻接口+CRT或LCD顯示器的圖像顯示能力越來越捉襟見肘。制造成本的不斷降低,使LCD等平板顯示技術已逐步取代傳統(tǒng)的CRT顯示器成為PC機顯示器的主流。由于要與傳統(tǒng)的VGA模擬接口兼容,其內(nèi)部不得不內(nèi)置一級ADC(數(shù)模轉(zhuǎn)換)及PLL(鎖相環(huán))電路,將模擬的視頻信號轉(zhuǎn)化成數(shù)字信號再進行顯示,還要進一步針對CRT顯示的值進行校正,得到適合LCD象素特性的灰度信號。這樣一系列中間環(huán)節(jié)的轉(zhuǎn)換,加上模擬傳輸環(huán)節(jié)中難以抑制的噪聲干擾問題,使得此類平板顯示的圖像信息丟失,并隨著分辨率和場頻的提高而加重。以LCD、PDP、LED、OLED等為代表的平板顯示(包括數(shù)字投影儀)的蓬勃發(fā)展,對數(shù)字視頻接口技術提出了迫切要求。

DVI數(shù)字視頻接口就是在這種趨勢下產(chǎn)生的。DVI由Intel、Silicon Image、Compaq、Fujitsu Limited、Hewlett-Packard Company、IBM、NEC合作提出的一種數(shù)字視頻接口標準,很好地解決了上述問題,而且還兼容了傳統(tǒng)的VGA接口,是目前極具發(fā)展前途的一種PC機視頻接口標準。本文的目的在于使讀者迅速掌握DVI的通信協(xié)議,從接口提取視頻信息,擺脫對計算機內(nèi)部復雜的硬件原理的研究,使DVI接口的高質(zhì)量數(shù)字視頻信息可以按用戶的要求進行開發(fā)利用。

2 DVI接口構(gòu)成

DVI接口利用最小變換差分信號—T.M.D.S. (Transition Minimized Differential Signal)作為基本電氣鏈接信號。T.M.D.S.鏈路主要用于將圖像數(shù)據(jù)傳送到顯示器。DVI接口協(xié)議允許使用雙T.M.D.S.鏈路結(jié)構(gòu),從而可以支持超大分辨率的顯示設備。T.M.D.S.通過先進的編碼算法將8bit的象素數(shù)據(jù)轉(zhuǎn)換成10bit的最小變換信號,削弱了傳輸電纜中交叉電磁干擾EMI,并且這種直流平衡的編碼信號更有利于光纖傳輸。另外這種先進的編碼算法可以為接收端提供時鐘恢復信號,并允許在較遠距離傳輸時(一般小于5m)信號有較大的抖動誤差。

2.1 DVI體系結(jié)構(gòu)要求

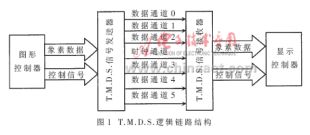

DVI作為一種面向計算機開發(fā)的視頻接口,要與現(xiàn)有的操作系統(tǒng)、硬件平臺兼容,還要與以前的接口標準保持一定的兼容性。圖1是DVI接口T.M.D.S.的邏輯鏈路結(jié)構(gòu)。DVI支持即插即用功能(Plug and Play)。在系統(tǒng)啟動時,DVI提供最低分辨率VGA 640×480模式, 系統(tǒng)通過DDC2B協(xié)議訪問顯示器,獲得顯示器對象素格式的支持情況,通過EDID數(shù)據(jù)獲得關于顯示器型號和現(xiàn)實能力的信息。這些內(nèi)容都是顯示器制造商在顯示器內(nèi)部固化的一段數(shù)據(jù),通過DDC(Display Data Channel)向主機系統(tǒng)提供自身信息。

?

系統(tǒng)啟動后會自動加載圖形顯示控制器(即顯卡)的驅(qū)動程序。根據(jù)用戶提出的顯示要求,即屏幕的分辨率、色深、刷新率,結(jié)合由DDC獲得關于顯示器的信息,確定T.M.D.S.的啟用情況。DVI的單T.M.D.S.只提供24bit色深,當用戶要求的色深超過24bit時,并且系統(tǒng)已經(jīng)確認顯卡和顯示器都支持雙鏈路T.M.D.S.。此時系統(tǒng)會啟動雙T.M.D.S.鏈路,鏈路0(數(shù)據(jù)通道0~2)傳輸24bit信息,其它顏色信息由鏈路1(數(shù)據(jù)通道3~5)傳輸;當用戶的分辨率和刷新率要求超出單T.M.D.S.鏈路的傳輸能力時(單T.M.D.S.鏈路的最高象素傳輸頻率為165MHz),系統(tǒng)會啟動鏈路1,鏈路0用來傳輸奇數(shù)象素信息,鏈路1用來傳輸偶數(shù)象素信息,并定義顯示器上每一行的第一個象素為象素1,奇數(shù)象素。由于雙T.M.D.S.鏈路共用一條時鐘回路,所以雙鏈路工作時,鏈路的時鐘頻率為象素數(shù)據(jù)帶寬的一半。

當然,DVI接口同樣也支持熱插拔(Hot Plug Detection)和顯示器電源管理等技術,還有對傳統(tǒng)的模擬VGA的兼容等問題。這些只是DVI作為一種接口標準必須做到的兼容性問題,并不代表DVI本質(zhì)的先進性。有關這些體系要求問題可參閱參考文獻[1~3]。

2.2 T.M.D.S.協(xié)議詳解

DVI接口的先進性體現(xiàn)在它可以將海量的顯示信息高速地傳送到顯示器中去,T.M.D.S.先進的編碼算法是其強大能力得以實現(xiàn)的根本。下面將詳細解釋T.M.D.S.協(xié)議中與實際應用緊密相關的幾個問題。為了便于理解作以下規(guī)定:輸入到編碼器或由解碼器輸出的象素數(shù)據(jù)稱為象素數(shù)據(jù)(Pixel Data);由發(fā)送器送出的或輸入到接收器的編碼數(shù)據(jù)稱為碼元(Character)。

請注意:在DVI接口協(xié)議中并沒有規(guī)定輸入或輸出的象素數(shù)據(jù)是串行的還是并行的,輸入輸出的數(shù)據(jù)格式留給芯片制造廠商靈活掌握,用戶應根據(jù)自己的實際情況選用芯片型號。

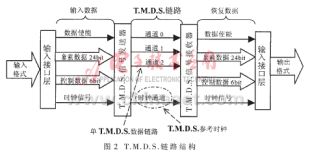

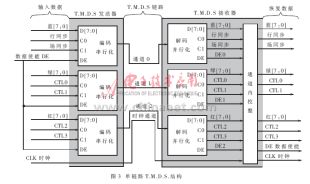

2.2.1 鏈路結(jié)構(gòu)

T.M.D.S.鏈路結(jié)構(gòu)見圖2。圖3是單鏈路T.M.D.S.結(jié)構(gòu)圖。雙鏈路結(jié)構(gòu)與單鏈路很相似[1]。每個鏈路的發(fā)送器(Transmitter)中包含三個完全相同編碼器(Encoder),每個編碼器驅(qū)動一條串行T.M.D.S.通道(Channel)。輸入到每個編碼器的數(shù)據(jù)包括8bit象素數(shù)據(jù)和2bit控制信號" title="控制信號">控制信號(見圖3)。

?

?

?

在DE(Data Enable)信號的控制下,編碼器在任何合法時鐘驅(qū)動下,分別將象素數(shù)據(jù)和控制數(shù)據(jù)編碼并由發(fā)送器將編碼后的碼元串行發(fā)送到T.M.D.S.鏈路上。在DE有效期間(DE=1)對象素數(shù)據(jù)進行編碼發(fā)送,在DE無效期間(DE=0)對控制數(shù)據(jù)進行編碼發(fā)送。無論是對二者中的哪一項進行編碼,由編碼器輸出的都是串行的10bit碼元,并且最低有效位先送出。

2.2.2 時鐘與同步問題

時鐘與同步是DVI信號處理過程中至關重要的一環(huán)。以顯卡中圖形處理器提供的象素時鐘(Pixel Clock)為參考時鐘,在整個信號收發(fā)過程中,會存在三組不同頻率的時鐘信號,這三組時鐘信號通過鎖相環(huán)電路(PLL)進行同步控制。

從圖3可知,以象素時鐘的速度輸入到編碼器的8bit象素數(shù)據(jù)被變換成10bit的T.M.D.S.碼元,在T.M.D.S.通道內(nèi)串行傳輸。所以T.M.D.S. 碼元要以10倍象素的時鐘頻率進行碼元傳輸。在接收端,若要正確判斷所接收的碼元就需要用高于碼時鐘(Character Clock)的頻率對輸入信號進行采樣,所以又存在一個采樣時鐘(Sampling Clock)。例如:TI公司提供的DVI接收芯片[6]采用4倍過采樣技術對輸入信號采樣,在XGA分辨率(1024×768)、60Hz刷新率的情況下,象素時鐘為65MHz,則T.M.D.S.碼元時鐘將為650MHz,采樣時鐘將達到2.6GHz。

T.M.D.S.的先進編碼算法使得串行輸出的碼元流中包含了碼元同步信息,利用PLL技術使接收器和解碼器可以在串行的碼元流中正確測定碼元邊界、解碼象素數(shù)據(jù)。在T.M.D.S.輸出的編碼中,代表象素數(shù)據(jù)的編碼包含了5次或5次以下的變化信息,而代表控制信號的編碼包含了7次以上的變換信息。這些含有高變化信息的編碼在顯示的消隱時期內(nèi)被送出。解碼器可以唯一確定地識別這些高變換碼,PLL可以利用這些確定的信號作為相位校正的參考信號。

2.2.3 T.M.D.S.編碼與解碼算法

深入理解、靈活運用并實現(xiàn)這些先進的算法是芯片制造廠商最關心的問題。本文從使用者的角度出發(fā),以實用為原則對編碼及解碼算法進行分析[1]。

從圖3中可以看出,實際應用時最關心的行同步、場同步信號作為控制信息在藍基色(Blue[7:0])被編碼器編碼發(fā)送;其他通道的控制信號CTL[0:3]或CTL[0:9]都應接邏輯0,其中CTL0可以提供用戶使用,但有嚴格使用條件,非不得不用的情況下推薦接邏輯0。

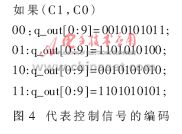

T.M.D.S.的每一條通道都由連續(xù)輸出的10bit串行編碼驅(qū)動。在顯示的消隱[5](DE=0)時間段內(nèi)編碼器輸出四個特定編碼,詳見圖4,也就是前面所說的可被解碼器唯一確定識別的四個編碼。在DE=1時編碼過程分為兩個階段,第一階段對8bit的象素數(shù)據(jù)進行最小變換生成9bit的最小變化碼,其中最低有效位與象素數(shù)據(jù)的最低有效位相同,第9位為變換方式標志位:0表示對象素數(shù)據(jù)進行異或非(XNOR)變換,1表示進行異或(XOR)變換;第二階段生成10bit的直流平衡碼:如果上一次編碼傳輸了過多的1且將要傳輸編碼中1比0多,則將此次編碼的低8位取反并在第10位置1,否則,將不作處理,直接傳輸。

?

每一條T.M.D.S.鏈路中含有與3個編碼器對應的3個解碼器。T.M.D.S.的解碼算法相對簡單一些。由于在消隱時間內(nèi)傳輸了特定的四個編碼,解碼器可以判斷DE的邏輯狀態(tài),若DE=0,則直接將對應的控制信號組合狀態(tài)送出。若DE=1,則根據(jù)第10位的情況決定低8位是否進行取反,根據(jù)第9位的信息決定對編碼進行的變化方式:為1,進行XOR(異或)變換;為0,進行XNOR(異或非)變換。在象素數(shù)據(jù)有效期間,行、場同步以及控制信息CTLX均保持恒定。通過上述解碼過程,行同步和場同步信號由藍基色通道解調(diào)出來,結(jié)合另外兩個通道解調(diào)出來的綠基色和紅基色,就可以進行視頻信息的數(shù)字方式顯示了。

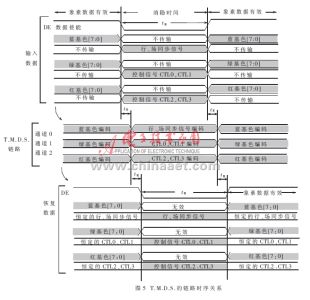

圖5是T.M.D.S.的鏈路時序關系,其中tB是對消隱信號持續(xù)時間的要求,要求tB≥128Tpixel,Tpixel為象素時鐘周期。tE和tR分別是編碼和解碼延遲時間,一般小于64Tpixel。

?

3 DVI接口應用指南

DVI接口提供了強大的數(shù)據(jù)傳輸率,其鏈路工作頻率很高,所以對器件的供電電壓、連接電纜的特性阻抗以及終端接插件的電氣特性都有非常嚴格和詳細的規(guī)定。這些都是DVI相關器件廠商要嚴格遵循的技術指標[1]。

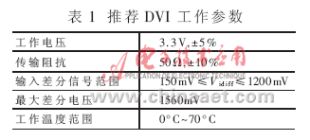

表1給出了實際應用最為關心的五個工作參數(shù),其他參數(shù)的詳細解釋見文獻[1]33~42。表2給出了DVI接口插頭信號線的定義。其中的DDC通道用于設備制造商向主機提供產(chǎn)品信息,這使DVI接口應用錦上添花。制造者可以在顯示設備中固化一段除設備本身特性參數(shù)以外的信息,結(jié)合計算機操作系統(tǒng),使系統(tǒng)識別設備的特征編號,從而達到保護自己產(chǎn)品產(chǎn)權的目的。當然,如果設計者不提供DDC信息,計算機操作系統(tǒng)就會把當前的顯示設備當成標準顯示設備來驅(qū)動。詳細情況請參閱文獻[2~5]。

?

?

?

目前,世界上幾大電子芯片制造廠商都提供DVI接口芯片, TI、ADI、Silicon Image等公司均提供不同性能參數(shù)的DVI發(fā)送或接收芯片,讀者可以到相應的網(wǎng)站查詢更詳盡的信息。

本文從計算機顯示技術的發(fā)展背景入手,詳細解釋和分析了DVI視頻標準。從方便實用、便于讀者理解的角度與原則出發(fā),直接針對實際應用中最為關心的編碼解碼算法、行同步場同步信號的提取、數(shù)據(jù)傳輸?shù)臅r鐘與同步問題、數(shù)據(jù)傳輸及恢復過程的時序要求等問題,簡要介紹了DDC-顯示數(shù)據(jù)通道的用途。

?

參考文獻

1 Digital Display Working Group. DVI Specification Revision?1.0. 1999;4

2 VESA Display Data Channel (DDC) Specification Version?3. 1997;12

3 VESA Plug and Play Standard Specification Version 1.1997;6

4 VESA Video Signal Standard Specification Version 1.6p

5 VESA Monitor Timing Specification Version 1.0 Revision 0.8

6 Texas Instruments. TI PanelBusTM User's Guide. 2000;9