處理器的發(fā)展

隨著集成度不斷提高,以及特征尺寸不斷縮小,處理器內(nèi)核電壓也開始降至 1V 以下,同時其電流消耗也隨著工作速度的提高而上升。工藝技術(shù)的改進(jìn)必須與負(fù)載點電源設(shè)計技術(shù)的發(fā)展要求同步。適用于二十世紀(jì)八九十年代的電源管理解決方案未必適用于目前的高性能處理器。為處理器提供核心動力面臨著若干技術(shù)上的挑戰(zhàn),如:如何放置大型旁路電容、浪涌電流、穩(wěn)壓精度與定序等。

能量的來源——大型旁路電容

處理器的總電流不單由電源自身提供,還由處理器的旁路以及電源的大型電容器提供。如果處理器工作強(qiáng)度發(fā)生突然變化導(dǎo)致負(fù)載急劇瞬變,那么浪涌電流首先由本地旁路電容提供——通常為較小的陶瓷電容,它們可針對負(fù)載變化做出迅速響應(yīng)。隨著處理速度從 500 MHz 增至 1GHz 乃至更高,我們還需要存儲更多能量的旁路電容,這是至關(guān)重要的。另一能量來源就是電源的大型電容。對于較新型的高性能處理器而言,旁路電容應(yīng)等于乃至大于電源的大型電容。為了避免造成穩(wěn)定性方面的問題,我們必須注意確保電源在增加旁路電容的情況下保持穩(wěn)定。即便電源評估板在基準(zhǔn)情況下工作良好無誤,但連接至負(fù)載時也可能出錯。為確保對電源的反饋環(huán)路進(jìn)行補(bǔ)償,以適應(yīng)更大的旁路電容。大型旁路電容必須彼此靠近,才能減小寄生效應(yīng)。

避免浪涌電流

帶有大型旁路電容的電源在啟動時可能發(fā)生問題,因為電源啟動時可能難以為大型旁路電容充足電并滿足處理器的負(fù)載要求。因此,電源可能會在過電流情況下斷電,電壓也可能在啟動時暫時下降(變?yōu)閱握{(diào)),這就可能導(dǎo)致處理器鎖死。為了減小浪涌電流,我們可延長內(nèi)核電壓電源的啟動時間,從而讓旁路電容慢慢充電。眾多 DC/DC 調(diào)節(jié)器均具有可調(diào)節(jié)的慢啟動引腳,以延長電壓上升時間。如果調(diào)節(jié)器不帶慢啟動引腳,那么我們可以采用外部 MOSFET 與 RC 充電方案來實現(xiàn)。超額電源設(shè)計是另一種解決浪涌電流的簡單方法,前提是設(shè)計人員能夠承受更高額定電流帶來的體積增大、價格升高的不利因素。如果處理器要求的話,我們也建議采用帶有電流限制的 DC/DC 調(diào)節(jié)器來保持單調(diào)的電壓斜線上升。

精度調(diào)節(jié)

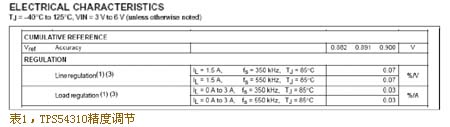

多年前的處理器要求電壓容限達(dá) 5% 之多,但隨著工藝節(jié)點不斷縮小,內(nèi)核電壓也降至 1V 以下,因此容限減小,甚至可能要求線路(工作輸入電壓范圍)、負(fù)載(工作輸出電流范圍)和工作溫度上的誤差容限不超過 3%。為確保精度調(diào)節(jié)能夠滿足處理器的要求,一般產(chǎn)品說明書的電氣特性部分保證設(shè)備在一定溫度和線路條件下的性能誤差在參考電壓 1% 的范圍內(nèi)。負(fù)載精度在3A情況下誤差最大為 0.09%。TPS54310 在各種線路、負(fù)載以及溫度條件下都能夠輕松實現(xiàn)誤差在 3% 以內(nèi)。表1 給出了TPS54310 的調(diào)節(jié)精度示例。

AC 精度調(diào)整

如果處理器在從低工作到高工作狀態(tài)變化中遇到動態(tài)負(fù)載范圍突變,它會迅速消耗掉更多的電流,這就會導(dǎo)致電壓下降。電源必須對電壓變化立即做出反應(yīng)以保持調(diào)節(jié)的準(zhǔn)確度(圖 1)。電壓峰值 (voltage spike) 應(yīng)不超過處理器的電壓容限規(guī)范,因此您應(yīng)準(zhǔn)確了解處理器產(chǎn)品說明書中所列的最大絕對內(nèi)核電壓要求是多少。為了提高電源在瞬態(tài)情況下的調(diào)節(jié)性能,我們可降低電感器的值,從而加速穩(wěn)壓器的響應(yīng)時間,并增加電容來提供更強(qiáng)的能量存儲能力,以適應(yīng)電壓下降以及電壓尖峰 (spike) 的情況。較好的做法是采用電源電壓監(jiān)控器來保護(hù)處理器,如果電壓在系統(tǒng)掉電過程中下降過低,那么就能提供良好的斷電重置功能。

定序

越來越多的處理器制造商開始針對核心與 I/O 上電定序提供建議的時序指南。一旦我們了解了時序要求,就可根據(jù)負(fù)載點電源設(shè)計者的要求來選擇適當(dāng)?shù)募夹g(shù)。對于雙電源而言,上電和斷電有幾種不同的方法,分別為:順序、同時排序和預(yù)偏置啟動。

如果內(nèi)核與 I/O 上電之間要求有幾毫秒的短暫間隔,那么可實施逐次排序 (sequential sequencing),具體順序隨意。其方法之一很簡單,就是將一個穩(wěn)壓器的POWERGOOD 引腳連接至另一個穩(wěn)壓器的 ENABLE 引腳即可。另一種方法則是采用熱插拔類型的定序集成電路來控制每個電壓電平的打開和關(guān)閉。這能夠?qū)崿F(xiàn)靈活性,但也會占用板級空間,并增加成本。

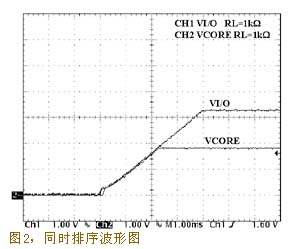

如果我們需要最小化上電與斷電期間的內(nèi)核與 I/O 電壓差動的話,那么就可采用同時排序。在實施同時排序時,內(nèi)核與 I/O 電壓彼此跟蹤,直至達(dá)到所理想的較低電壓電平為止。這時,較低的電壓在其穩(wěn)壓點上不再上升,而較高電壓繼續(xù)上升。德州儀器 (TI) 推出了帶有 TRACKIN 引腳的 TPS54x80 開關(guān)穩(wěn)壓器和帶有自動跟蹤功能的 PTH 系列 DC/DC 模塊,它們都可用于實施同時排序。圖2顯示了上電過程中的內(nèi)核與 I/O 電壓跟蹤情況。

如果在內(nèi)核處于“打開” 很久前就施加 I/O 電壓,而且內(nèi)核與 I/O 電壓之間必須存在最小增量,那么我們可方便地實施預(yù)偏置方法。在這種情況下,處理器制造商建議在上電前用二極管對內(nèi)核電壓進(jìn)行預(yù)偏置。二極管上的電壓下降在內(nèi)核與 I/O 電壓之間保持最小增量。采用同步補(bǔ)償 DC/DC 轉(zhuǎn)換器時,應(yīng)確保低壓側(cè)MOSFET 在啟動過程中保持關(guān)閉,否則已經(jīng)施加給內(nèi)核的失調(diào)電壓就會在 DC/DC 轉(zhuǎn)換器啟動時匯至接地,這可能會損壞二極管。內(nèi)核電壓隨二極管電壓下降而隨 I/O 電壓相應(yīng)變動,這表明處理器的內(nèi)核電壓在打開前已經(jīng)有了偏移值。隨后,內(nèi)核在失調(diào)電壓的基礎(chǔ)上斜線上升,直至達(dá)到所需的電壓電平為止。圖3給出了預(yù)偏置啟動波形圖的一個示例。TPS54x73 開關(guān)穩(wěn)壓器與 PTH 系列 DC/DC 模塊可用于實施預(yù)偏置啟動。

為 PLL 供電

許多較新型的處理器除了內(nèi)核與 I/O 電壓之外還要求單獨的 PLL(鎖相環(huán))電源。如果執(zhí)行代碼時PLL的電壓處于最小和最大容限之外,而且很不穩(wěn)定,那么就可能會導(dǎo)致數(shù)據(jù)損壞,或處理器鎖死。我們可采用簡單的預(yù)防措施,如使用電源電壓監(jiān)控器 (SVS) 等,來保護(hù)數(shù)據(jù)的完整性。內(nèi)核與 I/O 電壓穩(wěn)定后,PLL電壓的容限必須在一定的時鐘周期之內(nèi),如在執(zhí)行任何代碼前容限必須保持在最大1,000 個時鐘周期內(nèi)。某些處理器包括內(nèi)置的SVS功能,可讓PLL電壓趨于穩(wěn)定。如果您的處理器不具備上述的內(nèi)部處理功能,那么可采用電壓容限要求較嚴(yán)格的電源電壓監(jiān)控器來確認(rèn)內(nèi)核與 I/O 穩(wěn)定性。請確保監(jiān)控器的“RESET”時間大于 PLL 電壓穩(wěn)定下來所需的時鐘周期數(shù)。電源紋波抑制 (PSRR) 較強(qiáng)的低壓降調(diào)節(jié)器(如 TPS79xxx 系列)有助于降低不必要的噪聲尖峰進(jìn)入 PLL。

總結(jié)

目前,先進(jìn)的高性能處理器需要高性能負(fù)載點電源。更大的旁路電容、排序、浪涌電流、精度調(diào)節(jié)以及 PLL 供電電壓監(jiān)控都是目前負(fù)載點電源所必須解決的問題。5年以前適用的電源解決方案可能已不再適用于較新型的處理器。請記住,DC/DC穩(wěn)壓器是針對特定市場和終端設(shè)備而專門設(shè)計的,有著特定的成本和性能目標(biāo)。