摘 要: 通過(guò)研究立體液晶顯示" title="液晶顯示">液晶顯示器的圖像獲取及顯示接口,完成了從攝像到顯像的整體數(shù)字系統(tǒng)的電路部分設(shè)計(jì)。

關(guān)鍵詞: 立體液晶顯示 圖像獲取? CMOS圖像傳感器? FPGA

?

立體液晶顯示器是近年來(lái)新出現(xiàn)的虛擬現(xiàn)實(shí)顯示設(shè)備,它真實(shí)地再現(xiàn)場(chǎng)景的三維信息,顯示具有縱深感的圖像。其最大特點(diǎn)就是觀察者無(wú)需使用任何附加設(shè)備,直接用肉眼就可看到屏幕上顯示的立體圖像。觀測(cè)者可以更容易、更快速地理解真實(shí)的景深信息,更全面、更直觀地洞察圖像空間位置的實(shí)際分布狀況。

目前,國(guó)內(nèi)外的自由立體液晶顯示方式通常采用計(jì)算機(jī)采集圖像并存儲(chǔ),處理后輸出到液晶屏驅(qū)動(dòng)電路板,然后通過(guò)板載模數(shù)轉(zhuǎn)換模塊等處理后在液晶屏顯示立體圖像。這種方式主要由計(jì)算機(jī)進(jìn)行圖像采集和處理,其開(kāi)發(fā)周期短,但成本較高,體積較大,且需要液晶屏廠商提供驅(qū)動(dòng)電路板。因此,本文以FPGA為核心,設(shè)計(jì)并開(kāi)發(fā)了一套專用于立體液晶顯示的圖像采集和顯示系統(tǒng),可廣泛應(yīng)用于立體顯微、測(cè)繪領(lǐng)域、工程設(shè)計(jì)、軍事指揮等各個(gè)方面,有望形成產(chǎn)業(yè)規(guī)模。

1 方案設(shè)計(jì)

人們通常是兩眼同時(shí)觀看物體。由于兩只眼睛視軸的間距(約65mm)及同一物體在兩眼的構(gòu)像不一致形成的生理視差,使得左眼和右眼所接收到的視覺(jué)圖像不同。而大腦通過(guò)眼球的運(yùn)動(dòng)、調(diào)整,綜合這兩幅圖像的信息,產(chǎn)生立體感。本設(shè)計(jì)通過(guò)兩個(gè)完全相同的攝像機(jī),使兩個(gè)圖像平面位于同一平面Q,兩機(jī)坐標(biāo)軸平行,水平軸重合。通過(guò)兩攝像頭模擬人眼視差來(lái)恢復(fù)物體的深度信息。視差越大說(shuō)明物體離透鏡的距離越近;反之,則越遠(yuǎn)[1]。

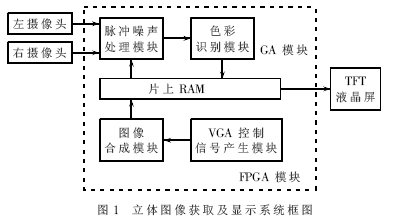

立體圖像獲取及顯示系統(tǒng)框圖如圖1所示。CMOS雙攝像頭嚴(yán)格水平放置,獲取立體圖像對(duì)。數(shù)字圖像數(shù)據(jù)并行進(jìn)入FPGA,利用片上" title="片上">片上RAM作幀緩存,然后由FPGA中的圖像處理模塊模擬大腦對(duì)兩眼圖像的綜合處理,按照VGA時(shí)序輸出到液晶屏顯示。

?

采用松下10.4英寸工控液晶屏EDTCB03Q2F,其接口為T(mén)TL電平,可用FPGA直接驅(qū)動(dòng),分辨率為640×480像素,色彩為262K(6bit/color),工作電壓3.3V。

以O(shè)mniVision公司的OV9620這一較為典型的彩色1/2英寸CMOS圖像傳感器模塊作為核心,實(shí)現(xiàn)雙芯片成像系統(tǒng)" title="成像系統(tǒng)">成像系統(tǒng)。該芯片采用Bayer模式濾波,其中有1 310 720個(gè)有效像素,其他像素用于黑電平補(bǔ)償和內(nèi)插。它支持SXGA和VGA兩種模式,支持?jǐn)z像和快拍,帶有光學(xué)黑電平校正、可編程" title="可編程">可編程/自動(dòng)曝光和增益控制、可編程白平衡控制、水平和垂直次采樣(4:2和4:2),可編程設(shè)定成像窗口和幀傳輸速率。內(nèi)部集成了SCCB控制接口便于訪問(wèn)其57個(gè)片內(nèi)寄存器,以實(shí)現(xiàn)對(duì)圖像傳感器芯片各種工作狀態(tài)參數(shù)的設(shè)定[2]。

采用FPGA實(shí)現(xiàn)數(shù)據(jù)的采集、處理及作為液晶屏的顯示接口。相對(duì)普通微處理器,F(xiàn)PGA時(shí)鐘頻率高、接口多,滿足高速數(shù)據(jù)傳輸需要;相對(duì)DSP而言,用戶I/O" title="I/O">I/O較多,不需擴(kuò)展即可實(shí)現(xiàn)數(shù)據(jù)實(shí)時(shí)采集和輸出,且便于實(shí)現(xiàn)外加存儲(chǔ)器擴(kuò)展。采用Xilinx公司的spartan3系列XC3S1000,系統(tǒng)門(mén)級(jí)為1000K,片上分布式RAM為120Kbit,分塊RAM為432Kbit。用戶I/O共391個(gè),片上鎖相環(huán)(DCM)4個(gè)[3]。它輸出紅、綠、藍(lán)各6位信號(hào),時(shí)鐘信號(hào)、行/場(chǎng)同步信號(hào)以及復(fù)合消隱信號(hào)在液晶屏顯示。

2 系統(tǒng)實(shí)現(xiàn)

2.1 雙攝像頭成像系統(tǒng)設(shè)計(jì)

該成像系統(tǒng)主要由兩個(gè)CMOS圖像傳感器、外圍控制電路和光學(xué)鏡頭組成。系統(tǒng)設(shè)計(jì)的主要任務(wù)是:(1)通過(guò)對(duì)管腳信號(hào)的控制設(shè)置成像系統(tǒng)的工作狀態(tài),輸出VGA模式;(2)提供系統(tǒng)的工作時(shí)鐘信號(hào),保證兩個(gè)攝像頭工作時(shí)鐘嚴(yán)格同步;(3)為系統(tǒng)提供穩(wěn)定的工作電源和電平設(shè)置;(4)光學(xué)鏡頭的設(shè)計(jì)。

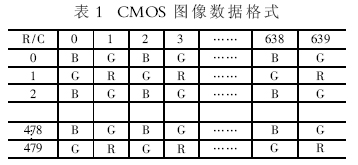

CMOS芯片為T(mén)TL電平接口,與FPGA兼容,其輸出數(shù)據(jù)格式如表1所示。它輸出10位并行紅、綠、藍(lán)信號(hào),行、場(chǎng)同步信號(hào),時(shí)鐘信號(hào)供FPGA采集。

2.2 FPGA設(shè)計(jì)

FPGA作為整個(gè)圖像系統(tǒng)的控制核心,實(shí)現(xiàn)數(shù)據(jù)采集接口及立體圖像合成的功能。采用Top-down設(shè)計(jì)方法,首先劃分為不同的功能模塊,用VHDL語(yǔ)言進(jìn)行行為級(jí)設(shè)計(jì),然后采用原理圖進(jìn)行頂層設(shè)計(jì),經(jīng)過(guò)編程、綜合、仿真和實(shí)現(xiàn),最后在電路板上進(jìn)行驗(yàn)證。

2.2.1 VGA控制信號(hào)的產(chǎn)生模塊

參照VESA VGA標(biāo)準(zhǔn),像素時(shí)鐘頻率為25.175MHz,行頻為31.469kHz,每行包括800點(diǎn),其中有效顯示640點(diǎn),行同步時(shí)間96點(diǎn),行消隱前肩16點(diǎn),行消隱后肩48點(diǎn),共160點(diǎn)行消隱期;場(chǎng)頻(刷新率)為59.94Hz,每場(chǎng)有525行,其中有效顯示480行,場(chǎng)同步時(shí)間2行,場(chǎng)消隱前肩11行,場(chǎng)消隱后肩32行,共45行[4]。

像素時(shí)鐘由FPGA外接50MHz晶振二分頻得到,作為液晶屏驅(qū)動(dòng)控制信號(hào)發(fā)生的基準(zhǔn),行頻和場(chǎng)頻相與得到數(shù)據(jù)有效信號(hào)(DE)。

2.2.2 脈沖噪聲處理

數(shù)字圖像的噪聲主要來(lái)源于圖像的獲取和傳輸過(guò)程。在成像階段,因?yàn)槌上裣到y(tǒng)的散焦、成像中的短暫停留、成像器材的固有缺陷等帶來(lái)傳感器噪聲;在傳輸過(guò)程中的噪聲主要因?yàn)殡娮与娐吩肼曇约皵?shù)據(jù)傳輸環(huán)境的不理想。這樣,造成圖像退化的主要因素為脈沖噪聲(椒鹽噪聲),在數(shù)字傳輸結(jié)束后,總是以最大值表現(xiàn)出來(lái)。即負(fù)脈沖以黑點(diǎn)(胡椒點(diǎn))出現(xiàn),正脈沖以白點(diǎn)(鹽點(diǎn))出現(xiàn),且具有小面積的特點(diǎn)。由于FPGA片上存儲(chǔ)資源有限,以及視頻流固有的限制,只能參考當(dāng)前像素之前的像素進(jìn)行處理。考慮到距離較遠(yuǎn)的像素相關(guān)性較小,如圖2所示:以像素5為當(dāng)前像素,選取1,2,3,4像素作為參考。標(biāo)定后,脈沖噪聲總是以數(shù)字化最大值表現(xiàn)出來(lái),即黑椒點(diǎn)為0,鹽點(diǎn)為255。當(dāng)色彩數(shù)據(jù)進(jìn)入FPGA時(shí),首先判斷其數(shù)值:如果是椒鹽點(diǎn),則該數(shù)據(jù)取1,2,3,4像素的該色彩分量平均值;如果不是椒鹽點(diǎn),則送入色彩識(shí)別模塊。

2.2.3 色彩識(shí)別模塊

如表1所示,CMOS攝像頭輸出格式為:第一行BGBGBG……,第二行GRGRGR……,即RGB信號(hào)按此順序串行輸出,而液晶屏接收RGB信號(hào)并行輸入,必須識(shí)別出輸入數(shù)據(jù)屬于何種色彩分量,經(jīng)組合后輸出到數(shù)據(jù)處理模塊進(jìn)行處理。

采用ModelSim對(duì)色彩識(shí)別模塊進(jìn)行仿真,結(jié)果如圖3所示。攝像頭幀頻(vsIn)輸出一個(gè)脈沖表示一幀到來(lái)時(shí),若行頻(hsIn)有效,則第一行開(kāi)始,數(shù)據(jù)端口(dataIn)中的數(shù)據(jù)依次輸出到藍(lán)色分量端口(bOut)、綠色分量端口(gOut);若行頻無(wú)效,則無(wú)數(shù)據(jù)輸出;第二行依次按照綠色分量端口(gOut)、紅色分量端口(rOut)……如此循環(huán),使得相鄰四個(gè)像素共享藍(lán)色和紅色分量,橫向相鄰的兩個(gè)像素共享綠色分量。數(shù)據(jù)經(jīng)過(guò)判斷組合后,RGB信號(hào)并行存儲(chǔ)到片上RAM,加快處理速度,便于實(shí)時(shí)輸出至液晶屏。

2.2.4 圖像合成模塊

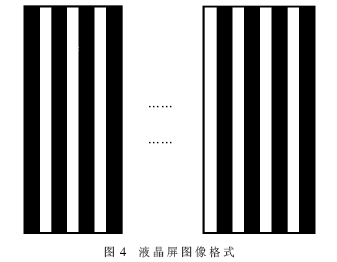

液晶屏上采用光柵對(duì)圖像進(jìn)行空分處理,實(shí)現(xiàn)雙眼視差,只需對(duì)其輸入相應(yīng)數(shù)據(jù)即可實(shí)現(xiàn)立體顯示。兩個(gè)攝像頭的圖像數(shù)據(jù)并行讀入(由于液晶屏接收RGB各6位進(jìn)行顯示,故只讀入攝像頭的高6位),經(jīng)噪聲處理及色彩識(shí)別并組合后放入片上RAM進(jìn)行緩存。在VGA控制信號(hào)中的行、場(chǎng)頻控制下,計(jì)算RAM地址,從片上RAM中讀出數(shù)據(jù)并輸出至液晶屏,輸出效果如圖4。其中黑色表示左攝像頭數(shù)據(jù),白色表示右攝像頭數(shù)據(jù),以像素為單位交替出現(xiàn),即奇數(shù)列為左攝像頭數(shù)據(jù),偶數(shù)列為右攝像頭數(shù)據(jù)。

本設(shè)計(jì)采用雙CMOS攝像頭模擬人眼獲取圖像。以FPGA為核心設(shè)計(jì)了圖像采集、處理和顯示接口,其圖像數(shù)據(jù)可直接輸出到TTL接口的液晶屏顯示。對(duì)于目前市場(chǎng)上大部分LVDS接口的液晶屏,只需修改FPGA的I/O屬性即可,無(wú)需液晶屏廠家提供驅(qū)動(dòng)電路板,實(shí)現(xiàn)了立體液晶顯示圖像采集和顯示系統(tǒng)的最小化設(shè)計(jì),目前已成功運(yùn)用于實(shí)時(shí)圖像的立體液晶顯示。整個(gè)系統(tǒng)結(jié)構(gòu)緊湊,擴(kuò)展性強(qiáng),生產(chǎn)成本低。此外,該系統(tǒng)只需對(duì)FPGA進(jìn)行重新編程即可用于其他多路視頻采集、處理及顯示方案。

參考文獻(xiàn)

[1] 譚 軍,陸 波,余桂豐.立體電視技術(shù)的發(fā)展概況及基本原理[J].中國(guó)有線電視,2004,(12):25-27.

[2] OmniVision Technologies Inc.OV9620 CMOS SXGA(1.3?MPixel) CamerachipTM datasheet Version 2.5.2003,9.

[3] Xilinx Inc.The Spartan-3 Family Data Sheet.DS099,2005,8.

[4] 徐 欣,于紅旗,易 凡等.基于FPGA的嵌入式系統(tǒng)設(shè)計(jì)[M].北京:機(jī)械工業(yè)出版社,2005.

本課題受?chē)?guó)家“863計(jì)劃”(2005AA311020)和江蘇省高技術(shù)研究計(jì)劃(BG2004031)資助