以太網(Ethernet)作為應用最廣泛的局域網技術異軍突起,已經迅速走向工業(yè)自動化控制領域的前臺。CPCI總線系統(tǒng)插槽有限,設計基于CPCI總線的多網口卡可節(jié)省空間,又可以滿足狀態(tài)監(jiān)測及故障診斷系統(tǒng)要求的實時和大數(shù)據量傳輸。

1 模塊總體設計

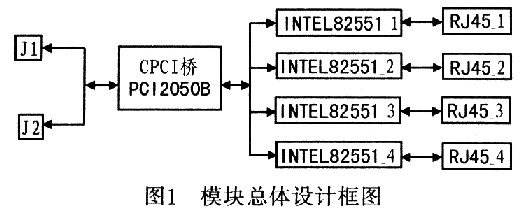

該模塊采用CPCI并行總線進行設計。圖1給出該模塊總體設計框圖,其中,通過PCI橋擴展總線分別連接4片INTEL82551,由于INTEL82551內部已集成PCI接口,PCI橋可實現(xiàn)與INTEL82551之間的無縫連接。J1和J2為CPCI的接口插件。

2 CPCI總線結構模塊

2.1 原理和結構

在1條PCI總線上如果連接過多的電氣負載或設備,總線不能正常工作。通過在系統(tǒng)內另外增加1條或多條PCI總線,問題可以得到解決。在系統(tǒng)內擴展另1條PCI總線,唯一的方法是使用PCI-PCI(即P2P)橋進行系統(tǒng)擴展。P2P橋是特殊的PCI設備,可把系統(tǒng)中的PCI總線粘合在一起。P2P橋在系統(tǒng)中連接主從兩條PCI總線,它作為上一級總線的一個負載,通過對PCI信號的重新驅動和仲裁,而向下可以驅動一個總線段。

其作用是協(xié)調2條PCI總線之間的數(shù)據傳輸,監(jiān)視在這兩條PCI總線上啟動的所有交易,并決定是否將交易傳送通過另一條PCI總線。當橋確定將一條總線上的交易傳送到另一條總線時,橋必須充當交易總線的總線目標,以及交易的目的總線的主設備。系統(tǒng)設計者也可以安裝多個P2P橋。

2.2 PCI2050B簡介

根據系統(tǒng)集成的特性,這里選擇TI公司的PCI2050B橋接器來實現(xiàn)P2P橋。PCI2050B屬于透明的PCI-PCI橋,在2個32位最高工作頻率66 MHz的PCI總線之間提供橋連接。該橋支持突發(fā)模式(burstmode transfers),極大增加了數(shù)據的吞吐量,橋的總線數(shù)據路徑(tmstraffic paths)獨立工作。橋的主、從總線分別可以工作在3.3 V或者5 V的環(huán)境下,而橋的核心邏輯工作在3.3 V,以減少功耗。主機軟件通過內部寄存器對橋進行操作。通過內部寄存器既可以得到標準PCI的狀態(tài),也可以對主、從總線進行控制。橋的PCI配置頭只能通過主PCI接口來操作。PC-I2050B帶9個從總線,除了為每個從總線提供內部仲裁外,也可為系統(tǒng)提供外部仲裁。PCI2050B提供10個從側時鐘輸出。

2.3 PCI橋的設計

根據該模塊總體設計框圖,系統(tǒng)設計需要注意以下幾個方面。

2.3.1 時鐘設計

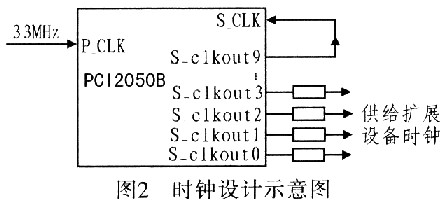

圖2為PCI2050B的時鐘設計框圖。

該時鐘設計要點如下:

1)PCI2050B有2個獨立的時鐘域,主接口受主側輸入時鐘P_CLK的控制,從接口受從側輸入時鐘S_CLK的控制。這2個時鐘相互獨立,但保持同步,而且從側的時鐘頻率不能高于主側的時鐘頻率。P_CLK與S_CLK最大延時不得超過7ns,S_CLK不能超前P_CLK。

2)PCI2050B的從側有10個時鐘輸出S-clkout[9:0],其中9個時鐘輸出可以供給擴展的PCI槽,為保證時鐘輸出同步,另1個必須反饋給從側的輸入時鐘S_CLK,每一個時鐘只能驅動一個負載。

3)為了減小時鐘的信號反射,輸出到擴展槽的9個時鐘輸出必須在起始端加串聯(lián)電阻匹配,匹配電阻阻值與電路板特征阻抗大小有關,對65 Ω的傳輸線,選用50 Ω串聯(lián)匹配電阻。

4)為了減小這些時鐘之間的抖動(skew),供給擴展槽(或擴展設備)的9根時鐘線(9個S_clkout)與S_CLK必須等長。所以,從S_clkout[9]輸出反饋至S_CLK的時鐘線長度應等于從PCI2050B的時鐘輸出引腳到擴展設備的時鐘線的總長。本模塊擴展4個網口,使用PCI2050B從側的4個輸出時鐘,在PCB布線中這4根時鐘線與反饋時鐘線必須等長。

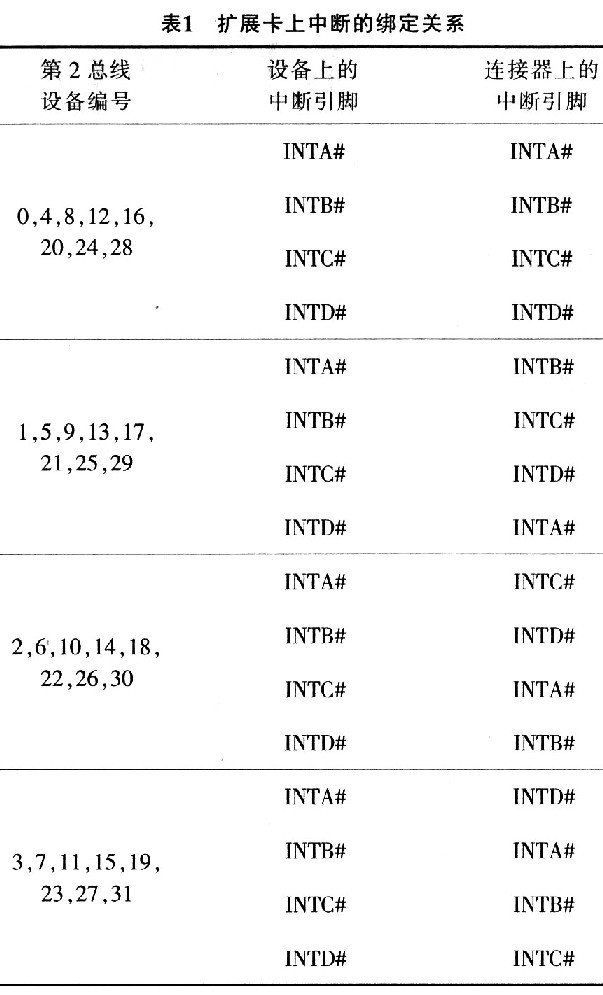

2.3.2 中斷設計和IDSEL映射

PCI2050B支持9個從設備,在初始化配置空間讀寫時,PCI2050B作為上一級PCI總線的操作對象,提供了IDSEL引腳進行器件選擇,該引腳可以連接到高24位PCI總線中的任意一根。同時,為了減少地址線的容性負載,需要在該信號連線上串接一只1 kΩ的電阻。本模塊僅擴展一級總線,PCI2050B主側的IDSEL引腳直接連接到CPCI插座J1的IDSEL。對于二級總線側的PCI器件(本模塊為INTEL82551),其IDSEL引腳經過1 kΩ的電阻連接到PCI2050B的S_AD31S_ADl6引腳的任意一根。來自從側上的設備的INT線不通過橋。如果橋位于一個插入卡上,從側設備的中斷線直接接到連接器的中斷引腳(INTA#~INTD#)。本模塊中,PCI2050B是一個橋設備,INTEL82551的中斷引腳直接連接到J1的中斷引腳。所有從設備的中斷線的連接與設備編號(即IDSEL線的連接)有綁定關系,對應關系如表1所示。4片INTEL8255l的IDSEL引腳分別連接到S_AD28、S-AD29、S_AD30和S_AD31,對應的設備編號為12、13、14、15,則器件的中斷引腳INT#對應連接到J1的INTA#、INTB#、INTC#、INTD#。

2.3.3 PCI2050B工作模式的選擇

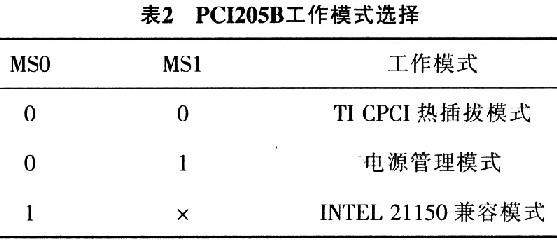

PCI2050B有3種工作模式可供選擇:TI CPCI熱插拔模式、電源管理模式和INTEL 21150兼容模式。選擇引腳分別為MSO,MSl,模式選擇定義如表2所示。

根據CPCI總線應用設計的需要,筆者選擇了TI CPCI熱插拔工作模式。當PCI2050B選擇TI CPCI熱插拔工作模式時,為了確保熱插拔邏輯的正常工作,要求必須將HS_SWICH/GPI03引腳和HSENUM引腳上拉,同時,由于沒有使用PCI2050B的關于GPI0引腳,且因為這些引腳在缺省條件下定義為輸入腳,為了避免誤觸發(fā),將這些引腳全部上拉。

3 以太網接口

本網卡使用4片INTEL82551、4片EEPROM 93C46和4片PE68515實現(xiàn)4路以太網網絡接口。INTEL82551是Intel公司的一款高集成的以太網控制器,其主要功能是實現(xiàn)以太網幀的收發(fā)。它集成了10Base-T/lOOBase-T MAC控制器和10Base-T/100Base-T PHY控制器,支持數(shù)據的全雙工或半雙工傳輸,支持自動協(xié)商,支持10/100 Mb/s傳輸速率,支持流控機制。

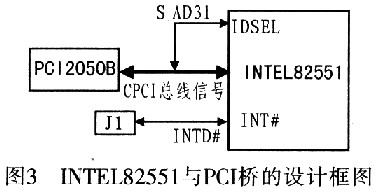

3.1 INTEL82551與PCI橋的接口設計

每片INTEL82551的CPCI總線信號連接到PCI2050B的從側,應特別注意的是信號IDSEL和INT#根據表1一一對應,否則模塊插到系統(tǒng)槽上,系統(tǒng)不能正確驅動模塊。其中1路器件的電路連接,如圖3所示。器件的IDSEL連接到S_AD31上,則器件的中斷INT#連接到J1的INTD#上。

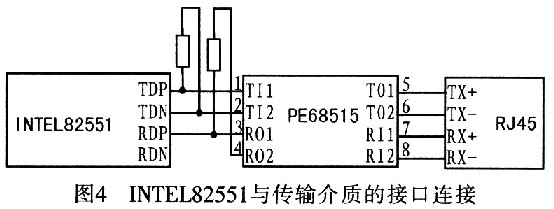

3.2 Intel82551與傳輸介質接口

使用4片PE68515和4個RJ-45實現(xiàn)傳輸介質接口。每一路接口電路連接,如圖4所示。

3.3 網卡調試

PCB電裝完后,檢查各器件及其他電路是否有虛焊,網卡插于CPCI機箱插槽,在系統(tǒng)設備管理器中可看到模塊屬性,如IDSEL連接AD31,則屬性為PCI SLOTl(PCI總線N,設備15,功能O)(N為總線編號)。用EEUPDATE對網卡配置后,模塊可正常收發(fā)數(shù)據。

4 結束語

本四網口模塊符合PCI2.2規(guī)范,已成功應用于3U CPCI機箱的Windows平臺。根據需要可擴展為八網口的CPCI卡,此系列基于CPCI多網口卡,可廣泛用于各類測試設備、有線通信等領域。