0 引言

穿墻雷達(dá)是一種能夠穿透非金屬墻壁,并對(duì)墻壁后面人員或物體進(jìn)行探測(cè)、追蹤和定位的雷達(dá)系統(tǒng),一般采用超帶寬步進(jìn)體制。本實(shí)驗(yàn)室搭建的穿墻雷達(dá)系統(tǒng)需要一個(gè)l~2 GHz頻帶的信號(hào)源。根據(jù)系統(tǒng)帶寬以及雜散、相位噪聲等系統(tǒng)參數(shù)要求,筆者采用DDS+PLL混合頻率合成技術(shù),并充分利用AD9858等高集成化芯片,設(shè)計(jì)了一種可滿足系統(tǒng)信號(hào)源輸出要求的頻率合成器。

1 系統(tǒng)原理與結(jié)構(gòu)

DDS+PLL頻率合成器的基本原理是用一個(gè)低頻、高分辨率的DDS頻率來(lái)激勵(lì)或者插入PLL,然后將兩者的優(yōu)勢(shì)結(jié)合起來(lái)產(chǎn)生高品質(zhì)的信號(hào)源。

本文采用DDS激勵(lì)PLL的方案來(lái)滿足系統(tǒng)要求。本系統(tǒng)采用高穩(wěn)定的頻率源作為系統(tǒng)參考時(shí)鐘;并在單片機(jī)的控制下把頻率控制字和相位控制字寫到DDS內(nèi)部寄存器,然后由DDS產(chǎn)生一個(gè)頻率和相位都可以編程控制的模擬正弦波輸出,并把DDS的輸出作為PLL的參考信號(hào),最后根據(jù)穿墻雷達(dá)系統(tǒng)要求的信號(hào)頻率來(lái)設(shè)定分頻器的分頻比N,從而得到系統(tǒng)輸出信號(hào)。此類方案實(shí)現(xiàn)的信號(hào)源具有較高的頻率和較快的頻率轉(zhuǎn)換速度,而AD9858等集成芯片的高性能則使系統(tǒng)在雜散和噪聲方面也能達(dá)到要求。

2 電路設(shè)計(jì)

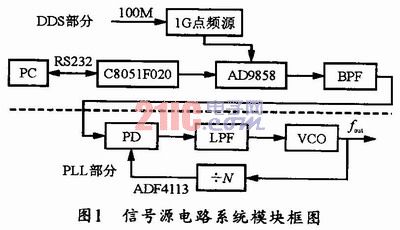

本系統(tǒng)的電路設(shè)計(jì)主要分為DDS模塊和PLL模塊兩大部分,其系統(tǒng)框圖如圖l所示。

2.1 DDS模塊電路設(shè)計(jì)

本系統(tǒng)由DDS來(lái)保障較高的頻率分辨率和良好的參考源性能,而由PLL提高頻率輸出并濾除DDS輸出雜散,跳頻方式則通過(guò)對(duì)DDS和PLL的控制來(lái)實(shí)現(xiàn)。

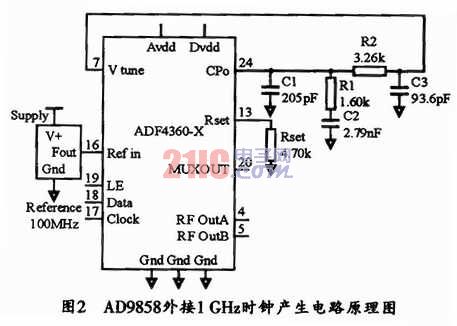

AD9858的外接1 GHz時(shí)鐘點(diǎn)頻源可使用ADF4360_2生成,并可使用ADIsimPLL仿真,其基本電路原理圖如圖2所示。ADF4360_2的參考時(shí)鐘使用100MHz有源晶振,實(shí)際電路設(shè)計(jì)時(shí)需加入濾波后再接到Ref端口。輸出頻率為2 GHz,可以設(shè)置為2分頻輸出,也可以在AD9858芯片內(nèi)部設(shè)置為2分頻輸入。

控制AD9858主要使用C8051F020的特殊功能寄存器SFR、FIASH和外部存儲(chǔ)器接口EMIF。其中SFR提供對(duì)CIP-51的資源和外設(shè)的控制以及CIP -51與這些資源和外設(shè)之間的數(shù)據(jù)交換;FLASH是C8052F020的內(nèi)部存儲(chǔ)器,可通過(guò)JTAG接口對(duì)其編程;外部存儲(chǔ)器接口EMIF則御用訪問(wèn)片外存儲(chǔ)器。配置EMIF的流程如下:

(1)將EMIF選到低端口(P3,P2,Pl,P0)或高端口(P7,P6,P5,P4);

(2)選擇復(fù)用或非復(fù)用方式;

(3)選擇存儲(chǔ)器模式(只用片內(nèi),只用片外;不帶塊選擇分片、帶塊選擇分片等);

(4)設(shè)置與片外存儲(chǔ)器的時(shí)序;

(5)選擇相關(guān)端口的輸出方式(寄存器PnMDOUT和P740UT)。

2.2 AD9858的基本原理和性能

DDS是基于查找表的數(shù)字頻率發(fā)生器。DDS器件工作時(shí),其頻率控制字K在每一個(gè)時(shí)鐘周期內(nèi),其余相位累加器累加一次,而得到的相位值

(O~2π)在每一個(gè)時(shí)鐘周期內(nèi)則以二進(jìn)制碼的形式去尋址正弦查詢表ROM,并將相位信息轉(zhuǎn)變成相應(yīng)的數(shù)字化正弦幅度值,ROM輸出的數(shù)字化波形經(jīng)數(shù)模轉(zhuǎn)換器(DAC)后,用于實(shí)現(xiàn)數(shù)字化信號(hào)到模擬信號(hào)的轉(zhuǎn)變,最后,DAC輸出的階梯序列波再通過(guò)低通濾波器(LPF)平滑后,就可得到一個(gè)純凈的正弦信號(hào)。

AD9858的10位數(shù)模轉(zhuǎn)換器可以工作到lGsps,并能夠產(chǎn)生高達(dá)450MHz的頻率階變模擬輸出正弦波,同時(shí)具有快速調(diào)頻和細(xì)微的頻率分辨率(32位頻率分辨率)。AD9858內(nèi)部有集成的電荷泵(CP)和相位檢測(cè)器(PFD),可以將高速DDS和鎖相環(huán)(PLL結(jié)合使用)在片內(nèi)模擬混頻,也可以使DDS、PLL和混頻器結(jié)合使用。

AD9858有單音和掃頻兩種工作模式。在單音模式下。AD9858可產(chǎn)生由內(nèi)部寄存器FTW控制的單頻輸出信號(hào)。輸出頻率與系統(tǒng)時(shí)鐘的關(guān)系可由如下公式確定:

對(duì)于AD9858,N=32。可見其頻率可以通過(guò)改變FTW任意改變,也可以通過(guò)外部引腳來(lái)選擇提前設(shè)定在4個(gè)存儲(chǔ)在寄存器上的頻率值來(lái)實(shí)現(xiàn)快速跳頻。

而在掃頻模式下,用戶需要通過(guò)頻率控制字(FTW)、頻率轉(zhuǎn)換控制字(DFTW)、頻率斜率控制字(DFRRW)來(lái)設(shè)定頻率的掃頻初始值、頻率步進(jìn)值和頻率步進(jìn)時(shí)間,從而實(shí)現(xiàn)掃頻。

在設(shè)計(jì)DDS時(shí)需要仔細(xì)考慮輸入和輸出的頻段:當(dāng)輸出頻率靠近fc/n(其中n=3,4,5,6,7;fc為DDS的時(shí)鐘頻率)時(shí),差頻信號(hào)產(chǎn)生的雜散離輸出頻率很近,以至于無(wú)法使用濾波器器濾除,這種窄帶雜散經(jīng)過(guò)倍頻還會(huì)繼續(xù)惡化,嚴(yán)重惡化雜散性能,所以,設(shè)計(jì)時(shí)不能使用DDS輸出頻段靠近和跨越fc/n的頻點(diǎn)(其中n=3,4,5,6,7)。本系統(tǒng)中DDS的輸入頻率為1GHz。因此輸出頻段為50~100 MHz。這樣,輸出頻道附近就不會(huì)出現(xiàn)大的雜散。

2.3 PLL模塊設(shè)計(jì)

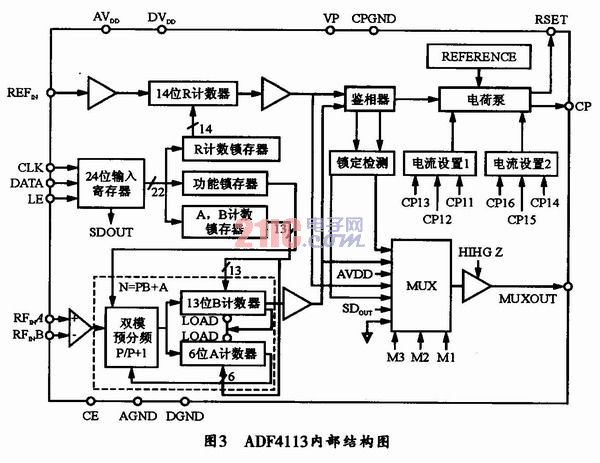

PLL模塊包括ADF4113和輸出帶寬為1~2 GHz壓控振蕩器。ADF4113的內(nèi)部結(jié)構(gòu)如圖3所示,它由低噪聲數(shù)字鑒相器、高精度電荷泵、可編程參考分頻器(R分頻器)、可編程A,B計(jì)數(shù)器以及雙模分頻器P/P+1組成。其中6位A計(jì)數(shù)器、13位B計(jì)數(shù)器與雙模分頻器共同組成了N分頻器,分頻比為N=BP+A。數(shù)字鑒相器用來(lái)對(duì)R計(jì)數(shù)器和N計(jì)數(shù)器的輸出相位進(jìn)行比較,然后輸出一個(gè)與二者相位誤差成正比的誤差電壓。該電壓經(jīng)外部濾波器濾波后可控制外接VCO,從而構(gòu)成一個(gè)完整的頻率合成器。其輸出頻率為:

其中,fREFIN為參考頻率。

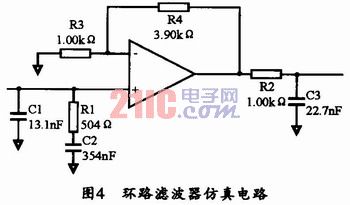

環(huán)路濾波器是鎖相環(huán)電路中很重要的一個(gè)部分,它的性能好壞直接關(guān)系到鎖相輸出的相位噪聲和雜散指標(biāo)。設(shè)計(jì)時(shí)仍然可使用AD公司提供的PLL仿真軟件ADLsimPLL來(lái)生成。其各項(xiàng)參數(shù)設(shè)置為:輸出頻率為1~2 GHz。鑒相頻率為5 MHz,使用有源濾波,放大器輸出電壓范圍為-15~+15V。該設(shè)置可以滿足后級(jí)電路VCO的控制要求。其環(huán)路濾波器仿真電路如圖4所示。

壓控振蕩器芯片可根據(jù)系統(tǒng)帶寬等要求選用Z-com公司的V585MFA8,該器件的主要技術(shù)指標(biāo)如表1所列。

注意到VCO的工作電壓為10 V。由于本實(shí)驗(yàn)電路使用了實(shí)驗(yàn)室的直流穩(wěn)壓源OFl722M-2。該電源可以提供0~36V的連續(xù)電壓。如果使用芯片供電,整個(gè)電路需提供3.3 V、5 V、10 V、12 V等4個(gè)電壓值,故可使用線性電壓元件來(lái)實(shí)現(xiàn),但要注意電源布局及走線。

2.4 帶通濾波器設(shè)計(jì)

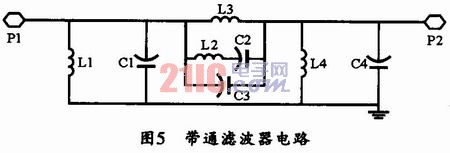

帶通濾波器的設(shè)計(jì)方案直接影響到輸出信號(hào)的質(zhì)量。DDS輸出信號(hào)中含有豐富的高頻成份,考慮到電路規(guī)模和系統(tǒng)要求,本文采用常用的橢圓濾波方案,并使用三階濾波器濾除雜散。同時(shí)使用ADS濾波器輔助設(shè)計(jì),其具體電路如圖5所示。其中,L1和L4為41 nH;Cl和C4為137 pF;L2選52 nH;L3選54 nH;C2選108 pF;C3選103 pF。

3 印刷版設(shè)計(jì)

本設(shè)計(jì)的印制板可分為兩個(gè)電路板設(shè)計(jì),即把DDS部分與鎖相環(huán)部分做成一塊,而把電源和參考時(shí)鐘做成另一塊。兩塊電路板采用絕緣子穿孔相連。這樣可以有效降低電源部分對(duì)DDS與鎖相部分的干擾。印刷板都需要大面積鋪地,所有的旁路電路均應(yīng)盡量靠近器件,所有的信號(hào)線盡可能的短,而且不能有90度轉(zhuǎn)角。

4 結(jié)束語(yǔ)

本文采用AD9858和AD4360_2等高性能芯片來(lái)實(shí)現(xiàn)1~2GHz符合穿墻雷達(dá)系統(tǒng)的信號(hào)源系統(tǒng)設(shè)計(jì),同時(shí)在電路布局等方面都進(jìn)行了良好的設(shè)計(jì),因而使輸出信號(hào)在雜波抑制和相位噪聲方面都有良好的特性。完全可以滿足穿墻雷達(dá)實(shí)驗(yàn)系統(tǒng)信號(hào)源部分的設(shè)計(jì)要求。