由于半導(dǎo)體工藝進(jìn)步,相同芯片面積中可以放入愈來愈多的晶體管,致使這10多年來業(yè)界開始積極發(fā)展所謂的系統(tǒng)單芯片SoC,而可組態(tài)性處理器IP概念就像自助餐式的自組拼盤,提供嵌入式系統(tǒng)更寬廣的應(yīng)用空間…

過往需多顆芯片才能組構(gòu)的運(yùn)算系統(tǒng),現(xiàn)在透過半導(dǎo)體的整合工藝,單一SoC芯片即可實(shí)現(xiàn),但無論是用多顆芯片構(gòu)成的系統(tǒng),還是用單顆芯片就實(shí)現(xiàn)的系統(tǒng),系統(tǒng)中都包含各種屬性、功效電路,而在SoC需求愈來愈普遍,同時(shí)內(nèi)部設(shè)計(jì)愈形復(fù)雜后,芯片公司已難完全以自力、自主完成SoC設(shè)計(jì),若完全自力設(shè)計(jì),則電路的設(shè)計(jì)、驗(yàn)證過程費(fèi)時(shí)更長(zhǎng),影響SoC上市時(shí)間與研發(fā)成本。

為能用更簡(jiǎn)便、快速方式完成SoC設(shè)計(jì),半導(dǎo)體產(chǎn)業(yè)衍生新經(jīng)營(yíng)型態(tài)的公司,稱為IP Provider(硅知識(shí)產(chǎn)權(quán)供貨商),IP Provider只專注于芯片內(nèi)各功效電路研發(fā)設(shè)計(jì),并將功效電路設(shè)計(jì)成果授權(quán)給其它業(yè)者使用,而技術(shù)授權(quán)費(fèi)或芯片量產(chǎn)后的權(quán)利金,就成了IP Provider的主要收益來源。

不過,并不是只有IP Provider才能授權(quán)芯片的功效電路設(shè)計(jì),半導(dǎo)體產(chǎn)業(yè)中其它經(jīng)營(yíng)型態(tài)業(yè)者,也提供類似服務(wù),包括整合裝置制造商(IDM)、晶圓代工廠(Foundry)、無晶圓廠的芯片公司(Fabless)、芯片設(shè)計(jì)服務(wù)業(yè)者(Design House)、以及電路設(shè)計(jì)自動(dòng)化的工具供貨商(EDA Vendor)等也多有提供,差別只在于專營(yíng)與兼營(yíng),IP Provider屬專營(yíng)業(yè)者,其余各種型態(tài)的業(yè)者屬于兼營(yíng)。

事實(shí)上硅知識(shí)產(chǎn)權(quán)概念最初來自Foundry,F(xiàn)oundry業(yè)者為讓投單客戶芯片電路設(shè)計(jì)可盡快投產(chǎn),所以向客戶提供現(xiàn)成、已完成各項(xiàng)驗(yàn)證的功效電路設(shè)計(jì),當(dāng)這類型的設(shè)計(jì)累積數(shù)量夠多后,才逐漸開展出更高層次的硅知識(shí)產(chǎn)權(quán)產(chǎn)業(yè)。

處理器IP是SoC的最核心

了解IP能簡(jiǎn)化、加速SoC設(shè)計(jì)后。如今的SoC,芯片內(nèi)多半會(huì)使用1個(gè)或1個(gè)以上的IP,在用及各種IP中,又以控制器、處理器的IP最為基礎(chǔ)與關(guān)鍵。每顆SoC設(shè)計(jì)之初就要決定控制器/處理器架構(gòu),此等于決定SoC的最核心設(shè)計(jì),接著才能決定外圍功效電路,最后才能完成SoC整體設(shè)計(jì)。

也因?yàn)榭刂破?處理器的需求最基礎(chǔ)、普遍,所以如英國(guó)ARM(安謀國(guó)際)、美國(guó)MIPS(美普思)等業(yè)者在硅知識(shí)產(chǎn)權(quán)業(yè)界中相當(dāng)活躍,因?yàn)锳RM、MIPS等皆以處理器的IP授權(quán)為主業(yè)務(wù)。今日多數(shù)SoC均直接使用ARM、MIPS業(yè)者授權(quán)的處理器IP,已少有完全自力設(shè)計(jì)的SoC執(zhí)行核心。

圖 英國(guó)ARC公司可組態(tài)性處理器IP的展望規(guī)劃圖(Roadmap),圖上半年為ARC 700系列的展望規(guī)劃,下半年則為600系列的展望規(guī)劃。

Soft IP與Hard IP之別

雖然IP可以加速SoC設(shè)計(jì),但進(jìn)一步還要了解IP層次,大體而言IP可分成Soft IP與Hard IP 2個(gè)層次;Soft IP是偏向電路功效邏輯層面設(shè)計(jì),而Hard IP則是除了具備電路功效邏輯外,連帶已完成芯片實(shí)際投產(chǎn)前的實(shí)體性電路設(shè)計(jì)。

如果SoC業(yè)者期望對(duì)IP部分電路設(shè)計(jì)能有較高的再修改性,或者是更高度的電路設(shè)計(jì)整合,則必須選擇Soft IP,反之Hard IP難以再修改,整合度也有限。不過Hard IP設(shè)計(jì)完成度較高,已經(jīng)完成邏輯、實(shí)體2部分的設(shè)計(jì),相對(duì)的Soft IP僅完成前期性的功效邏輯,所以就SoC整體設(shè)計(jì)的加速性而言,此方面Hard IP優(yōu)于Soft IP。(附注2)

Soft IP的調(diào)修彈性仍有其限

所以,若為了追求較高的設(shè)計(jì)彈性,則必須選擇Soft IP,但即便是Soft IP模式,其設(shè)計(jì)彈性也有限。以處理器IP來說,多數(shù)的處理器IP其處理架構(gòu)均已經(jīng)固定,如處理器內(nèi)有多少個(gè)緩存器、管線階數(shù)等,雖技術(shù)上依然可以對(duì)這些架構(gòu)再行調(diào)修,但I(xiàn)P的授權(quán)業(yè)者通常不樂見、甚至不允許這么做,因?yàn)閷?duì)架構(gòu)進(jìn)行調(diào)整將會(huì)阻礙執(zhí)行軟件的移植性與兼容性。

因此,提供處理器IP的業(yè)者,通常實(shí)行另一種作法,那就是提供多種型款(但各款的設(shè)計(jì)架構(gòu)皆已固定)的處理器IP讓客戶選擇,若客戶認(rèn)為某款的IP不合用,則可以再評(píng)估另一款I(lǐng)P,直到選定最貼近需求的款式為止。

可組態(tài)性處理器IP的意涵

用多種型款的現(xiàn)成固定式設(shè)計(jì),來因應(yīng)客戶對(duì)處理器IP的各種不同需求,這是目前較普遍的作法,事實(shí)上ARM、MIPS、PowerPC等皆是如此。然而業(yè)界也有另一種作法,就是提供更高度的彈性設(shè)計(jì),此稱為可組態(tài)性處理器(Configurable Processor)。

可組態(tài)性處理器,是SoC設(shè)計(jì)者可以決定處理器的細(xì)節(jié)設(shè)計(jì),包括增/減緩存器、執(zhí)行單元、指令數(shù)...等設(shè)計(jì),借以建構(gòu)出更合乎需求的處理器核心。如此,可組態(tài)性處理器IP,提供更高度的設(shè)計(jì)彈性,目前以可組態(tài)性著稱的處理器IP,主要有英國(guó)ARC公司的ARC 600、ARC 700核心,以及美國(guó)Tensilica公司的Xtensa 7、Xtensa LX2核心。

要注意的是,此類IP雖提供可組態(tài)性,但并不表示處理器內(nèi)的任何環(huán)節(jié)都可重新調(diào)整,仍有其不變的主架構(gòu)存在,倘若各環(huán)節(jié)都可以再行調(diào)修,此已等于是100%的自主設(shè)計(jì),如此就沒有向外取得IP授權(quán)的必要。

實(shí)行可組態(tài)性處理器IP的動(dòng)機(jī)

前面提到,為了更高的設(shè)計(jì)彈性、為了更切合設(shè)計(jì)要求,所以需要可組態(tài)性處理器IP,但「彈性」、「要求」仍是相當(dāng)浮泛的概念性形容,以下將更具體說明實(shí)行可組態(tài)性處理器IP的動(dòng)機(jī)。

1.減少芯片電路面積

將原本的多芯片系統(tǒng)整合成SoC,為的就是要精省系統(tǒng)電路面積,同時(shí)也精省實(shí)現(xiàn)成本,不過要將原有的多芯片整合成單芯片,多半要對(duì)電路功效進(jìn)行權(quán)衡取舍,甚至犧牲部分規(guī)格、性能、功效,所以設(shè)計(jì)時(shí)都會(huì)盡力縮小各功效電路面積,而可組態(tài)性處理器IP因具備更高彈性,能將「電路面積」視為第一要求,組態(tài)出占用面積最小的處理核心。

2.減少芯片的功耗用電

許多SoC是用于手持式應(yīng)用裝置中,手持式應(yīng)用裝置除力求芯片小體積化外,也相當(dāng)講究功耗用電,原因是手持裝置的電池電力有限。此外能源成本愈來愈高,用于機(jī)房設(shè)備內(nèi)的芯片也得講究省電,其它各類應(yīng)用芯片亦有類似趨勢(shì)發(fā)展。因此,可組態(tài)性處理器IP在組態(tài)時(shí),即能針對(duì)功耗用電進(jìn)行最佳化設(shè)計(jì)。

3.增加芯片的運(yùn)算效能、反應(yīng)速率

能以電路面積來組態(tài)、能以功耗用電來組態(tài),那么也可以從運(yùn)算效能為取向來進(jìn)行組態(tài),尤其是硬性實(shí)時(shí)控制(Hard Real-Time Control)的應(yīng)用格外有需求。事實(shí)上,一直以來處理器首要講究的特性表現(xiàn),是價(jià)格效能比(Price/Performance Ratio),近年來才開始重視功耗用電性的每瓦效能比(Performance Per Watt)。

4.減少芯片的授權(quán)成本

使用處理器IP要支付一筆技術(shù)授權(quán)費(fèi),且在SoC設(shè)計(jì)完成、投入量產(chǎn)后,還要針對(duì)每顆出廠后的SoC抽取量產(chǎn)權(quán)利金,為了減少授權(quán)費(fèi)及權(quán)利金等成本支出,實(shí)行可組態(tài)作法有機(jī)會(huì)減少此方面的成本支出,例如不需要浮點(diǎn)運(yùn)算單元?jiǎng)t在組態(tài)設(shè)計(jì)時(shí)將可棄舍該單元,需要數(shù)字信號(hào)處理單元才放入該單元,透過逐項(xiàng)的權(quán)衡增減,有可能降低整體「技術(shù)授權(quán)費(fèi)/量產(chǎn)權(quán)利金」成本。即便不能減少「技術(shù)授權(quán)費(fèi)/量產(chǎn)權(quán)利金」成本,電路面積也可以獲得精省,進(jìn)而讓芯片投產(chǎn)成本得到精省(與前述的第一項(xiàng)動(dòng)機(jī)相近)。

5.針對(duì)SoC的應(yīng)用進(jìn)行最佳化

SoC的應(yīng)用非常多,有的是數(shù)字相機(jī)(DSC)的SoC,有的是可攜式媒體播放器(PMP)的SoC,或是導(dǎo)航機(jī)(PND)的SoC,不同的SoC其應(yīng)用設(shè)計(jì)也不同,例如DSC SoC不重視音訊處理,而PND SoC只專注靜態(tài)視訊處理及簡(jiǎn)易的音訊處理,但卻需要重視數(shù)字信號(hào)的處理(接收衛(wèi)星定位信號(hào)后的相關(guān)處理),至于PMP、STB(視訊機(jī)上盒)則重視動(dòng)態(tài)、高質(zhì)量的音/視訊處理,也重視信號(hào)處理(接收、處理節(jié)目信號(hào))。

由上可知,不同的執(zhí)行處理特性、不同的運(yùn)算負(fù)荷度,若用單一架構(gòu)處理器IP則難以滿足設(shè)計(jì),而可組態(tài)性處理器IP卻可以針對(duì)不同的應(yīng)用需求來進(jìn)行組態(tài),以合乎各種應(yīng)用取向的SoC設(shè)計(jì)。

可組態(tài)性處理器IP的隱憂

雖可組態(tài)性處理器IP有如上的5種優(yōu)點(diǎn),但也不表示沒有缺點(diǎn),事實(shí)上,隨半導(dǎo)體技術(shù)及市場(chǎng)演化,可組態(tài)性處理器也面臨一些隱憂、威脅,以下我們簡(jiǎn)要討論。

1.工藝持續(xù)縮密,芯片面積資源獲得寬解

芯片的縮密工藝技術(shù)仍持續(xù)精進(jìn),從90nm、65nm、到45nm,并持續(xù)往下探,使芯片電路面積成本愈來愈低,因此芯片設(shè)計(jì)者已不如過往般重視面積成本,事實(shí)上處理器的多核化發(fā)展,無論是同質(zhì)多核、異質(zhì)多核,都表示「透過電路面積倍增的作法來爭(zhēng)取效能提升」已屬可行、值得。如此,透過組態(tài)作法讓執(zhí)行核心的面積最佳化,此種需求將逐漸減少。

2.芯片上市的時(shí)間壓力愈來愈大

使用IP為的就是要節(jié)省芯片設(shè)計(jì)的驗(yàn)證心力、加速芯片的開發(fā),讓芯片更早上市銷售,而今市場(chǎng)競(jìng)爭(zhēng)更加激烈,芯片Time To Market壓力比過去更大,使許多SoC項(xiàng)目都舍棄從Soft IP階段開始設(shè)計(jì),直接取用Hard IP加速設(shè)計(jì)。

然而可組態(tài)性處理器IP可說是比Soft IP更Soft(軟)性的IP,是從「比Soft IP」更前期的設(shè)計(jì)階段開始著手,好處是獲得更高的設(shè)計(jì)彈性,但相對(duì)的就是增加SoC的設(shè)計(jì)時(shí)間,甚至為實(shí)現(xiàn)組態(tài)化而必須學(xué)習(xí)、熟悉另一套前期設(shè)計(jì)工具,即處理器的組態(tài)工具。

3.軟件風(fēng)險(xiǎn)

此點(diǎn)前面已約略提及,事實(shí)上,除有軟件移植性、兼容互通性等疑慮,軟件的后續(xù)維護(hù)也將令人擔(dān)憂,同時(shí)協(xié)力業(yè)者提供的宏程序(Macro)也可能無法立即適用,這些都須再行斟酌、調(diào)修。特別是軟件開發(fā)、維護(hù)成本在整體SoC方案中所占的比重愈來愈高,許多原有以硬件電路方式設(shè)計(jì)成的功效,而今多半轉(zhuǎn)成軟件方式實(shí)現(xiàn)。

4.固定組態(tài)處理器IP的轉(zhuǎn)向

ARM、MIPS等皆是以固定組態(tài)性處理器IP為主,不過為因應(yīng)客戶需求也開始有些轉(zhuǎn)變,或允許部分的特例,例如MIPS的Pro系列IP就擁有組態(tài)性,或如ARM的OptimoDE Data Engines能因應(yīng)不同需求的應(yīng)用設(shè)計(jì)。

附注1:ARM、MIPS在處理器IP的主要授權(quán)業(yè)務(wù)逐漸成熟后,也開始進(jìn)行相關(guān)延伸,如ARM延伸至實(shí)體IP領(lǐng)域,MIPS延伸到模擬/混訊IP領(lǐng)域,此外兩家業(yè)者皆開始跨入32位的控制器IP市場(chǎng)。

附注2:除了Soft IP、Hard IP外也有Firm IP,F(xiàn)irm IP的設(shè)計(jì)完成度介于前兩者之間,不過在產(chǎn)業(yè)的實(shí)際運(yùn)用中卻不如前兩者普遍。

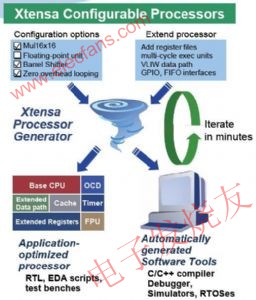

圖 Tensilica Xtensa系列可組態(tài)性處理器IP的組態(tài)設(shè)計(jì)示意圖,左上是勾核需求的功效項(xiàng)、特性項(xiàng),例如需不需要硬件乘法器、桶式移位器等,右上則是延伸處理器架構(gòu),例如增加緩存器、增加VLIW數(shù)據(jù)路徑等,左下則進(jìn)行設(shè)計(jì)應(yīng)用最佳化,右下則是軟件自動(dòng)化產(chǎn)生工具。