美國(guó)國(guó)家儀器公司Ryan Verret

自從1997年基于FPGA的可重配置I/O(RIO)產(chǎn)品在NIWeek圖形化系統(tǒng)設(shè)計(jì)會(huì)議上首次亮相以來(lái),NI已發(fā)布了多種基于NI RIO技術(shù)的設(shè)備,包括NI R系列、CompactRIO以及PXI Express RIO 中頻收發(fā)器。RIO技術(shù)不僅用于控制應(yīng)用,強(qiáng)大的FPGA功能大大提高了測(cè)試吞吐量,使新的測(cè)試成為可能,從而增強(qiáng)了自動(dòng)化測(cè)試系統(tǒng)。同時(shí),現(xiàn)成可用的商業(yè)硬件平臺(tái)以及LabVIEW為FPGA編程帶來(lái)的簡(jiǎn)化,也大大降低了系統(tǒng)開(kāi)發(fā)難度和成本。

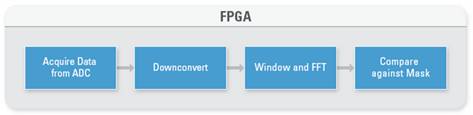

圖1:基于高性能FPGA可以實(shí)現(xiàn)高帶寬實(shí)時(shí)頻譜分析儀等強(qiáng)大測(cè)試儀器。

自動(dòng)化測(cè)試應(yīng)用中的FPGA

開(kāi)放式的用戶(hù)可編程FPGA可以用于解決全新的應(yīng)用挑戰(zhàn)。在FPGA測(cè)試技術(shù)的關(guān)鍵應(yīng)用領(lǐng)域閉環(huán)測(cè)試系統(tǒng)中,測(cè)試系統(tǒng)必須向被測(cè)設(shè)備(DUT)提供實(shí)時(shí)反饋,來(lái)模擬真實(shí)世界的狀態(tài)變化,而這就需要使用具有硬件級(jí)響應(yīng)速度的基于FPGA的設(shè)備。以RFID標(biāo)簽測(cè)試為例,其測(cè)試系統(tǒng)必須模擬RFID讀卡器,以不超過(guò)25 μs的延遲與標(biāo)簽進(jìn)行協(xié)議交互。有些自動(dòng)化測(cè)試系統(tǒng)要求極高的數(shù)據(jù)處理能力,這也是FPGA的全新應(yīng)用領(lǐng)域。寬帶實(shí)時(shí)頻譜分析儀需要對(duì)采集到的數(shù)據(jù)進(jìn)行連續(xù)傅立葉變換(FFT),如圖1所示,只有通過(guò)FPGA對(duì)信號(hào)進(jìn)行協(xié)處理才能滿(mǎn)足這些用戶(hù)自定義分析需求的吞吐量。

除了用于閉環(huán)實(shí)時(shí)測(cè)試系統(tǒng)的高速響應(yīng)和增強(qiáng)測(cè)試系統(tǒng)的信號(hào)處理能力,通過(guò)FPGA還可以實(shí)現(xiàn)自定義的協(xié)議接口、自定義的觸發(fā)控制等功能,從而可以進(jìn)一步提升現(xiàn)有自動(dòng)化測(cè)試系統(tǒng)功能。

表1:三種基于PXI Express的NI FlexRIO FPGA模塊參數(shù)

基于PXI Express的NI FlexRIO FPGA模塊和適配器模塊

最新基于PXI Express的NI FlexRIO FPGA模塊利用更強(qiáng)大的FPGA、更大的板載內(nèi)存、增強(qiáng)的同步特性和高性能的數(shù)據(jù)吞吐量,進(jìn)一步延伸了自動(dòng)化測(cè)試系統(tǒng)的功能極限。

NI最新發(fā)布了基于PXI Express的NI FlexRIO FPGA模塊——NI PXIe-7961R、NI PXIe-7962R、NI PXIe-7965R。三款NI FlexRIO FPGA模塊集成了針對(duì)數(shù)字信號(hào)處理應(yīng)用的高性能Xilinx Virtex-5 SXT FPGA與高達(dá)512 MB的板載DRAM,詳細(xì)信息見(jiàn)表1。您可以將它們作為獨(dú)立協(xié)處理器使用,將計(jì)算負(fù)荷從主處理器移到FPGA上,在主處理器和FPGA之前平衡運(yùn)算負(fù)擔(dān),從而取得更優(yōu)的系統(tǒng)性能。NI同時(shí)還發(fā)布了多個(gè)NI FlexRIO適配器模塊,為FPGA提供了靈活的I/O。NI FlexRIO FPGA模塊的用戶(hù)可以結(jié)合使用這些提供了高性能模擬或數(shù)字I/O的適配器模塊,創(chuàng)建基于FPGA的儀器。

圖2:全新的基于PXI Express的NI FlexRIO FPGA模塊可以與例如NI 5781基帶收發(fā)器等I/O適配器模塊進(jìn)行交互。

Xilinx SXT FPGA整合了高達(dá)640個(gè)DSP slice,可以用于實(shí)現(xiàn)數(shù)字濾波器、定制信號(hào)處理和FFT邏輯等常見(jiàn)功能。作為FPGA的處理性能的補(bǔ)充,板載DRAM提供了較之于現(xiàn)有的NI PXI-795xR系列NI FlexRIO FPGA模塊兩倍帶寬和四倍容量,將DRAM吞吐量提高到3.2 GB/s,使得結(jié)合使用高性能適配器模塊對(duì)大數(shù)據(jù)量進(jìn)行操作成為可能。

這三款NI PXIe-796xR設(shè)備不僅是使用PXI Express技術(shù)的首批FlexRIO FPGA模塊,同時(shí)還集成了全新NI-STC3 ASIC,能夠在多個(gè)FPGA模塊之間或是在基于PXI Express的數(shù)字化儀和FPGA模塊之間直接進(jìn)行數(shù)據(jù)流傳送(亦稱(chēng)作點(diǎn)對(duì)點(diǎn)數(shù)據(jù)流)。這一功能可避免將大量數(shù)據(jù)先傳送回主處理器,再傳給目標(biāo)板卡,從而可以幫助用戶(hù)利用高性能NI數(shù)字化儀建立基于FPGA的儀器。將設(shè)備與NI PXIe-5122數(shù)字化儀一起使用,可以將兩個(gè)通道,以100 MS/s全采樣速率或400 MS/s總采樣速率傳送到PXI Express NI FlexRIO FPGA中。您還可以將NI PXIe-5622中頻(IF)數(shù)字化儀或NI PXIe-5663矢量信號(hào)分析儀的數(shù)據(jù),以最大75 MS/s的I/Q速率或300 MS/s的總速率傳送到NI FlexRIO FPGA模塊進(jìn)行處理。對(duì)于大多數(shù)計(jì)算要求高的應(yīng)用而言,您可以將運(yùn)算量平均到多個(gè)FPGA上,以超過(guò)800 MB/s的速率從一個(gè)FPGA傳送到另一個(gè)FPGA,或是以每個(gè)方向700 MB/s的速率雙向(總模塊吞吐量超過(guò)1.4 GB/s)進(jìn)行點(diǎn)對(duì)點(diǎn)數(shù)據(jù)傳輸。

表2:NI和NI聯(lián)盟合作伙伴提供了多個(gè)全新的NI FlexRIO適配器模塊。

全新的高性能NI FlexRIO FPGA和適配器模塊將幫助有測(cè)試和產(chǎn)品驗(yàn)證需求的工程師和研究人員輕松構(gòu)建基于FPGA的系統(tǒng),快速有效地實(shí)現(xiàn)復(fù)雜的自定義儀器設(shè)備。

作者信息: Ryan Verret,NI信號(hào)發(fā)生器和FPGA測(cè)試產(chǎn)品的產(chǎn)品經(jīng)理,獲得了美國(guó)萊斯大學(xué)的電氣工程學(xué)士學(xué)位和碩士學(xué)位。